Summary of Contents for iWave Zynq-7000 SoC

- Page 1 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Zynq-7000 SoC SODIMM Development Platform Hardware User Guide REL1.0 iWave Systems Technologies Pvt. Ltd. Page 1 of 58...

- Page 2 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Document Revision History Document Number iW-PRFOZ-UM-02-R1.0-REL1.0-Hardware-Zynq-7000-DevKit Revision Date Change Description Oct 2018 Initial Release Version PROPRIETARY NOTICE: This document contains proprietary material for the sole use of the intended recipient(s). Do not read this document if you are not the intended recipient. Any review, use, distribution or disclosure by others is strictly prohibited.

- Page 3 (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

-

Page 4: Table Of Contents

Mechanical Characteristics ..........................55 3.3.1 SODIMM Carrier Board Mechanical Dimensions ..................55 3.3.2 Guidelines to insert the Zynq-7000 SoC SODIMM SOM into Carrier Board ..........56 3.3.3 Guidelines to remove the Zynq-7000 SoC SODIMM SOM from Carrier board ..........56 ORDERING INFORMATION .......................... - Page 5 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide List of Figures Figure 1: Zynq-7000 SoC SODIMM Carrier Board Block Diagram ..................8 Figure 2: SODIMM Edge Connector ..........................10 Figure 3: Debug UART ..............................25 Figure 4: Gigabit Ethernet Connector ..........................26 Figure 5: USB OTG Connector ............................

-

Page 6: Introduction

Carrier board for complete validation of Zynq-7000 SoC functionality. This document is the Hardware User Guide for the Zynq-7000 SoC SODIMM Carrier Board and provides detailed information on the overall design & usage of the Carrier Board from a Hardware Systems perspective. The details about the Zynq-7000 SoC SODIMM SOM hardware is explained in Zynq-7000 SoC SODIMM SOM hardware user guide document. -

Page 7: References

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Terminology Description In this document, wherever Signal Type is mentioned, below terminology is used. Table 2: Terminology Terminology Description Input Signal Output Signal Bidirectional Input/output Signal CMOS Complementary Metal Oxide Semiconductor Signal... -

Page 8: Architecture And Design

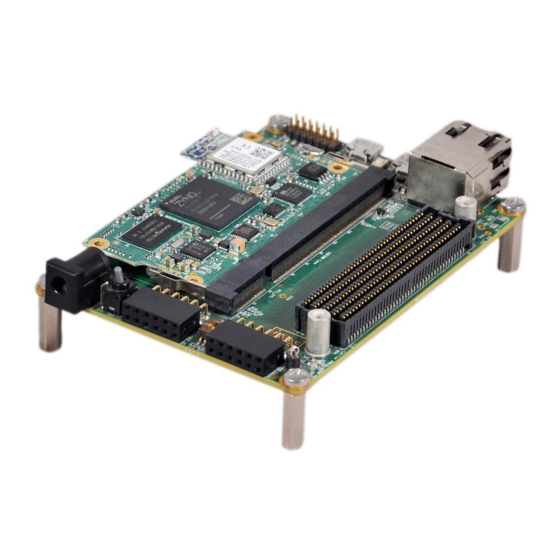

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide 2. ARCHITECTURE AND DESIGN This section provides detailed information about the Zynq-7000 SoC SODIMM Development platform carrier board features with high level block diagram and detailed information about each block. Zynq SODIMM Carrier Board Block Diagram iW-RainboW-G28D –... -

Page 9: Zynq-7000 Soc Sodimm Carrier Board Features

: 100mm X 72mm Note: In Zynq-7000 SoC, PL Bank13 is not available in Z-7007S and Z-7010 devices and so Bank13 IOs (20 SE IOs) on FMC connector & Pmod connector1 is NC in Z-7007S and Z-7010 SoC based SODIMM DevKit. -

Page 10: Sodimm Connector

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Connector The Zynq-7000 SoC SODIMM Carrier board supports 200 Pin SODIMM Edge mating connector for SODIMM SOM attachment. This standard 200-pin robust connector is capable of handling high-speed serialized signals and can be used for size constrained embedded applications. -

Page 11: Table 3: Sodimm Edge Connector Pin Out

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Table 3: SODIMM Edge Connector Pin Out SODIMM Edge Connector Signal Type/ Description Pin Name Termination Power Ground. GPHY_ATXRXM IO, DIFF Ethernet transmit differential pair 0 negative. This pin is connected to RJ45 Magjack. - Page 12 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L22P_T3_13 IO, 3.3V LVCMOS Bank13 User I/O Single ended pin. This pin is connected to K10 pin of FMC connector (J1). PL_IO_L15P_T2_DQS_13 IO, 3.3V LVCMOS Bank13 User I/O Single ended pin.

- Page 13 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L1P_T0_34 IO, 3.3V LVCMOS Bank34 User I/O Single ended pin. This pin is connected to H7 pin of FMC connector (J1). PL_IO_L2P_T0_34 IO, 3.3V LVCMOS Bank34 User I/O Single ended pin.

- Page 14 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L13N_T2_MRCC_13 IO, 3.3V LVCMOS Bank13 User I/O Single ended pin. This pin is connected to F5 pin of FMC connector (J1). PL_IO_L14N_T2_SRCC_13 IO, 3.3V LVCMOS Bank13 User I/O Single ended pin.

- Page 15 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L11N_T1_SRCC_34 O, 3.3V CMOS Bank34 Clock user Single region negative Single ended pin. This pin is connected to G3 pin of FMC connector (J1).

- Page 16 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination USB_OTG_ID O, 3.3V CMOS USB OTG ID input for USB host or device detection. This pin is connected from Micro USB OTG connector (J4).

- Page 17 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L12N_T1_MRCC_34 O, 3.3V LVCMOS Bank34 Clock user Multi region negative Single ended pin. This pin is connected to H5 pin of FMC connector (J1).

- Page 18 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination SD0_CD(PS_MIO48_501) O, 1.8V LVCMOS/ SD0 Card Detect pin. This pin is connected from Micro SD connector for card detection. VIN_3V3 O, 3.3V Power Supply Voltage.

- Page 19 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L14P_T2_SRCC_34 IO, 3.3V LVCMOS Bank34 Clock user Single region positive Single ended pin. This pin is connected to D20 pin of FMC connector (J1).

- Page 20 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L24P_T3_AD15P_35 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. This pin is connected to G33 pin of FMC connector (J1). PL_IO_L21N_T3_DQS_AD1 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin.

- Page 21 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L6N_T0_VREF_35 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. This pin is connected to 3 pin of Pmod connector1 (J3). Note: Optionally this pin is connected to K20 of FMC connector (J1) through resistor and default not populated.

- Page 22 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L18N_T2_AD13N_3 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. This pin is connected to C23 pin of FMC connector (J1). PL_IO_L20N_T3_AD6N_35 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin.

- Page 23 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination PL_IO_L3N_T0_DQS_AD1N IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. This pin is connected to G31 pin of FMC connector (J1). PL_IO_L4N_T0_35 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin.

- Page 24 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide SODIMM Edge Connector Signal Type/ Description Pin Name Termination JTAG_TDI O, 3.3V CMOS JTAG Test Data Input. This pin is connected to 10 pin of JTAG connector (J8). PL_IO_L2P_T0_AD8P_35 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin.

-

Page 25: Serial Interface Features

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Serial Interface Features 2.4.1 Debug UART The Zynq SODIMM Carrier Board supports debug interface through Zynq 7000 CPU’s UART0 interface. This UART0 signals from SODIMM Edge connector is connected to UART to USB Convertor “FT232RQ-REEL” and to USB Micro AB Connector (J6). -

Page 26: Communication Features

The Zynq-7000 SoC SODIMM Carrier board supports 10/100/1000Mbps Ethernet interface through ENET0 interface of Zynq-7000 SoC PS. Ethernet PHY output signals from SODIMM Edge connector is directly connected to RJ45 Magjack (J2). The Ethernet supports Speed (Yellow) and Link/Activity (Green) LED indications on RJ45 Magjack connector. -

Page 27: Usb 2.0 Otg Port

The Zynq-7000 SoC SODIMM carrier Board supports USB2.0 High Speed OTG interface through USB OTG Controller of Zynq-7000 SoC PS. The Transceiver output signals from SODIMM Edge connector is directly connected to USB2.0 MicroAB connector. This port can be used as USB OTG functionality which supports USB host and USB device based on USB ID pin status. -

Page 28: Microsd Port

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide 2.5.3 MicroSD Port The Zynq-7000 SoC SODIMM Carrier Board supports SDIO interface through SD0 interface of Zynq-7000 SoC PS. This SD0 signals from SODIMM Edge connector is connected to Micro SD connector (J11) to support Micro SD storage. -

Page 29: Expasnion Connectors

Upto four clock capable SE IOs (two MRCC and two SRCC) Note: In Zynq-7000 SoC, PL BANK13 is not available in Z-7007S and Z-7010 devices and so BANK13 IOs (20 SE IOs) on FMC connector is NC in Z-7007S and Z-7010 SoC based SODIMM DevKit. -

Page 30: Figure 8: Fmc Hpc Connector Pin Out

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Figure 8: FMC HPC Connector Pin Out REL1.0 iWave Systems Technologies Pvt. Ltd. Page 30 of 58... -

Page 31: Table 5: Fmc Hpc Connector Pin Out

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Table 5: FMC HPC Connector Pin Out FMC Connector Signal Type/ Signal Name Description Pin Name Termination Power Ground. DP1_M2C_P DP1_M2C_N Power Ground. Power Ground. DP2_M2C_P DP2_M2C_N Power Ground. Power Ground. DP3_M2C_P... - Page 32 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination RES1 Power Ground. Power Ground. DP9_M2C_P DP9_M2C_N Power Ground. Power Ground. DP8_M2C_P DP8_M2C_N Power Ground. Power Ground. DP7_M2C_P DP7_M2C_N Power Ground. Power Ground.

- Page 33 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination DP0_C2M_N Power Ground. Power Ground. DP0_M2C_P DP0_M2C_N Power Ground. Power Ground. LA06_P PL_IO_L7P_T1_34 IO, 3.3V LVCMOS Bank34 User I/O Single ended pin.

- Page 34 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination LA27_N PL_IO_L1N_T0_AD0 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin N_35 This pin is connected from 189 pin of SODIMM Connector (J7).

- Page 35 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination Power Ground. LA05_P PL_IO_L5P_T0_34 IO, 3.3V LVCMOS Bank34 User I/O Single ended pin. This pin is connected from 97 pin of SODIMM Connector (J7).

- Page 36 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination JTAG_TCK O, 3.3V LVCMOS JTAG Test Clock. JTAG_TDI I, 3.3V LVCMOS JTAG Test Data Input JTAG_TDO O, 3.3V LVCMOS JTAG Test Data Output...

- Page 37 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination HA13_N Note: Optionally this pin is connected from 7 pin of SODIMM Connector (J7) through resistor default populated. Power Ground. HA16_P Note: Optionally this pin is connected...

- Page 38 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination VADJ VCC_3V3 O, 3.3V Power FMC Adjustable Voltage. Power Ground. PG_M2C PG_M2C O,3.3V/ Power Good Signal from FMC Module 10K PU to Carrier.

- Page 39 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination HA15_N Note: Optionally this pin is connected from 123 pin of SODIMM Connector (J7) through resistor and default not populated. Power Ground.

- Page 40 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination LA00_P_CC E_PL_IO_L10P_T1_A IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. D11P_35 This pin is connected from 154 pin of SODIMM Connector (J7).

- Page 41 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination LA22_P E_PL_IO_L9P_T1_DQ IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. S_AD3P_35 This pin is connected from 148 pin of SODIMM Connector (J7).

- Page 42 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination CLK0_M2C_P PL_IO_L12P_T1_MR I, 3.3V LVDS Bank34 User I/O Single ended pin. CC_34 This pin is connected from 90 pin of SODIMM Connector (J7).

- Page 43 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination LA19_P PL_IO_L22P_T3_AD7 IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. P_35 This pin is connected from 138 pin of SODIMM Connector (J7).

- Page 44 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination Power Ground. CLK1_C2M_P PL_IO_L12P_T1_MR IO, 3.3V LVCMOS Bank35 User I/O Single ended pin. CC_35 This pin is connected from 136 pin of SODIMM Connector (J7).

- Page 45 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination HA18_P Note: Optionally this pin is connected from 161 pin of SODIMM Connector (J7) through resistor and default not populated. HA18_N Note: Optionally this pin is connected...

- Page 46 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination HA02_P PL_IO_L20P_T3_13 IO, 3.3V LVCMOS Bank13 User I/O Single ended pin. This pin is connected from 29 pin of SODIMM Connector (J7).

- Page 47 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide FMC Connector Signal Type/ Signal Name Description Pin Name Termination HB00_N_CC Power Ground. HB06_P_CC HB06_N_CC Power Ground. HB10_P HB10_N Power Ground. HB14_P HB14_N Power Ground. HB17_P_CC HB17_N_CC Power Ground. VIO_B_M2C REL1.0 iWave Systems Technologies Pvt. Ltd.

-

Page 48: Pmod Host Port Connectors

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide 2.6.2 Pmod Host Port Connectors The Zynq-7000 SoC SODIMM Carrier board supports two 12pin Pmod host port connector for plugging Pmod modules. Pmod interface or Peripheral Module interface is a standard defined by Digilent Inc in the Digilent Pmod Interface Specification for peripherals used with FPGAs or microcontrollers. -

Page 49: Table 6: Pmod Connector1 Pin Out

O, 3.3V Power 3V3 Supply Voltage. Note: If IO voltage of PL Bank34 and Bank35 is changed in Zynq-7000 SoC SODIMM SOM, then the IO voltage of corresponding PL Bank IOs in this Pmod connector1 will also change. Note: In Zynq-7000 SoC, PL Bank13 is not available in Z-7007S & Z-7010 devices and so Bank13 IOs on Pmod Connector1 pin2 is NC in Z-7007S &... -

Page 50: Additional Features

Additional Features 2.7.1 JTAG Connector A Standard Xilinx 14-pin JTAG Header is available in Zynq-7000 SoC SODIMM carrier board for debug purpose. JTAG signals from SODIMM connector is directly connected to JTAG Header (J8) and same JTAG signals are also connected to FMC connector. -

Page 51: Power On/Off Switch

Figure 11: Power On/Off Switch 2.7.3 Reset Switch The Zynq-7000 SoC SODIMM carrier board supports Push button switch (SW1) to reset the Zynq 7000 SoC CPU. Reset signal of SODIMM edge connector Pin 187 is directly connected from Reset Push button switch. This Reset Push button switch (SW1) is physically located at the top of the board as shown below. -

Page 52: Rtc Coin Cell Holder

2.7.4 RTC Coin Cell Holder The Zynq-7000 SoC SODIMM carrier board supports Coin Cell Holder to connect “2032” series 3V coin cell. This coin cell voltage is connected to SODIMM SOM for RTC back up voltage when VCC main power is off. This Coin Cell Holder (J12) is physically located at the bottom of the board as shown below. -

Page 53: Technical Specification

Max Input Ripple VCC_5V 4.75V 5.25V ±50mV VRTC_3V0¹ 2.8V 3.3V ±20mV ¹ The Zynq-7000 SoC SODIMM DevKit uses this voltage as backup power source to RTC controller when VCC is off. REL1.0 iWave Systems Technologies Pvt. Ltd. Page 53 of 58... -

Page 54: Environmental Characteristics

3.2.3 Electrostatic Discharge iWave’s Zynq-7000 SoC SODIMM Development platform is sensitive to electro static discharge and so high voltages caused by static electricity could damage some of the devices on board. It is packed with necessary protection while shipping. -

Page 55: Mechanical Characteristics

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide Mechanical Characteristics 3.3.1 SODIMM Carrier Board Mechanical Dimensions The SODIMM carrier board PCB form factor is 100mm x 72mm and Board mechanical dimension is shown below. Figure 15: SODIMM carrier board Mechanical dimension – Top View The SODIMM carrier board PCB thickness is 1.55mm±0.1mm, top side maximum height component is Ethernet... -

Page 56: Guidelines To Insert The Zynq-7000 Soc Sodimm Som Into Carrier Board

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide 3.3.2 Guidelines to insert the Zynq-7000 SoC SODIMM SOM into Carrier Board • Make sure that power is not provided to the SODIMM carrier board. • Insert the SOM module into the socket at a slight angle (approximately 30 degrees) as shown in the below illustration (A). -

Page 57: Ordering Information

Zynq-7000 SoC SODIMM Development Platform Hardware User Guide 4. ORDERING INFORMATION The below table provides the standard orderable part numbers for Zynq-7000 SoC SODIMM Development platform which includes Zynq-7000 SoC SODIMM SOM and SODIMM carrier board. Table 11: Orderable Product Part Numbers... - Page 58 Zynq-7000 SoC SODIMM Development Platform Hardware User Guide REL1.0 iWave Systems Technologies Pvt. Ltd. Page 58 of 58...

Need help?

Do you have a question about the Zynq-7000 SoC and is the answer not in the manual?

Questions and answers