Advertisement

Quick Links

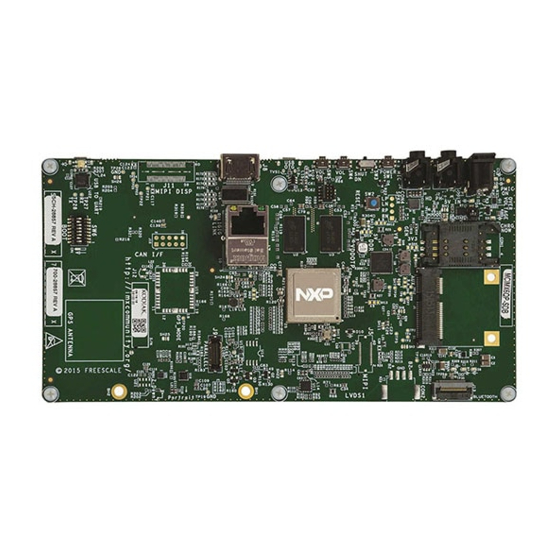

NXP Semiconductors

Chip Errata

Chip Errata for

the i.MX 6Dual/6Quad and

i.MX 6DualPlus/6QuadPlus

This document details the silicon errata known at the time of publication for the i.MX 6Dual/6Quad and

i.MX 6DualPlus/6QuadPlus multimedia applications processors.

Table 2

provides a revision history for this document.

Table 3

contains a summary of the silicon errata. Bolded rows are specific to either i.MX 6Dual/6Quad or

i.MX 6DualPlus/6QuadPlus (see the errata description column).

Table 4

lists the ARM errata excluded from detailed description in this document.

To identify the silicon revision, refer to the last letter of the part number. See

For additional information, see either the i.MX 6Dual/6Quad Applications Processor Reference Manual

(IMX6DQRM) or the i.MX 6DualPlus/6QuadPlus Applications Processor Reference Manual

(IMX6DQPRM).

© 2012-2016 NXP B.V.

Table 1. Part number/silicon revision examples

Example Part Numbers

MCIMX6Q6AVT10AC

MCIMX6D6AVT10AD

MCIMX6QP6AVT1AA

MCIMX6DP6AVT1AA

Silicon Revision

i.MX 6Quad, Revision 1.2

i.MX 6Dual, Revision 1.3

i.MX 6QuadPlus, Revision 1.0

i.MX 6DualPlus, Revision 1.0

IMX6DQCE

Rev. 6.1, 06/2016

Table 1

for examples.

Advertisement

Subscribe to Our Youtube Channel

Summary of Contents for NXP Semiconductors i.MX 6Dual

- Page 1 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus This document details the silicon errata known at the time of publication for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus multimedia applications processors. Table 2 provides a revision history for this document.

- Page 2 (additional) necessary actions to prevent the occurrence or impact of each erratum. Go through your support channel if you have any questions or concerns. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

-

Page 3: Chip Errata For The I.mx 6Dual/6Quad And I.mx 6Dualplus/6Quadplus, Rev. 6.1, 06/2016 Nxp Semiconductors

ARM. Rev. 3 11/2013 • Added the following: ERR007005, ERR007006, ERR007007, ERR007008, ER007117, ER007220, ERR007265, ERR007266 • Updated the following: ERR003740, ERR003742, ERR003778, ERR004512 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors... - Page 4 Table 2. Document Revision History (continued) Rev. Date Substantive Changes Number Rev. 2 5/2013 • Deleted ERR003775—Addressed in rev. 1 of the i.MX 6Dual/6Quad Applications Processor Reference Manual (IMX6DQRM). • Added the following errata: – ERR006282 – ERR006308 – ERR006358 – ERR006687 •...

- Page 5 UNDEFINED exception instead of being treated as NOP ERR003738 ARM/MP: 751475—Parity error may not be reported on full cache line access No fix scheduled (eviction / coherent data transfer / cp15 clean operations) Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 6 ARM/MP: 782774—A spurious event 0x63, “STREX passed,” can be reported on an No fix scheduled LDREX that is preceded by a write to Strongly Ordered memory region Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 7 In master mode, burst lengths of 32n+1 will transmit incorrect data No fix scheduled ERR009606 ERR004446 EIM: AUS mode is nonfunctional for devices larger than 32 MB No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 8 HDMI: 9000440660—Audio DMA fails to stop after ERROR detection No fix scheduled ERR004308 HDMI: 8000504668—The arithmetic unit may get wrong video timing values although No fix scheduled the FC_* registers hold correct values Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 9 ERR005197 MIPI: Null and Blanking data packets activate ‘dvalid’ signal No fix scheduled ERR009704 MIPI: CSI-2: CRC error produced in 4-lane configuration No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 10 PCIe: 9000493959—L1 ASPM incorrectly entered after link down event during L1 No fix scheduled ASPM entry negotiation ERR004321 PCIe: 9000470913—Power Management Control: Core might enter L0s/L1 before No fix scheduled Retry buffer is empty Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 11 1.3. ERR007220 ROM: NAND boot may fail due to incorrect Hamming Checking implementation in the Fixed in silicon ROM code [i.MX 6Dual/6Quad Only] revision 1.3 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 12 ROM: Incorrect NAND BAD Block Management [i.MX 6Dual/6Quad Only] No fix scheduled ERR009678 ROM: SD/EMMC/NAND prematurely times out during boot [i.MX 6Dual/6Quad Only] No fix scheduled SATA ERR003761 SATA: 9000433864—COMRESET and COMWAKE do not always contain six bursts No fix scheduled ERR003762 SATA: 9000450053—In SDB FIS with N-bit set, non-matching PMP field is not...

- Page 13 WDOG: WDOG SRS bit requires to be written twice No fix scheduled XTAL ERR005777 XTAL: In some cases, the 24 MHz oscillator start-up is slow or may fail to start No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 14 Freescale Linux BSP for impacted devices. OS vendors/users must approach ARM if further information is required. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 15 DSM, and then, revert to the normal bypass mode, when exiting from DSM. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

-

Page 16: Value

2. Modify the comparator value to set it to a higher value 3. Clear the Global Timer flag 4. Clear the Pending Status information for Interrupt 27 (Global Timer interrupt) in the Distributor of the Interrupt Controller. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors... -

Page 17: Nxp Semiconductors

ARM should be followed. Due to limitations of this timer specifically in low power mode operation we do not recommend the use of this ARM Global timer. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors... - Page 18 Diagnostic Control register, placed in CP15 c15 0 c0 1. The bit can be written in Secure state only, with the following Read/Modify/Write code sequence: Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

-

Page 19: Chip Errata For The I.mx 6Dual/6Quad And I.mx 6Dualplus/6Quadplus, Rev. 6.1, 06/2016 Nxp Semiconductors

Setting this bit has no visible impact on the overall performance or power consumption of the processor. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase (UBOOT) starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors... - Page 20 Software workaround is not needed because this erratum will not be encountered in normal device operation. The Freescale Linux BSP does not support this optional profiling feature. Users may add Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 21 ERR003719 support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 22 When it is set, this bit prevents CP15 maintenance operations to be interrupted. Using this software workaround is not expected to cause any visible impact on the system. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 23 ERR003720 Linux BSP Status: Software workaround implemented in Linux BSP codebase (UBOOT) starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 24 Software workaround not needed in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Linux BSP keeps ACTRL[2:1]=2’b00. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 25 The Linux BSP does not use this debug feature—the ARM workaround should be followed. Software workaround is not needed because this erratum will not be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 26 Change Translation Table Base Register Change ASID to new value the sequence: Change Translation Table Base Register to the global-only mappings Change ASID to new value Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 27 Change Translation Table Base Register to new value Set TTBCR.PD0 = 0 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 28 Freescale Linux BSP does not support this optional profiling feature. Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 29 0xD00, and not at any of its alias addresses. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not needed because this erratum will not be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 30 “live” registers [VFP, CP15, etc.]) Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not needed because this erratum will not be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 31 ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 32 Workarounds: No workaround is possible to achieve the required functionality of counting how many instructions are precisely passing through the register rename pipeline stage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 33 ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 34 Setting this bit causes all PLD instructions to be treated as NOPs, with the consequence that code sequences usually using the PLDs, such as the memcpy() routine, might suffer from a visible performance drop. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 35 Users should check their custom OS and either avoid the code sequence or apply the ARM recommended workaround. The ARM recommended workaround does have a performance impact. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 36 Linux BSP Status: The BSP uses correct MMU settings and does not present conditions that can cause an imprecise external abort. BSP has exception handlers for such aborts. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 37 The debugger tools can find the expected PC value and instruction state by reading the DBGPCSR register, and consider it as described in the Description section. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 38 Software workaround not applicable to the BSP since it is a debug feature. Users should use the ARM recommended workaround if using this debug feature in their application. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 39 No fix scheduled Linux BSP Status: Software workaround not needed in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 40 Linux BSP Status: No software workaround can be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 41 This ensures visibility of the written data by any external agent. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 42 The BSP does use DMBs however the specific condition or scenario is not seen in kernel code. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 43 Coresight components nDBGRESET is connected to. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not implemented because this erratum will never be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 44 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Software workaround not applicable to the BSP as instruction encodings are not generated by compiler. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 45 Parity is not supported on i.MX 6 series. See erratum ERR005187 regarding the BSP interaction with the parity interrupt. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 46 (aborted) data without entering the Data Abort exception handler as it should normally do. Workarounds: None Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 47 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround which disables the double linefill feature is integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 48 The bit[10] “High Priority for SO and Dev reads enable” of the PL310 Auxiliary Control Register is not enabled in the BSP. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 49 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 50 Users should ensure their tool chain has the recommended workaround. For more information about integrating the workaround inside tool chains, please refer to the Programmer Advice Notice related to this erratum, ARM UAN 0004A. (http://infocenter.arm.com/help/topic/com.arm.doc.uan0004a/UAN0004A_a9_read_read.pdf) Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 51 Note that false sharing on a memory region used for self modifying code is extremely unlikely to exist. As such, the write operation targeting the same cache line than the cache operation occurring Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 52 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 53 Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 54 Software workaround is not implemented because this erratum will never be encountered in normal device operation. Users that require this debug feature should implement the recommended ARM workaround. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 55 The BSP does not dynamically enable/disable data cache during run-time and thus avoids the PLD instruction with the data cache off. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 56 Software workaround is not implemented because this erratum will never be encountered in normal device operation. Users should use ARM recommended workaround if using this debug trace feature. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 57 The BNE might be mispredicted again, so the LDR is speculatively executed again, and the code loops back on the same failing LDREX/STREX sequence. Conditions: The erratum happens in systems which might generate external aborts in answer to cacheable memory requests. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 58 Software workaround implemented in Linux BSP codebase in all releases. Software workaround is to enable branch prediction which is enabled by default in the BSP GA release. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 59 BSP ignores any assertion on the PARITYFAIL[7:6] bits by masking the ARM -GIC parity interrupt 125. Please note that the i.MX6 does not support the parity feature and hence should not be enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 60 • The eviction buffer incorrectly samples the error information and cancels the corresponding eviction Projected Impact: When the above conditions are met, dirty data can be lost, leading to data corruption. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 61 • Disable the logic responsible for generating RAM errors. This can imply disabling parity in PL310 and/or disabling DATAERR and TAGERR generation in the RAM array, depending on the implementation. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 62 GIC parity interrupt 125, is masked in the BSP. The parity feature is disabled by default and should not be enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 63 The i.MX 6Dual/6Quad has PL310-BU-00000-r3p1-50rel0. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 64 Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. BSP software workaround sets prefetch offset to 0 or 15 to avoid this erratum. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 65 Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 66 Linux BSP Status: Software workaround, adding a DSB at the beginning of the abort exception handler) is integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 67 Load-Exclusive or Store-Exclusive instructions. The implementation of this workaround can be restricted to code regions which have access to Strongly Ordered memory. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 68 BSP. Users should check their application and OS to see if errata conditions met and apply recommended ARM work around if applicable. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 69 Interrupts must be temporarily disabled so that no interrupt can be taken between the maintenance operation and the translation entry update. This avoids the possibility of the interrupt service routine bringing the cache line back in the cache. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 70 Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above.The Linux community has not incorporated a workaround for this erratum Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 71 BSP. Users should check their application and OS to see if errata conditions met and apply recommended ARM work around if applicable. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 72 Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 73 When it is set, this bit causes the DMB instruction to be decoded and executed like a DSB. Using this software workaround is not expected to have any impact on the overall performance of the processor on a typical code base. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 74 - Making the processor executing the short loop take regular interrupts. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 75 The BSP has the MMU enabled when it performs BTAC flush in LPM entry. When kernel is running, the MMU is kept enabled until DSM is entered and ARM core power is gated. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 76 ; ensures that all subsequent accesses are observed when gaining of the communication variable has been observed ; loads and stores in the critical region can now be performed MOV r2,#0 MOV r0, #0 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 77 Users should confirm if the conditions apply in their specific OS and apply the ARM recommended workaround if necessary. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 78 However, the workaround is not expected to create any significant performance degradation in most standard applications. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 79 ERR009604 Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release imx_3.14.38_6qp_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 80 In addition, this erratum cannot occur if at least one of the following bits in the Diagnostic Control Register is set to 1: Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 81 - bit [22] – Disable Write Allocate Wait mode Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release imx_3.10.53_1.1.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 82 Software workaround is not implemented because this erratum will never be encountered in normal device operation.The Freescale Linux BSP does not support this optional profiling feature. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 83 Linux BSP Status: Software workaround is not implemented because this erratum will never be encountered in normal device operation, as this erratum is related to a debug feature. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 84 PARITYFAIL [7:6] bits by masking the ARM-GIC parity interrupt 125. Please note that the i.MX6 does not support the parity feature (disabled by default) and hence should not be enabled by users. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 85 CAAM CHANUM register. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 86 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 87 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 88 No fix scheduled Linux BSP Status: Software workaround not needed in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 89 PDNSCR_ISO2SW = PDNSCR_ISO = 1 (counts in IPG_CLK clock domain) Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release GA L3.0.35_1.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 90 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase. A patch is included in both BSP kernels v3.10.9 and v3.0.35. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 91 Please refer to Engineering Bulletin EB821 : LDB Clock Switch Procedure and i.MX6 Asynchronous Clock Switching Guidelines for further details on the issue and recommended software workaround procedure. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 92 ERR009219 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 93 25% drop in read data rates. Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.14.38_6qp_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 94 No fix scheduled. Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 95 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The driver limits the burst length up to 32 bits. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 96 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 97 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not implemented because this erratum will never be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 98 There is no workaround for the throughput limitation. To prevent overrun of the ENET RX FIFO, enable pause frame. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 99 800 bytes. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 100 None. Channels 1, 3, and 4 can be used for the event capture instead. Proposed Solution: No fix scheduled Linux BSP Status: Workaround cannot be implemented to mask this SoC issue, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 101 TDAR bit will restart TxBD processing. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release L3.0.35_4.0.0 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 102 ENET interrupts and GPIO6 SION is set, the resulting GPIO interrupt will wake the system from Wait mode. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release L3.0.35_4.0.0 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 103 ESAI must be reset according to the reset procedure documented in the reference manual. Proposed Solution: No fix scheduled Linux BSP Status: Workaround cannot be implemented to mask this SoC issue, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 104 Use DDR or OCRAM memories when performing exclusive accesses. Proposed Solution: No fix scheduled Linux BSP Status: Workaround cannot be implemented to mask this SoC issue, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 105 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The BSP does not use CSU. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 106 CODE field of the Control/Status word to request an abortion of the transmission. Wait for the corresponding IFLAG to be asserted by polling the IFLAG register or by the Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 107 The first mailbox cannot be used for reception or transmission process. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 108 The Set Feature command cannot be used in Toggle mode. Workarounds: None Proposed Solution: No fix scheduled Linux BSP Status: Workaround cannot be implemented to mask this SoC issue, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 109 GPU2D should not be mistakenly accessed by software when power-gated. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not implemented because this erratum will never be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 110 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 111 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 112 This will not cause a system hang or screen corruption in 3D applications. Workarounds: None Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 113 No workaround at this time. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 114 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 115 This issue happens only when Audio DMA is configured to use unspecified length burst (INCR); however, it is not recommended to use INCR in i.MX 6Dual/6Quad due to poor bus performance (PL301 convert AHB INCR to AXI SINGLE transfers). This issue can be ignored.

- Page 116 Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 117 No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Software workaround has been implemented with HDMI audio driver enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 118 AHB_DMA_CONF0 0x00123600, with bit 0 cleared (“0”) and with the bits 2:1 determining the INCR type. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 119 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 120 The fc_arithlogicunit_div when receive the tmds reset will force theiroutputs to zeros: //Hold division values********************************************************* always @ (posedge itmdsclk or negedge itmdsrstz) begin if (!itmdsrstz) Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 121 No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Software workaround has been implemented with HDMI driver enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

-

Page 122: Start Procedure

— Write 8’h00 to ADDR_AUD_N2 — Write 8’h00 to ADDR_AUD_N1 (starts new DMA operation set the AHB_DMA START bit) — Wait for FIFO full — Program N write to ADDR_AUD_N3 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors... - Page 123 No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Software workaround has been implemented with HDMI driver enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 124 No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Software workaround has been implemented with HDMI driver enabled. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 125 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used.The BSP configures the I2C frequency to 375 kHz by default. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 126 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The BSP ensures that the DDR_INPUT bit is set to CMOS input type. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 127 Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.14.52_1.1.0_ga. The BSP implements the IDMAC burst size workaround. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 128 Apply software reset to MIPI in case the aclk_emi_podf or aclk_emi_sel in the CCM are modified. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 129 Workarounds: None. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 130 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 131 A software workaround is possible but it hasn’t been implemented in the Linux BSP yet. BSP functionality may be affected in some configurations and use cases as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 132 Software workaround integrated in Linux BSP codebase starting in release 3.0.35_1.1.0 GA. The software workaround was integrated in the very first version of the MIPI DSI driver. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 133 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 134 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 135 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The BSP does not support data types from 0x13 to 0x17. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 136 • IPU_CSI0_DI__CSI0_MIPI_DI1 • IPU_CSI0_DI__CSI0_MIPI_DI2 • IPU_CSI0_DI__CSI0_MIPI_DI3 Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 137 3) Ignore the CRC error if you confirm the CRC error is due to the operating conditions described above in the Description. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 138 Software workaround not needed in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The BSP driver does not set the MFE bit to 1 but uses the default value 0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 139 RAM or a non-DDR based external memory. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 140 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used.The Freescale Linux BSP releases leave the ARCR_GUARD bits at the default value of 4'b0000. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 141 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 142 In case of MemRd TLPs, a completion with UR status is issued, but no error bits will be set on the root port. Workarounds: None Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 143 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 144 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 145 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 146 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 147 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 148 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 149 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 150 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 151 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 152 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 153 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 154 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 155 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 156 4. The core will enter the appropriate low power state, even though it still has TLPs in the retry buffer. Projected Impact: Low power states are entered inappropriately. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 157 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 158 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 159 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 160 None. This is an unusual verification setup, and in a real system the remote partner must keep sending TS1 OSs in Recovery.RcvrLock and then the core will move to Recovery after receiving 2 TS1 OSs. Proposed Solution: No fix scheduled Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 161 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 162 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 163 • Release LTSSM to wake-up from L2. • Wait for entry to L0 and then repeat process of entering Gen2 from cold start case (going through Detect). Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 164 6. Negotiate L2 entry/exit (software controlled D3). Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 165 It may be used if there are repeaters on the link. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround is not implemented because this erratum will never be encountered in normal device operation. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 166 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 167 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will not result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 168 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 169 Proposed Solution: No fix scheduled. Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 170 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 171 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 172 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 173 Linux BSP Status: No software workaround can be implemented to mask or workaround this erratum. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 174 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 175 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 176 Linux BSP Status:. Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 177 PCIe reference clock by setting IOMUXC_GPR1[REF_SSP_EN] to 1. Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release L3.10.53_1.1.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 178 No fix scheduled. Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_v2015.04_3.14.52_1.1.0_ga (U-Boot). LDO PU is always on except when entering DSM. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 179 IPU end of frame (EOF) interrupt in the current software implementation. Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.14.52_1.1.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 180 5) Enable the GPMI/BCH clocks in register CCM_CCGR4 Proposed Solution: ROM boot fixed in i.MX 6Dual/6Quad silicon revision 1.3 Linux BSP Status: No BSP software workaround. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 181 Burn more FCB copies(4/8) into the NAND chip to increase the possibility that ROM can find a valid one. Proposed Solution: Fixed in i.MX 6Quad/6Dual silicon revision 1.3. Linux BSP Status: No software workaround available. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 182 1. SD/MMC: Choose an SD/MMC card for which the Nac parameter is to be specified less than 50 ms and its initialization time is less than 500 ms. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 183 4. Provide an external stable 32 kHz clock input prior to de-assertion of POR_B. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 184 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 185 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 186 Table 6. Affected boot modes for the i.MX6Dual/6Quad BOOT_CFG1[7:4] Boot device Affected by this issue 0000 NOR/OneNAND (EIM) Not affected 010x SD/eSD/SDXC Affected 011x MMC/eMMC Affected Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 187 • Workaround #1—Implement and boot the system from SPI, I2C, Parallel NOR or SATA. Covers all boot sources. • Workaround #2—Utilize the i.MX 6Dual/6Quad’s watchdog timer in Serial Downloader mode. Covers all boot sources except NAND. • Workaround #3—Utilize an external watchdog timer or other reset source. Covers all boot sources.

- Page 188 • Users who do not or cannot use SPI/I2C or SATA as a boot source option can use this option. • The i.MX 6Dual/6Quad contains a watchdog timer which can be activated via fuse whenever the processor enters Serial Downloader mode. The Watchdog timer begins a 90-second countdown and, if nothing interrupts this process, the part resets.

- Page 189 Boot loader patch for SPI/I2C, Parallel NOR and SATA boot and the U-boot patch with the correct procedure to reset the PFDs is available for the Linux BSP GA release. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 190 • Specify the plug-in runs in EIM NOR directly instead of in internal RAM Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release rel_imx_3.10.17_1.0.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 191 Proposed Solution: No fix scheduled. Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 192 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 193 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 194 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 195 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 196 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 197 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Linux libata driver avoids this issue. The GHC.IE is set after the GHC.HR is completed. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 198 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 199 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. IS.CCC is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 200 Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. DPS is ignored in the Linux AHCI driver. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 201 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 202 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 203 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 204 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 205 This workaround has the disadvantage that since the PHY is not actually powered-down, there will be increased power consumption (approximately 21 mW on a Freescale reference design) compared to workaround #1. Workaround #3: Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 206 This workaround requires software modification. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround#2 has been implemented in Linux BSP codebase starting in releaseL3.10.17_1.0.0_GA release. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 207 64 kb buffer used for mass read/write commands. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in the Linux BSP codebase starting in release rel_imx_3.14.28_1.0.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 208 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 209 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 210 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 211 FIFO0 and right channel data is always stored in FIFO1. Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.10.53_1.1.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 212 High Speed disconnection detection circuit. This bit should be used to disable this in Suspend, and enable after resume. Proposed Solution: No fix scheduled Linux BSP Solution: Software workaround implemented in BSP version L3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 213 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 214 Proposed Solution: No fix scheduled. Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in release L3.0.35_4.0.0 Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 215 2. Set all bits in the USBPHY_PWD register 3. Set the USBPHY_CTRL.CLKGATE bit Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 216 Set Stream Disable mode (USB_nUSBMODE[SDIS]=1) to prevent receive FIFO overruns. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround implemented in Linux BSP codebase starting in imx_3.10.53_1.1.0_ga. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 217 No fix scheduled Linux BSP Status: Software workaround not implemented in Linux BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 218 Please contact your support channel if you have any questions or concerns. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 219 Before start of H.264 encoder from direct mode, clear the register that generates interrupt by software reset. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release rel_imx_2.6.38_11.11.01. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 220 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 221 0’s until there are 8 bytes in the buffer. This will allow VPU to read out and decode properly. Proposed Solution: No fix scheduled Linux BSP Status: Workaround possible but not implemented in the BSP, impacting functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 222 1080p@30fps for video that displays this issue. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 223 The WDOG SRS software reset bit should be written twice within one period of the 32 kHz clock. Proposed Solution: No fix scheduled Linux BSP Status: Software workaround integrated in Linux BSP codebase starting in release imx_3.0.35_4.1.0. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 224 Linux BSP Status: Software workaround cannot be implemented to mask or workaround this SoC issue. This erratum will result in impacted or reduced functionality as described above. Chip Errata for the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus, Rev. 6.1, 06/2016 NXP Semiconductors...

- Page 225 How to Reach Us: Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses Home Page: granted hereunder to design or fabricate any integrated circuits based on the nxp.com information in this document.

Need help?

Do you have a question about the i.MX 6Dual and is the answer not in the manual?

Questions and answers