Summary of Contents for Teridian 73S8024C

- Page 1 Simplifying System Integration 73S8024C Demo Board User Manual November 11, 2009 Rev. 1.3 UM_8024C_061...

- Page 2 Simplifying System Integration is a trademark of Teridian Semiconductor Corporation. All other trademarks are the property of their respective owners. Teridian Semiconductor Corporation makes no warranty for the use of its products, other than expressly contained in the Company’s warranty detailed in the Teridian Semiconductor Corporation standard Terms and Conditions.

-

Page 3: Table Of Contents

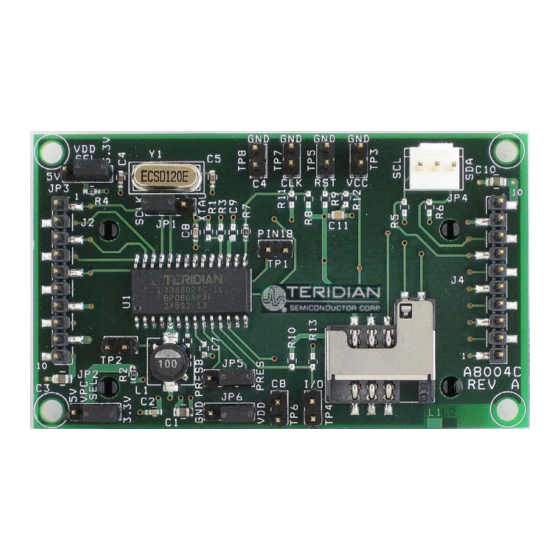

Design Considerations ........................ 12 4.1 General Layout Rules ......................12 4.2 Optimization for Compliance with EMV and NDS ..............12 73S8024C Demo Board Schematics, PCB Layouts and Bill of Materials ........13 5.1 Schematic ..........................13 5.2 Bill of Materials ........................14 5.3 PCB Layouts .......................... - Page 4 Figure 1: 73S8024C Demo Board ......................5 Figure 2: 73S8024C Demo Board Basic Connections ................6 Figure 3: 73S8024C Demo Board Connectors, Jumpers and Test Points ..........8 Figure 4: 73S8024C SO28 Pinout (Top View) ..................11 Figure 5: 73S8024C Demo Board Electrical Schematic ................13 Figure 6: 73S8024C Demo Board Top View ...................

-

Page 5: Introduction

73S1121F evaluation platform. The board has been designed to comply with the EMV 2000 Specification, Version 4.0. 73S8024C Demo Boards can easily be modified to comply with NDS specifications by replacing a few external components that are highlighted in this document. -

Page 6: Basic Connections

I/OUC AUX1UC RSTIN CMDVCC AUX2UC PWRDN 5V/#V CKDIV2 CKDIV1 Power Supply: Configure JP2 to 3.3V Note: CLKSTOP and CLKLEV can be left NC if unused. 5V/#V too, for 5V cards only. Figure 2: 73S8024C Demo Board Basic Connections Rev. 1.3... -

Page 7: Hardware Description

3 Hardware Description Demo Board Connectors, Jumpers and Test Points Table 1 describes the 73S8024C Demo Board connectors, jumpers and test points. The Item # in Table 1 refers to Figure 3. Table 1: 73S8024C Demo Board Connector, Jumper and Test Points... -

Page 8: Figure 3: 73S8024C Demo Board Connectors, Jumpers And Test Points

Factory test pin. Do not connect. 2-pin test points for each respective smart card signal. The pin label name is the respective signal (i.e. VCC, CLK) and the 2nd pin is GND. Figure 3: 73S8024C Demo Board Connectors, Jumpers and Test Points Rev. 1.3... -

Page 9: Recommended Operating Conditions And Absolute Maximum Ratings

ESD Tolerance – Other pins +/- 2 kV ESD testing on Card pins is HBM condition, 3 pulses, each polarity referenced to ground. 73S8024C Pin Description Table 4: 73S8024C Card Interface Pins Name Pin # Description Card I/O: Data signal to/from card. Includes a pull-up resistor to V AUX1 AUX1: Auxiliary data signal to/from card. -

Page 10: Table 5: 73S8024C Miscellaneous Pins

PWRDN Power Down control input. Active high. When the Power Down mode is set high, all internal analog functions are disabled to place the 73S8024C in its lowest power consumption mode. The Power Down mode is only allowed out of a card session (i.e. when CMDVCC = 1) -

Page 11: 73S8024C Pinout

UM_8024C_061 73S8024C Demo Board User Manual 73S8024C Pinout CLKDIV1 AUX2UC CLKDIV2 AUX1UC 5V/#V I/OUC XTALOUT XTALIN 73S8024C PWRDN PRES RSTIN CMDVCC PRES VDDF_ADJ AUX2 AUX1 Figure 4: 73S8024C SO28 Pinout (Top View) Rev. 1.3... -

Page 12: Design Considerations

73S8024C Demo Board User Manual UM_8024C_061 4 Design Considerations General Layout Rules • Route the auxiliary signals away from card interface signals. • Keep the CLK signal as short as possible and with few bends in the trace. Keep the route of the CLK trace to one layer (avoid vias to other plane). -

Page 13: 73S8024C Demo Board Schematics, Pcb Layouts And Bill Of Materials

UM_8024C_061 73S8024C Demo Board User Manual 5 73S8024C Demo Board Schematics, PCB Layouts and Bill of Materials Schematic SCLK SCLK XTALIN SELECT OFFB XTAL 3.3V 5.0V JP2 must be SELECT SSM_110_L_SV set to 3.3V 3.3V Resistors not populated SCLK C1, C2, C8, C9 and L1 must be... -

Page 14: Bill Of Materials

73S8024C Demo Board User Manual UM_8024C_061 Bill of Materials Table 8 provides the bill of materials for the 73S8024C Demo Board schematic provided in Figure 5. Table 8: 73S8024C Demo Board Bill of Materials Digikey Part Item Quantity Reference Part... -

Page 15: Pcb Layouts

UM_8024C_061 73S8024C Demo Board User Manual PCB Layouts Figure 6: 73S8024C Demo Board Top View Figure 7: 73S8024C Demo Board Bottom View Rev. 1.3... -

Page 16: Figure 8: 73S8024C Demo Board Top Signal Layer

73S8024C Demo Board User Manual UM_8024C_061 Figure 8: 73S8024C Demo Board Top Signal Layer Figure 9: 73S8024C Demo Board Middle Layer 1, Ground Plane Rev. 1.3... -

Page 17: Figure 10: 73S8024C Middle Layer 2, Supply Plane

UM_8024C_061 73S8024C Demo Board User Manual Figure 10: 73S8024C Middle Layer 2, Supply Plane Figure 11: 73S8024C Demo Board Bottom Signal Layer Rev. 1.3... -

Page 18: Ordering Information

73S8024C Demo Board User Manual UM_8024C_061 6 Ordering Information Table 9 lists the order number used to identify the 73S8024C Demo Board. Table 9: Order Numbers and Packaging Marks Part Description Order Number 73S8024C 28-Pin SO Demo Board 73S8024C-DB 7 Related Documentation... -

Page 19: Revision History

UM_8024C_061 73S8024C Demo Board User Manual Revision History Revision Date Description 6/8/2004 First publication. 8/2/2004 Minor corrections. 8/23/2005 Added new logo. 11/11/2009 Added Section 1.1, Package Contents. Added Section 1.2, Safety and ESD Notes. Added Section 6, Ordering Information. Added Section 7, Related Documentation. - Page 20 Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: Maxim Integrated 73S8024C-DB...

Need help?

Do you have a question about the 73S8024C and is the answer not in the manual?

Questions and answers