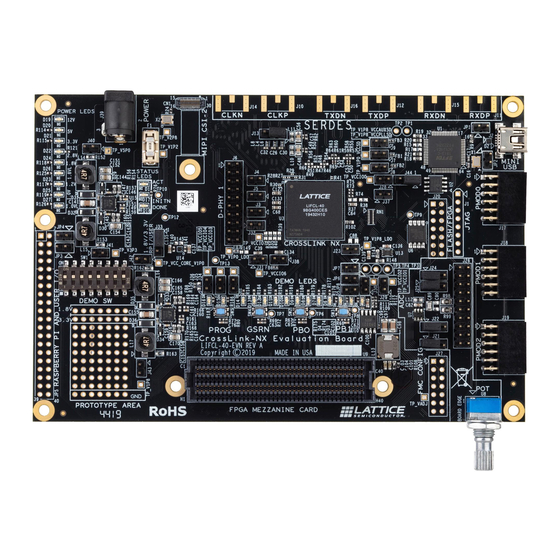

Lattice Semiconductor CrossLink-NX Manuals

Manuals and User Guides for Lattice Semiconductor CrossLink-NX. We have 8 Lattice Semiconductor CrossLink-NX manuals available for free PDF download: User Manual, Quick Start Manual, Quick Start

Lattice Semiconductor CrossLink-NX User Manual (54 pages)

PCIe Bridge Board

Brand: Lattice Semiconductor

|

Category: Network Hardware

|

Size: 3 MB

Table of Contents

Advertisement

Lattice Semiconductor CrossLink-NX User Manual (58 pages)

Brand: Lattice Semiconductor

|

Category: Motherboard

|

Size: 3 MB

Table of Contents

Lattice Semiconductor CrossLink-NX User Manual (46 pages)

PCIe Colorbar Demo for Lattice Nexus-based FPGAs

Brand: Lattice Semiconductor

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

Advertisement

Lattice Semiconductor CrossLink-NX User Manual (22 pages)

ROI User Tracking Using VVML Board Demonstration

Brand: Lattice Semiconductor

|

Category: Motherboard

|

Size: 0 MB

Table of Contents

Lattice Semiconductor CrossLink-NX User Manual (18 pages)

Brand: Lattice Semiconductor

|

Category: Motherboard

|

Size: 0 MB

Table of Contents

Lattice Semiconductor CrossLink-NX User Manual (18 pages)

QVGA MobileNet Human Counting Using VVML Board

Brand: Lattice Semiconductor

|

Category: Computer Hardware

|

Size: 1 MB

Table of Contents

Lattice Semiconductor CrossLink-NX Quick Start Manual (15 pages)

Object Counting Using VGG

Brand: Lattice Semiconductor

|

Category: Computer Hardware

|

Size: 1 MB

Table of Contents

Lattice Semiconductor CrossLink-NX Quick Start (2 pages)

Voice and Vision Machine Learning Board

Brand: Lattice Semiconductor

|

Category: Control Unit

|

Size: 0 MB

Table of Contents

Advertisement

Related Products

- Lattice Semiconductor CrossLink-NX ISP Demo

- Lattice Semiconductor CertusPro-NX

- Lattice Semiconductor CertusPro-NX Versa Board

- Lattice Semiconductor CrossLink

- Lattice Semiconductor iCE40 SPRAM Series

- Lattice Semiconductor iCE40 Ultra

- Lattice Semiconductor LatticeMico GPIO

- Lattice Semiconductor LatticeMico32

- Lattice Semiconductor LatticeMico8

- Lattice Semiconductor sysCLOCK ECP5