GOWIN GW2AR Series User Manual

Package & pinout

Hide thumbs

Also See for GW2AR Series:

- Programming and configuration manual (108 pages) ,

- Programming and configuraion manual (58 pages) ,

- User manual (23 pages)

Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for GOWIN GW2AR Series

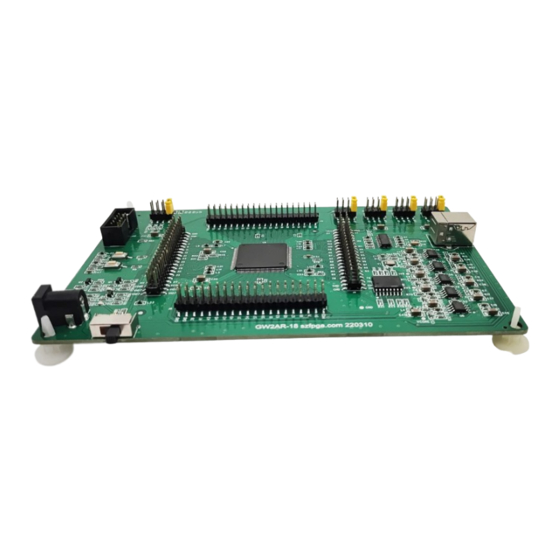

- Page 1 GW2AR series of FPGA Products Package & Pinout User Guide UG229-1.5E, 09/27/2022...

- Page 2 Copyright © 2022 Guangdong Gowin Semiconductor Corporation. All Rights Reserved. and GOWIN are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders.

- Page 3 Revision History Date Version Description 05/11/2018 1.06E Initial version published. For the QN88 and LQ144 packages, VCCX connects with 09/10/2018 1.07E VCCO7. LCDS pair added in Table 2-1. 11/20/2018 1.08E The EQ144 package added. Packages of devices embedded with PSRAM added. ...

-

Page 4: Table Of Contents

Contents Contents Contents ....................... i List of Figures ..................... ii List of Tables ...................... iii 1 About This Guide ..................... 1 1.1 Purpose ..........................1 1.2 Related Documents ......................1 1.3 Abbreviations and Terminology ................... 1 1.4 Support and Feedback ....................... 2 2 Overview ...................... -

Page 5: List Of Figures

List of Figures List of Figures Figure 2-1 GW2AR I/O Bank Distribution ..................8 Figure 3-1 View of GW2AR-18 QN88 Pins Distribution (Embedded with SDRAM) ......10 Figure 3-2 View of GW2AR-18 QN88P Pins Distribution (Embedded with PSRAM) ......11 Figure 3-3 View of GW2AR-18 QN88PF Pins Distribution (Embedded with PSRAM) ...... - Page 6 List of Tables List of Tables Table 1-1 Abbreviations and Terminology ..................1 Table 2-1 Max. I/O Information and LVDS Pair .................. 4 Table 2-2 GW2AR Power Pin ......................4 Table 2-3 Quantity of GW2AR-18 Pins (Devices Embedded With SDRAM) ........5 Table 2-4 Quantity of GW2AR-18 Pins (Devices Embedded With PSRAM) ........

-

Page 7: About This Guide

1.1 Purpose About This Guide 1.1 Purpose This manual contains an introduction to the GW2AR series of FPGA products together with a definition of the pins, a list of pin numbers, distribution of pins, and package diagrams. 1.2 Related Documents The latest user guides are available on GOWINSEMI Website. -

Page 8: Support And Feedback

1 About This Guide 1.4 Support and Feedback 1.4 Support and Feedback Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly using the information provided below. -

Page 9: Overview

2.1 PB-Free Package The GW2AR series of FPGA Products are PB free in line with the EU RoHS environmental directives. The substances used in the GW2AR series of FPGA products are in full compliance with the IPC-1752 standards. -

Page 10: Max. I/O Information And Lvds Pair

2 Overview 2.2 Max. I/O Information and LVDS Pair 2.2 Max. I/O Information and LVDS Pair Table 2-1 Max. I/O Information and LVDS Pair Package Pitch (mm) Size (mm) E-pad Size(mm) GW2AR-18 – LQ144 20 x 20 120(35) EQ144 20 x 20 9.74 x 9.74 120(35) EQ144P... -

Page 11: Pin Quantity

2 Overview 2.4 Pin Quantity 2.4 Pin Quantity Table 2-3 Quantity of GW2AR-18 Pins (Devices Embedded With SDRAM) GW2AR-18 Pin Type QN88 LQ144 EQ144 LQ176 EQ176 BANK0 8/4/2 19/8/4 19/8/4 19/9/6 19/9/6 BANK1 9/4/4 12/6/6 12/6/6 18/9/8 18/9/8 BANK2 4/2/1 12/6/3 12/6/3 12/5/3... -

Page 12: Table 2-4 Quantity Of Gw2Ar-18 Pins (Devices Embedded With Psram)

2 Overview 2.4 Pin Quantity GW2AR-18 Pin Type QN88 LQ144 EQ144 LQ176 EQ176 EXTR JTAGSEL_N Table 2-4 Quantity of GW2AR-18 Pins (Devices Embedded With PSRAM) GW2AR-18 Pin Type QN88P EQ144P QN88PF EQ144PF BANK0 8/4/2 19/8/4 8/4/2 19/8/4 BANK1 9/4/4 12/6/6 9/4/4 12/6/6 BANK2... - Page 13 2 Overview 2.4 Pin Quantity GW2AR-18 Pin Type QN88P EQ144P QN88PF EQ144PF MODE1 MODE2 EXTR JTAGSEL_N Note! [1] Single end/Differential/LVDS I/O quantity include CLK pins, and download pins. [2] JTAGSEL_N and JTAG pins cannot be used as I/O simultaneously. The data in this table is when the loaded four JTAG pins (TCK, TDI, TDO, and TMS) are used as I/O.

-

Page 14: Introduction To The I/O Bank

2 Overview 2.5 Introduction to the I/O BANK 2.5 Introduction to the I/O BANK There are eight I/O Banks in the GW2AR series of FPGA products, as shown in Figure 2-1. Figure 2-1 GW2AR I/O Bank Distribution This manual provides an overview of the distribution view of the pins in the GW2AR series of FPGA products. -

Page 15: View Of Pin Distribution

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View UG229-1.5E 9(26) -

Page 16: View Of Qn88 Pins Distribution (Embedded With Sdram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.1 View of QN88 Pins Distribution (Embedded with SDRAM) Figure 3-1 View of GW2AR-18 QN88 Pins Distribution (Embedded with SDRAM) Table 3-1 Other pins in GW2AR-18 QN88 (Embedded with SDRAM) 1, 22, 45, 66 VCCO0 VCCO1... -

Page 17: View Of Qn88P Pins Distribution (Embedded With Psram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.2 View of QN88P Pins Distribution (Embedded with PSRAM) Figure 3-2 View of GW2AR-18 QN88P Pins Distribution (Embedded with PSRAM) Table 3-2 Other pins in GW2AR-18 QN88P (Embedded with PSRAM) 1, 22, 45, 66 VCCO0 VCCO2/VCCO7... - Page 18 3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View EXTR MODE 87, 88 UG229-1.5E 12(26)

-

Page 19: View Of Qn88Pf Pins Distribution (Embedded With Psram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.3 View of QN88PF Pins Distribution (Embedded with PSRAM) Figure 3-3 View of GW2AR-18 QN88PF Pins Distribution (Embedded with PSRAM) Table 3-3 Other pins in GW2AR-18 QN88PF (Embedded with PSRAM) 1, 22, 45, 66 VCCO0 VCCO2... -

Page 20: View Of Lq144/Eq144 Pins Distribution (Embedded With Sdram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.4 View of LQ144/EQ144 Pins Distribution (Embedded with SDRAM) Figure 3-4 GW2AR-18 LQ144/EQ144 Pins Distribution View (Embedded with SDRAM) Table 3-4 Other pins in GW2AR-18 LQ144/EQ144 (Embedded with SDRAM) VCC/VCCPLLL1 1, 36, 73, 108 VCCO0 VCCO1... - Page 21 3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 2, 17, 53, 74, 89, 107 EXTR MODE 142, 143, 144 UG229-1.5E 15(26)

-

Page 22: View Of Eq144P Pins Distribution (Embedded With Psram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.5 View of EQ144P Pins Distribution (Embedded with PSRAM) Figure 3-5 GW2AR-18 EQ144P Pins Distribution View (Embedded with PSRAM) Table 3-5 Other pins in GW2AR-18 EQ144P (Embedded with PSRAM) VCC/VCCPLLL1 1, 36, 73, 108 VCCO0 VCCO1... -

Page 23: View Of Eq144Pf Pins Distribution (Embedded With Psram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.6 View of EQ144PF Pins Distribution (Embedded with PSRAM) Figure 3-6 GW2AR-18 EQ144PF Pins Distribution View (Embedded with PSRAM) Table 3-6 Other pins in GW2AR-18 EQ144PF (Embedded with PSRAM) VCC/VCCPLLL1 1, 36, 73, 108 VCCO0 VCCO1... - Page 24 3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View EXTR MODE 142, 143, 144 UG229-1.5E 18(26)

-

Page 25: View Of Lq176/Eq176 Pins Distribution (Embedded With Sdram)

3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View 3.1.7 View of LQ176/EQ176 Pins Distribution (Embedded with SDRAM) Figure 3-7 GW2AR-18 LQ176/EQ176 Pins Distribution View (Embedded with SDRAM) Table 3-7 Other pins in GW2AR-18 LQ176/EQ176 (Embedded with SDRAM) 1, 44, 89, 132 VCCO0 155, 176 VCCO1... - Page 26 3 View of Pin Distribution 3.1 GW2AR-18 Pins Distribution View VCCO2/VCCO3/VCCO6/VCCO7 5,13,22,40,95,110,130 VCCPLLL1 VCCPLLR0 VCCPLLR1 2, 43, 46, 87, 90, 131, 134, 175 EXTR MODE 111, 112, 113 UG229-1.5E 20(26)

-

Page 27: Package Diagrams

4 Package Diagrams Package Diagrams UG229-1.5E 21(26) -

Page 28: Qn88/Qn88P/Qn88Pf Package Outline (10Mm X 10Mm)

4 Package Diagrams 4.1 QN88/QN88P/QN88PF Package Outline (10mm x 10mm) 4.1 QN88/QN88P/QN88PF Package Outline (10mm x 10mm) Figure 4-1 Package Outline QN88/QN88P/QN88PF PIN 1(Laser Mark) EXPOSED PAD ZONE BOTTOM VIEW TOP VIEW MILLIMETER SYMBOL SIDE VIEW 0.75 0.80 0.70 0.85 0.90 0.80 0.90... -

Page 29: Lq144 Package Outline (20Mm X 20Mm)

4 Package Diagrams 4.2 LQ144 Package Outline (20mm x 20mm) 4.2 LQ144 Package Outline (20mm x 20mm) Figure 4-2 Package Outline LQ144 UG229-1.5E 23(26) -

Page 30: Eq144/ Eq144P/Eq144Pf Package Outline (20Mm X 20Mm)

4 Package Diagrams 4.3 EQ144/ EQ144P/EQ144PF Package Outline (20mm x 20mm) 4.3 EQ144/ EQ144P/EQ144PF Package Outline (20mm x 20mm) Figure 4-3 Package Outline EQ144/EQ144P/EQ144PF 9.74REF 9.74REF UG229-1.5E 24(26) -

Page 31: Eq176 Package Outline (20Mm X 20Mm)

4 Package Diagrams 4.4 EQ176 Package Outline (20mm x 20mm) 4.4 EQ176 Package Outline (20mm x 20mm) Figure 4-4 Package Outline EQ176 6.00REF 6.00REF UG229-1.5E 25(26) -

Page 32: Lq176 Package Outline (20Mm X 20Mm)

4 Package Diagrams 4.5 LQ176 Package Outline (20mm x 20mm) 4.5 LQ176 Package Outline (20mm x 20mm) Figure 4-5 Package Outline LQ176 0.25 DETAIL: F c1 c BASE METAL WITH PLATING SECTION B-B MILLIMETER SYMBOL 1.60 0.05 0.10 0.15 1.30 1.40 1.50 0.59...

Need help?

Do you have a question about the GW2AR Series and is the answer not in the manual?

Questions and answers