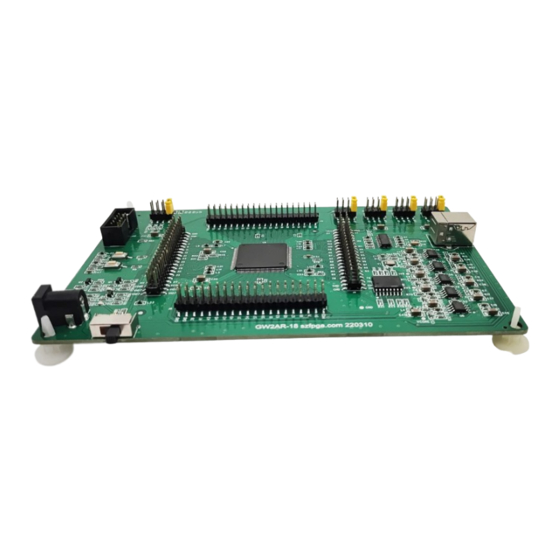

GOWIN GW2AR Series Manuals

Manuals and User Guides for GOWIN GW2AR Series. We have 7 GOWIN GW2AR Series manuals available for free PDF download: Programming And Configuration Manual, Programming And Configuraion Manual, User Manual, Manual, Schematic Manual

GOWIN GW2AR Series Programming And Configuration Manual (108 pages)

Brand: GOWIN

|

Category: Semiconductors

|

Size: 2 MB

Table of Contents

Advertisement

GOWIN GW2AR Series Programming And Configuraion Manual (58 pages)

FPGA products

Brand: GOWIN

|

Category: Semiconductors

|

Size: 0 MB

Table of Contents

GOWIN GW2AR Series User Manual (33 pages)

Package & Pinout

Brand: GOWIN

|

Category: I/O Systems

|

Size: 1 MB

Table of Contents

Advertisement

GOWIN GW2AR Series User Manual (22 pages)

Brand: GOWIN

|

Category: Motherboard

|

Size: 0 MB

Table of Contents

GOWIN GW2AR Series Manual (15 pages)

FPGA Products

Brand: GOWIN

|

Category: Computer Hardware

|

Size: 0 MB

GOWIN GW2AR Series Schematic Manual (15 pages)

Brand: GOWIN

|

Category: Microcontrollers

|

Size: 0 MB

Advertisement