Advertisement

Quick Links

ECLTSSOP20EVB

Evaluation Board User's

Manual for High Frequency

TSSOP 20

INTRODUCTION

ON Semiconductor has developed an evaluation board for

the devices in 20−lead TSSOP package. These evaluation

boards are offered as a convenience for the customers

interested in performing their own engineering assessment

on the general performance of the 20−lead TSSOP device

samples. The board provides a high bandwidth 50 W

controlled impedance environment. Figures 1 and 2 show

the top and bottom view of the evaluation board, which can

be configured in several different ways, depending on

device under test (see Table 1. Configuration List).

This evaluation board manual contains:

•

Information on 20−lead TSSOP Evaluation Board

•

Assembly Instructions

•

Appropriate Lab Setup

•

Bill of Materials

© Semiconductor Components Industries, LLC, 2012

January, 2012 − Rev. 2

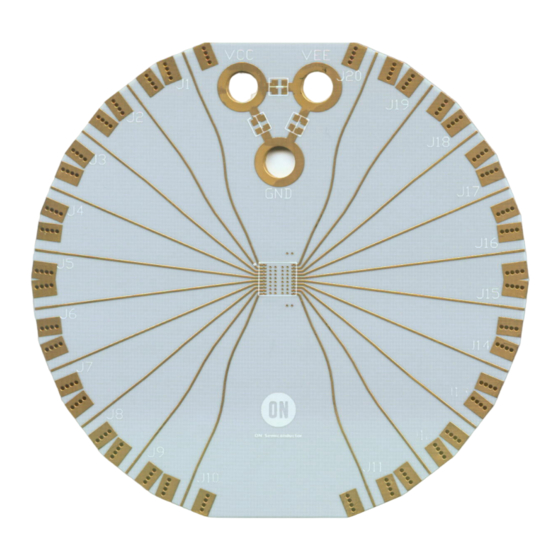

Figure 1. Top View of the 20−lead TSSOP Evaluation Board

EVAL BOARD USER'S MANUAL

This manual should be used in conjunction with the device

data sheet, which contains full technical details on the device

specifications and operation.

Board Lay−Up

The 20−lead TSSOP evaluation board is implemented in

four layers with split (dual) power supplies (see Figure 3.

Evaluation Board Lay−Up). For standard ECL lab setup and

test, a split (dual) power supply is essential to enable the 50

W internal impedance in the oscilloscope as a termination for

ECL devices. The first layer or primary trace layer is 0.008"

thick Rogers RO4003 material, which is designed to have

equal electrical length on all signal traces from the device

under the test (DUT) to the sense output. The second layer

is the 1.0 oz copper ground. The FR4 dielectric material is

placed between second and third layer and between third and

fourth layer. The third layer is the power plane (V

and a portion of this layer is a ground plane. The fourth layer

is the secondary trace layer.

1

http://onsemi.com

& V

CC

Publication Order Number:

EVBUM2057/D

)

EE

Advertisement

Subscribe to Our Youtube Channel

Summary of Contents for ON Semiconductor ECLTSSOP20EVB

- Page 1 INTRODUCTION This manual should be used in conjunction with the device data sheet, which contains full technical details on the device ON Semiconductor has developed an evaluation board for specifications and operation. the devices in 20−lead TSSOP package. These evaluation boards are offered as a convenience for the customers Board Lay−Up...

- Page 2 ECLTSSOP20EVB Bottom View Expanded Bottom View Figure 2. Bottom View of the 20−lead TSSOP Evaluation Board LAY−UP DETAIL 4 LAYER SILKSCREEN (TOP SIDE) LAYER 1 (TOP SIDE) 1 OZ ROGERS 4003 0.008 in LAYER 2 (GROUND PLANE P1) 1 OZ FR−4 0.020 in...

- Page 3 ECLTSSOP20EVB Top View Bottom View Figure 4. Evaluation Board Layout http://onsemi.com...

- Page 4 ECLTSSOP20EVB Pin 20 Pin 1 Ground Pin 19 Pin 2 Pin 18 Pin 3 Pin 17 Pin 4 Pin 16 Pin 5 Pin 15 Pin 6 Pin 14 Pin 7 Pin 13 Pin 8 Pin 12 Pin 9 Pin 11 Pin 10 Figure 5.

- Page 5 ECLTSSOP20EVB Evaluation Board Assembly Instructions It is recommended to solder 0.01 mF capacitors to C4 and The 20−lead TSSOP evaluation board is designed for C5 to reduce the unwanted noise from the power supplies. characterizing devices in a 50 W laboratory environment C1, C2, and C3 pads are provided for 0.1 mF capacitor to...

- Page 6 ECLTSSOP20EVB CONFIGURATIONS CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP14 / LVEP14 0603 CHIP PIN 1 CAPACITOR 0.01 mF WIRE 0402 CHIP RESISTOR 50 W 0805 CHIP CAPACITOR EXPANDED BOTTOM VIEW 0.01 mF EP14 / LVEP14 Figure 6.

- Page 7 ECLTSSOP20EVB CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP17 / LVEP17 PIN 1 0603 CHIP CAPACITOR 0.01 mF 0402 CHIP WIRE RESISTOR 50 W 0805 CHIP CAPACITOR EXPANDED BOTTOM VIEW EP17 / LVEP17 0.01 mF Figure 7.

- Page 8 ECLTSSOP20EVB CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP29 PIN 1 0603 CHIP CAPACITOR 0.01 mF 0402 CHIP WIRE RESISTOR 50 W 0805 CHIP EXPANDED BOTTOM VIEW CAPACITOR EP29 0.01 mF Figure 8. Configuration 3 Table 5.

- Page 9 ECLTSSOP20EVB 0603 CHIP CONNECTORS CAPACITOR 0.1 mF BANANA JACK PLUG 0603 CHIP 0603 CHIP NORMAL TOP VIEW CAPACITOR CAPACITOR EP40 PIN 1 0.01 mF 0.01 mF PIN 1 0402 CHIP RESISTOR WIRE WIRE 50 W 0805 CHIP 0805 CHIP EXPANDED BOTTOM VIEW...

- Page 10 ECLTSSOP20EVB CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP56 / LVEP56 PIN 1 0603 CHIP CAPACITOR 0.01 mF 0402 CHIP RESISTOR WIRE 50 W 0805 CHIP CAPACITOR 0.01 mF EXPANDED BOTTOM VIEW EP56 / LVEP56 Figure 10.

- Page 11 ECLTSSOP20EVB CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP57 PIN 1 0603 CHIP CAPACITOR 0.01 mF 0402 CHIP RESISTOR WIRE 50 W 0805 CHIP CAPACITOR 0.01 mF EXPANDED BOTTOM VIEW EP57 Figure 11. Configuration 6 Table 8.

- Page 12 ECLTSSOP20EVB CONNECTORS 0603 CHIP CAPACITOR 0.1 mF BANANA JACK PLUG NORMAL TOP VIEW EP139 PIN 1 0603 CHIP CAPACITOR 0.01 mF WIRE 0402 CHIP RESISTOR 50 W 0805 CHIP CAPACITOR EXPANDED BOTTOM VIEW 0.01 mF EP139 Figure 12. Configuration 7 Table 9.

- Page 13 ECLTSSOP20EVB LAB SETUP Power Supply Test Measuring Differential Equipment Signal Generator Channel 1 Channel 2 Channel 3 Out1 Channel 4 Out1 Channel 5 Channel 6 Channel 7 Channel 8 Trigger Trigger Figure 13. Example of Standard Lab Setup (Configuration 1) 1.

- Page 14 ECLTSSOP20EVB Table 11. Bill of Materials Components Manufacturer Description Part Number Web Site SMA Connector Johnson SMA Connector, Side 142−0701−851 http://www.johnsoncomponents.com Components* Launch, Gold Plated Banana Jack Keystone* http://www.keyelco.com Standard Jack 6096 Miniature Jack 6090 Chip Capacitor Johanson 500R14Z100MV4E http://www.johansondielectrics.com 0603 0.01 mF...

- Page 15 ECLTSSOP20EVB Top View Second Layer (Ground Plane) Figure 14. Gerber Files http://onsemi.com...

- Page 16 ECLTSSOP20EVB Third Layer (Power and Ground Plane) (Left side − V , Right side − V , Middle Box − Ground) Bottom Layer Figure 15. Gerber Files http://onsemi.com...

- Page 17 LIMITATIONS OF LIABILITY: ON Semiconductor shall not be liable for any special, consequential, incidental, indirect or punitive damages, including, but not limited to the costs of requalification, delay, loss of profits or goodwill, arising out of or in connection with the board, even if ON Semiconductor is advised of the possibility of such damages. In no event shall ON Semiconductor’s aggregate liability from any obligation arising out of or in connection with the board, under any theory of liability, exceed the purchase price paid for the board, if any.

Need help?

Do you have a question about the ECLTSSOP20EVB and is the answer not in the manual?

Questions and answers