Subscribe to Our Youtube Channel

Summary of Contents for Congatec COM Express conga-TC370

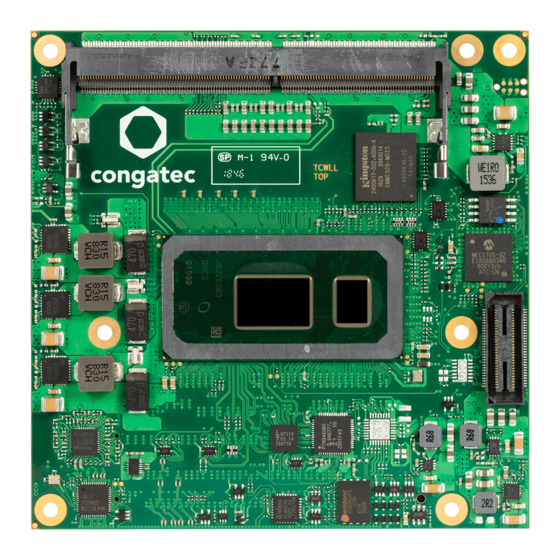

- Page 1 COM Express™ conga-TC370 8th Generation Intel Core™ i7, i5, i3 and Celeron Single Chip Ultra Low TDP Processors ® ® User’s Guide Revision 1.2 Copyright © 2019 congatec AG TCWLm12 1/74...

- Page 2 Corrected also HDMI resolution in section 6.1.3.1 “HDMI” and DP resolution in section 6.1.3.3 “DisplayPort (DP)” • Updated section 7.1 “eMMC 5.1” • Added information about congatec Menu Layout File (MLF) to section 11 “BIOS Setup Description” • Deleted section 12 “Industrial Specifications” 2020-12-08 •...

- Page 3 In no event shall congatec AG be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user’s guide or any other information...

- Page 4 Copyright © 2019, congatec AG. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from congatec AG. congatec AG has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied “as-is”.

- Page 5 (c) arising from course of performance, course of dealing, or usage of trade. congatec AG shall in no event be liable to the end user for collateral or consequential damages of any kind. congatec shall not otherwise be liable for loss, damage or expense directly or indirectly arising from the use of the product or from any other cause.

- Page 6 Technical Support congatec AG technicians and engineers are committed to providing the best possible technical support for our customers so that our products can be easily used and implemented. We request that you first visit our website at www.congatec.com for the latest documentation, utilities and drivers, which have been made available to assist you.

-

Page 7: Table Of Contents

Supply Voltage Battery Power ..........17 Environmental Specifications ........... 17 Additional Features ..............36 Block Diagram ................18 eMMC 5.1 ................36 congatec Board Controller (cBC) ..........36 Cooling Solutions ..............19 7.2.1 Board Information ..............36 7.2.2 General Purpose Input/Output ..........36 CSA Dimensions .............. - Page 8 BIOS Setup Description ............73 11.1 Navigating the BIOS Setup Menu ........... 73 11.2 BIOS Versions................73 11.3 Updating the BIOS ..............74 11.3.1 Update from External Flash ............. 74 11.4 Supported Flash Devices ............74 Copyright © 2019 congatec AG TCWLm12 8/74...

- Page 9 Table 33 Thermal Protection Signal Descriptions ........66 Table 34 SMBus Signal Description ............66 Table 35 General Purpose Serial Interface Signal Descriptions ....66 Table 36 Module Type Definition Signal Description ......67 Copyright © 2019 congatec AG TCWLm12 9/74...

-

Page 10: Introduction

Simply unplug one module and replace it with another; no redesign is necessary. Copyright © 2019 congatec AG TCWLm12... -

Page 11: Options Information

(4 USB 3.1 Gen 2) (4 USB 3.1 Gen 2) SATA (6 Gbps) LVDS DisplayPort (DP) HDMI Processor TDP (cTDP down) 15 (10) W 15 (10) W 15 (10) W 15 (12.5) W Copyright © 2019 congatec AG TCWLm12 11/74... -

Page 12: Specifications

2 UART (16C550 compatible) BIOS AMI Aptio ® V UEFI 2.x firmware 32 MB serial SPI flash with congatec Embedded BIOS features Power ACPI 4.0a compliant with battery support. S5e mode (see section 7.1.7 “Enhanced Soft-Off State” ) Management Deep Sx and Suspend to RAM (S3) -

Page 13: Supported Operating Systems

1. The processor supports only 64-bit operating systems. 2. The CSM (Compatibility Support Module) is disabled in the BIOS setup menu by default because we recommend to operate the system in native UEFI mode. Copyright © 2019 congatec AG TCWLm12 13/74... -

Page 14: Mechanical Dimensions

Supply Voltage Standard Power • 12 V DC ± 5 % The dynamic range shall not exceed the static range. 12.60V Absolute Maximum Dynamic Range 12.10V Nominal Static Range 11.90V 11.40V Absolute Minimum Copyright © 2019 congatec AG TCWLm12 14/74... -

Page 15: Electrical Characteristics

Power Consumption The power consumption values were measured with the following setup: • Input voltage +12 V • conga-TC370 COM • Modified congatec carrier board • conga-TC370 cooling solution • Microsoft Windows 10 (64 bit) Note The CPU was stressed to its maximum workload with the Intel ®... -

Page 16: Table 5 Measurement Description

2.2 / 3.9 0.23 3.29 4.62 0.09 0.07 0.02 ® 048804 2 x 4 GB BUWLR017 Windows 10 Intel Celeron 4305UE 2 2.0 / N.A 0.19 1.47 1.52 0.09 0.07 0.02 ® ® Copyright © 2019 congatec AG TCWLm12 16/74... -

Page 17: Supply Voltage Battery Power

Storage: 5% to 95% Caution The above operating temperatures must be strictly adhered to at all times. When using a congatec heatspreader, the maximum operating temperature refers to any measurable spot on the heatspreader’s surface. Humidity specifications are for non-condensing conditions. -

Page 18: Block Diagram

SM Bus SPI Flash 0 SPI0 PECI MGMNT SDIO GPIO/SDIO congatec Board GPIO I2C Bus Controller LID/SLEEP/FAN LID# / SLEEP# / FAN Generation SER0/1 UART CAN Controller Optional - Not available by default Copyright © 2019 congatec AG TCWLm12 18/74... -

Page 19: Cooling Solutions

1. We recommend a maximum torque of 0.4 Nm for carrier board mounting screws and 0.5 Nm for module mounting screws. 2. The gap pad material used on congatec heatspreaders may contain silicon oil that can seep out over time depending on the environmental conditions it is subjected to. -

Page 20: Csa Dimensions

CSA Dimensions 53.4 79.5 M2.5 x 11 mm threaded standoff for threaded version ø2.7 x 11 mm non-threaded standoff for borehole version Copyright © 2019 congatec AG TCWLm12 20/74... -

Page 21: Csp Dimensions

CSP Dimensions 53.43 79.5 M2.5 x 11 mm threaded standoff for threaded version ø2.7 x 11 mm non-threaded standoff for borehole version Copyright © 2019 congatec AG TCWLm12 21/74... -

Page 22: Hsp Dimensions

HSP Dimensions 53.43 M2.5 x 11 mm threaded standoff for threaded version ø2.7 x 11 mm non-threaded standoff for borehole version Copyright © 2019 congatec AG TCWLm12 22/74... -

Page 23: Heatspreader Thermal Imagery

Heatspreader Thermal Imagery The conga-TC370 heatspreader solution features heatstack, heat pipe and aluminium alloy plate. The aluminium alloy plate distributes the heat evenly on the heatspreader as shown in the thermal imagery below. Copyright © 2019 congatec AG TCWLm12 23/74... -

Page 24: Onboard Temperature Sensors

The board temperature sensor measures the ‘cold-spot’ temperature of the module. The sensor is defined in CGOS API as CGOS_TEMP_ BOARD. The sensor locations are shown below: Temp. Sensor 1 (Cold Spot) CPU Temperature Sensor Copyright © 2019 congatec AG TCWLm12 24/74... -

Page 25: Bottom-Side Sensors

The conga-TC370 features a board temperature sensor on the bottom-side of the module. The sensor measures the ‘hot-spot’ temperature of the module. The sensor is defined in CGOS API as CGOS_TEMP_BOARD_ALT. The sensor location is shown below: Temp. Sensor 2 (Hot Spot) Copyright © 2019 congatec AG TCWLm12 25/74... -

Page 26: Connector Rows

PCI Express Graphics (PEG) The conga-TC370 supports an optional x1 or x2 PEG port on the C–D connector. To support this optional interface, you need a customized conga-TC370 variant. For more information, contact congatec technical support team. Note The PEG lanes can not be linked together with the PCI Express lanes in section 6.1.1 “PCI Express™”. -

Page 27: Digital Display Interface

4096x2304 @ 60 Hz, 24 bpp VGA (BOM option) 1920x1200 @ 60 Hz LVDS 1920x1200 @ 60 Hz (dual LVDS mode) HDMI 4096x2160 @ 24 Hz, 24 bpp 4096x2304 @ 60 Hz, 24 bpp Copyright © 2019 congatec AG TCWLm12 27/74... -

Page 28: Hdmi

• Audio formats such as AC-3 Dolby Digital, Dolby Digital Plus, DTS-HD, LPCM, 192 KHz/24 bit, 8 channel, Dolby TrueHD, DTS-HD Master Audio (Lossless Blu-Ray Disc Audio Format) • maximum of two independent DP displays Copyright © 2019 congatec AG TCWLm12 28/74... -

Page 29: Lvds/Edp

Whiskey Lake ULT SoC does not natively support VGA interface. However, the conga-TC370 can support this interface by integrating ® an optional DisplayPort to VGA adapter chip. Note 1. DDI2 is not supported if VGA is enabled. 2. For VGA support, you need a customized conga-TC370 variant. Copyright © 2019 congatec AG TCWLm12 29/74... -

Page 30: Sata

The USB ports are configured in the BIOS setup menu to operate by default in Gen 1 mode. Before you change the default setting to Gen 2, ensure the carrier board is designed for Gen 2 operation. For Gen 2 design considerations, contact congatec technical support center. -

Page 31: Gigabit Ethernet

10.1.1 “LPC Bus”. 6.1.11 I²C Bus The I²C bus is implemented through the congatec board controller and accessed through the congatec CGOS driver and API. The controller provides a fast-mode multi-master I²C bus that has the maximum I²C bandwidth. 6.1.12 General Purpose Serial Interface The conga-TC370 offers two standard 16C550 UARTs on the A–B connector via the congatec Board Controller. -

Page 32: Gpios

6.1.13 GPIOs The conga-TC370 offers General Purpose Input/Output signals on the A–B connector. The GPIO signals are controlled by the congatec Board controller. 6.1.14 Power Control PWR_OK Power OK from main power supply or carrier board voltage regulator circuitry. A high value indicates that the power is good and the module can start its onboard power sequencing. - Page 33 0.8 V when the 12 V is applied to the module. Actively driving PWR_OK high is compliant to the COM Express specification but this can cause back driving. Therefore, congatec recommends driving the PWR_OK low to keep the module in reset and tri-state PWR_OK when the carrier board hardware is ready to boot.

- Page 34 Do this during the power supply qualification phase to ensure that the above mentioned problem does not occur in the application. For more information, see the “Power Supply Design Guide for Desktop Platform Form Factors” document at www.intel.com. Copyright © 2019 congatec AG TCWLm12...

-

Page 35: Power Management

S3 state, then the resume path will place system back into S3. S5e Power State The conga-TC370 features a congatec proprietary Enhanced Soft-Off power state. See section 7.2.7 “Enhanced Soft-Off State” for more information. Copyright © 2019 congatec AG... -

Page 36: Additional Features

Board Controller (cBC) The conga-TC370 is equipped with Microchip microcontroller. This onboard microcontroller plays an important role for most of the congatec embedded/industrial PC features. It fully isolates some of the embedded features such as system monitoring or the I²C bus from the x86 core architecture, which results in higher embedded feature performance and more reliability, even when the x86 processor is in a low power mode. -

Page 37: Watchdog

Enhanced Soft-Off State The conga-TC370 supports an enhanced Soft-Off state (S5e)—a congatec proprietary low-power Soft-Off state. In this state, the CPU module switches off almost all the onboard logic in order to reduce the power consumption to absolute minimum (between 0.05 mA and 0.09 mA). -

Page 38: Oem Bios Customization

OEM POST Logo This feature allows system designers to replace the congatec POST logo displayed in the upper left corner of the screen during BIOS POST with their own BIOS POST logo. Use the congatec system utility CGUTIL 1.5.4 or later to replace/add the OEM POST logo. -

Page 39: Oem Bios Code/Data

OEM BIOS Code/Data With the congatec embedded BIOS it is possible for system designers to add their own code to the BIOS POST process. The congatec Embedded BIOS first calls the OEM code before handing over control to the OS loader. -

Page 40: Api Support (Cgos)

The architecture of the CGOS API driver provides the ability to write application software that runs unmodified on all congatec CPU modules. All the hardware related code is contained within the congatec embedded BIOS on the module. See section 1.1 of the CGOS API software developers guide, available on the congatec website. -

Page 41: Conga Tech Notes

3. To ensure that the TCC is active for only short periods of time, thus reducing the impact on processor performance to a minimum, it is necessary to have a properly designed thermal solution. The Intel ® Xeon, Core™ i7/i5/i3, Celeron ® and Pentium ® processor’s respective datasheet can provide you with more information about this subject. Copyright © 2019 congatec AG TCWLm12 41/74... -

Page 42: Processor Performance Control

100 MHz on short and regular intervals until the upper limit is met or the maximum possible upside for the number of active cores is reached. For more information about Intel Turbo Boost 2 Technology visit the Intel website. ® ® Copyright © 2019 congatec AG TCWLm12 42/74... -

Page 43: Intel ® Virtualization Technology

See section 8.1 “Adaptive Thermal Monitor and Catastrophic Thermal Protection” for more information. The congatec board controller supports active cooling solution. The board controller controls the fan’s speed based on the temperature readings of the CPU. This feature does not require ACPI OS support. The only software-controlled thermal trip point on conga-TC370 is the Critical Trip Point. -

Page 44: Acpi Suspend Modes And Resume Events

RTC Alarm Activate and configure “Resume On RTC Alarm” in the power setup menu (only available in S5) Watchdog Power Button Event Wakes unconditionally from S3-S5 Copyright © 2019 congatec AG TCWLm12 44/74... -

Page 45: Signal Descriptions And Pinout Tables

The table below describes the terminology used in this section. The PU/PD column indicates if a pull-up or pull-down resistor has been used. If the field entry area in this column for the signal is empty, then no pull-up or pull-down resistor has been implemented by congatec. The “#”... -

Page 46: Connector Signal Descriptions

SATA2_TX- SATA3_TX- LVDS_A3+ LVDS_B3- SUS_S5# PWR_OK LVDS_A3- eDP_BKLT_EN/LVDS_BKLT_EN SATA2_RX+ SATA3_RX+ GND (FIXED) GND (FIXED) SATA2_RX- SATA3_RX- eDP_TX3+/LVDS_A_CK+ LVDS_B_CK+ BATLOW# eDP_TX3-/LVDS_A_CK- LVDS_B_CK- (S)ATA_ACT# HDA_SDIN2 eDP_AUX+/LVDS_I2C_CK eDP/LVDS_BKLT_CTRL HDA_SYNC HDA_SDIN1 eDP_AUX-/LVDS_I2C_DAT VCC_5V_SBY HDA_RST# HDA_SDIN0 GPI3 VCC_5V_SBY Copyright © 2019 congatec AG TCWLm12 46/74... - Page 47 PCIE_TX5+ PCIE_RX5+ A107 VCC_12V B107 VCC_12V PCIE_TX5- PCIE_RX5- A108 VCC_12V B108 VCC_12V GPI0 GPO1 A109 VCC_12V B109 VCC_12V PCIE_TX4+ PCIE_RX4+ A110 GND (FIXED) B110 GND (FIXED) Note Not connected Not supported Bootstrap signals Copyright © 2019 congatec AG TCWLm12 47/74...

-

Page 48: Table 13 Connector C-D Pinout

PEG_TX8- DDI1_PAIR4+ RSVD GND (FIXED) GND (FIXED) DDI1_PAIR4- DDI1_PAIR0+ PEG_RX9+ PEG_TX9+ RSVD DDI1_PAIR0- PEG_RX9- PEG_TX9- RSVD RSVD RSVD RSVD DDI1_PAIR5+ DDI1_PAIR1+ DDI1_PAIR5- DDI1_PAIR1- PEG_RX10+ PEG_TX10+ GND (FIXED) GND (FIXED) PEG_RX10- PEG_TX10- DDI2_CTRLCLK_AUX+ DDI1_PAIR2+ Copyright © 2019 congatec AG TCWLm12 48/74... - Page 49 PEG_RX0+ PEG_TX0+ C107 VCC_12V D107 VCC_12V PEG_RX0- PEG_TX0- C108 VCC_12V D108 VCC_12V TYPE0# PEG_LANE_RV# C109 VCC_12V D109 VCC_12V PEG_RX1+ PEG_TX1+ C110 GND (FIXED) D110 GND (FIXED) Note Not connected Not supported Bootstrap signals Copyright © 2019 congatec AG TCWLm12 49/74...

-

Page 50: Table 14 Pci Express Signal Descriptions (General Purpose)

PCI Express Graphics Lanes used on the carrier board if the design involves more than one PCI Express device Note PCIe lanes 4 and 5 are not supported if the optional PEG port is implemented. Copyright © 2019 congatec AG TCWLm12 50/74... -

Page 51: Table 15 Pci Express Signal Descriptions (X16 Graphics)

PCIE_RX[16-31] + and - PEG_RX1- PEG_RX2+ PEG_RX2- PEG_RX3+ PEG_RX3- PEG_RX4+ PEG_RX4- PEG_RX5+ PEG_RX5- PEG_RX6+ PEG_RX6- PEG_RX7+ PEG_RX7- PEG_RX8+ PEG_RX8- PEG_RX9+ PEG_RX9- PEG_RX10+ PEG_RX10- PEG_RX11+ PEG_RX11- PEG_RX12+ PEG_RX12- PEG_RX13+ PEG_RX13- PEG_RX14+ PEG_RX14- PEG_RX15+ C101 PEG_RX15- C102 Copyright © 2019 congatec AG TCWLm12 51/74... - Page 52 Not supported order Note The conga-TC370 offers optional x1 or x2 PEG port via PCIe lanes 4 or 5, or both. For PEG port support, you need a customized conga-TC370 variant (assembly option) . Copyright © 2019 congatec AG TCWLm12 52/74...

-

Page 53: Table 16 Ddi Signal Description

PU 100 kΩ DDI enable strap already populated DP AUX- function if DDI2_DDC_AUX_SEL is no connect I/O PCIE 3.3 V (see note below) HDMI/DVI I2C CTRLDATA if DDI2_DDC_AUX_SEL is pulled high I/O OD 3.3 V Copyright © 2019 congatec AG TCWLm12 53/74... -

Page 54: Table 17 Hdmi Signal Descriptions

O PCIE TMDS1_DATA0- Multiplexed with DDI1_PAIR2+ and DDI1_PAIR2- TMDS1_DATA1+ HDMI/DVI TMDS differential pair O PCIE TMDS1_DATA1- Multiplexed with DDI1_PAIR1+ and DDI1_PAIR1- TMDS1_DATA2+ HDMI/DVI TMDS differential pair O PCIE TMDS1_DATA2- Multiplexed with DDI1_PAIR0+ and DDI1_PAIR0- Copyright © 2019 congatec AG TCWLm12 54/74... - Page 55 Not supported Multiplexed with DDI3_CTRLDATA_AUX- Note These signals have special functionality during the reset process. They may bootstrap some basic important functions of the module. For more information refer to section 9.2 “Bootstrap Signals”. Copyright © 2019 congatec AG TCWLm12 55/74...

-

Page 56: Table 18 Displayport (Dp) Signal Descriptions

Detection of hot plug / unplug and notification of the link layer; multiplexed with I 3.3 V Not supported DDI3_HPD DP3_AUX+ Half-duplex bi-directional AUX channel for services such as link configuration or I/O PCIE Not supported maintenance and EDID access Copyright © 2019 congatec AG TCWLm12 56/74... -

Page 57: Table 19 Embedded Displayport Signal Descriptions

AUX+ AC coupled off module eDP_AUX- eDP AUX- AC coupled off module eDP_HPD Detection of hot plug / unplug and notification of the link layer I 3.3 V PD 1M Ω Copyright © 2019 congatec AG TCWLm12 57/74... -

Page 58: Table 20 Crt Signal Descriptions

I/O 3.3 V PU 2k2 3.3 V PU for LVDS support (default) LVDS_I2C_DAT DDC lines used for flat panel detection and control I/O 3.3 V PU 2k2 3.3 V PU for LVDS support (default) Copyright © 2019 congatec AG TCWLm12 58/74... -

Page 59: Table 22 Serial Ata Signal Descriptions

USB 2.0 compliant. Backwards compatible to USB 1.1 USB7+ USB Port 7, data + or D+ USB 2.0 compliant. Backwards compatible to USB 1.1 USB7- USB Port 7, data - or D- USB 2.0 compliant. Backwards compatible to USB 1.1 Copyright © 2019 congatec AG TCWLm12 59/74... -

Page 60: Table 24 Usb 3.0 Signal Descriptions

Additional transmit signal differential pairs for the Superspeed USB data path O USB_SSTX2- USB_SSRX3+ Additional receive signal differential pairs for the Superspeed USB data path USB_SSRX3- USB_SSTX3+ Additional transmit signal differential pairs for the Superspeed USB data path O USB_SSTX3- Copyright © 2019 congatec AG TCWLm12 60/74... -

Page 61: Table 25 Gigabit Ethernet Signal Descriptions

The GBE0_LINK# output is not active during a 10 Mb connection. It is only active during a 100 Mb or 1 Gb connection. This is a limitation of Ethernet Phy since it only has 3 LED outputs—ACT#, LINK100# and LINK1000#. The GBE0_LINK# signal is a logic AND of the GBE0_LINK100# and GBE0_LINK1000# signals on the conga-TC370 module. Copyright © 2019 congatec AG TCWLm12 61/74... -

Page 62: Table 26 High Definition Audio Link Signals Descriptions

ESPI Mode: Resets the eSPI interface for both master and slaves. It is typically driven O 1.8 V from eSPI master to esPI slaves. Copyright © 2019 congatec AG TCWLm12 62/74... -

Page 63: Table 28 Spi Bios Flash Interface Signal Descriptions

BIOS disable signals. Note These signals have special functionality during the reset process. They may bootstrap some basic important functions of the module. For more information refer to section 9.2 “Bootstrap Signals”. Copyright © 2019 congatec AG TCWLm12 63/74... -

Page 64: Table 29 Miscellaneous Signal Descriptions

PU 10KΩ 3.3 V Pulled high internally on the module; shared with SD_DATA1 GPI2 General purpose input pin (bidirectional signal) I 3.3 V PU 10KΩ 3.3 V Pulled high internally on the module; shared with SD_DATA2 Copyright © 2019 congatec AG TCWLm12 64/74... -

Page 65: Table 31 Power And System Management Signal Descriptions

Sleep button used by the ACPI operating system to bring the system to sleep state or to wake it I OD 3.3 V PU 100 kΩ 3.3 VSB up again. Note: For proper detection, assert a pulse width of at least 16 ms. Copyright © 2019 congatec AG TCWLm12 65/74... -

Page 66: Table 32 Rapid Shutdown Signal Descriptions

I 3.3 V PU 47 kΩ 3.3 V Note Pins are protected on the module by a series schotty diode. Therefore, pull-down resistor is required on the carrier board for proper logic level. Copyright © 2019 congatec AG TCWLm12 66/74... -

Page 67: Table 36 Module Type Definition Signal Description

In R2.0 this pin is defined as a no-connect for Types 1-6. A carrier can detect a R1.0 module by the presence of 12 V on this pin. R2.0 module Types 1-6 will no-connect this pin. Type 10 modules shall pull this pin to ground through a 4.7 kΩ resistor. Copyright © 2019 congatec AG TCWLm12 67/74... -

Page 68: Table 37 Power And Gnd Signal Descriptions

C76, C80, C84, C87, C90, C93, C96, C100, C103, C110, D1, D2, D5, D8, D11, D14, D21, D31, D41, D51, D60, D67, D70, D73, D76, D80, D84, D87, D90, D93, D96, D100, D103, D110 Copyright © 2019 congatec AG TCWLm12 68/74... -

Page 69: Bootstrap Signals

2. No external DC loads or external pull-up or pull-down resistors should change the configuration of the signals listed in the above table. External resistors may override the internal strap states and cause the COM Express™ module to malfunction and/or cause irreparable damage to the module. Copyright © 2019 congatec AG TCWLm12 69/74... -

Page 70: System Resources

On the conga-TC370, the PCI Express Bus acts as the subtractive decoding agent. All I/O cycles that are not positively decoded are forwarded to the PCI Bus not the LPC Bus. Only specified I/O ranges are forwarded to the LPC Bus. In the congatec Embedded BIOS the following I/O address ranges are sent to the LPC Bus: 2Eh –... -

Page 71: Pci Configuration Space Map

SPI Controller GbE Controller 01h (Note3) PCI Express Port 0 02h (Note3) PCI Express Port 1 03h (Note3) PCI Express Port 2 04h (Note3) PCI Express Port 3 05h (Note3) PCI Express Port 4 Copyright © 2019 congatec AG TCWLm12 71/74... -

Page 72: Sm Bus

4. Internal PCI devices not connected to the conga-TC370 are not listed. 10.3 Onboard resources are not connected to the I²C bus. Address 16h is reserved for congatec Battery Management solutions. 10.4 SM Bus System Management (SM) bus signals are connected to the Intel ®... -

Page 73: Bios Setup Description

Navigating the BIOS Setup Menu The BIOS setup menu shows the features and options supported in the congatec BIOS. To access and navigate the BIOS setup menu, press the <DEL> or <F2> key during POST. The right frame displays the key legend. Above the key legend is an area reserved for text messages. These text messages explain the options and the possible impacts when changing the selected option in the left frame. -

Page 74: Updating The Bios

BIOS updates are recommeded to correct platform issues or enhance the feature set of the module. The conga-TC370 features a congatec/AMI AptioEFI firmware on an onboard flash ROM chip. You can update the firmware with the congatec System Utility. The utility has five versions—...

Need help?

Do you have a question about the COM Express conga-TC370 and is the answer not in the manual?

Questions and answers