Table of Contents

Advertisement

Quick Links

Features

•

Core

– ARM926EJ-S™ ARM

– 16 Kbytes Data Cache, 16 Kbytes Instruction Cache, Memory Management Unit

•

Memories

– One 64-Kbyte internal ROM embedding bootstrap routine: Boot on NAND Flash,

SDCard, DataFlash

– One 32-Kbyte internal SRAM, single-cycle access at system speed

– High Bandwidth Multi-port DDR2 Controller

– 32-bit External Bus Interface supporting 8-bank DDR2/LPDDR, SDR/LPSDR, Static

Memories

– MLC/SLC NAND Controller, with up to 24-bit Programmable Multi-bit Error

Correcting Code (PMECC)

•

System running at up to 133 MHz

– Power-on Reset Cells, Reset Controller, Shut Down Controller, Periodic Interval

Timer, Watchdog Timer and Real Time Clock

– Boot Mode Select Option, Remap Command

– Internal Low Power 32 kHz RC and Fast 12 MHz RC Oscillators

– Selectable 32768 Hz Low-power Oscillator and 12 MHz Oscillator

– One PLL for the system and one PLL at 480 MHz optimized for USB High Speed

– Twelve 32-bit-layer AHB Bus Matrix for large Bandwidth transfers

– Dual Peripheral Bridge with dedicated programmable clock for best performance

– Two dual port 8-channel DMA Controllers

– Advanced Interrupt Controller and Debug Unit

– Two Programmable External Clock Signals

•

Low Power Mode

– Shut Down Controller with four 32-bit Battery Backup Registers

– Clock Generator and Power Management Controller

– Very Slow Clock Operating Mode, Software Programmable Power Optimization

Capabilities

•

Peripherals

– USB Device High Speed, USB Host High Speed and USB Host Full Speed with

dedicated On-Chip Transceiver

– Two 10/100 Mbps Ethernet MAC Controllers

– Two High Speed Memory Card Hosts

– Two CAN Controllers

– Two Master/Slave Serial Peripheral Interface

– Two Three-channel 32-bit Timer/Counters

– One Synchronous Serial Controller

– One Four-channel 16-bit PWM Controller

– Three Two-wire Interfaces

– Four USARTs, two UARTs

– One 12-channel 10-bit Analog-to-Digital Converter

– Soft Modem

•

I/O

– Four 32-bit Parallel Input/Output Controllers

– 105 Programmable I/O Lines Multiplexed with up to Three Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line, optional Schmitt trigger input

– Individually Programmable Open-drain, Pull-up and pull-down resistor,

Synchronous Output

•

Package

– 217-ball BGA, pitch 0.8 mm

®

®

Thumb

Processor running at up to 400 MHz @ 1.0V +/- 10%

®

or serial DataFlash. Programmable order.

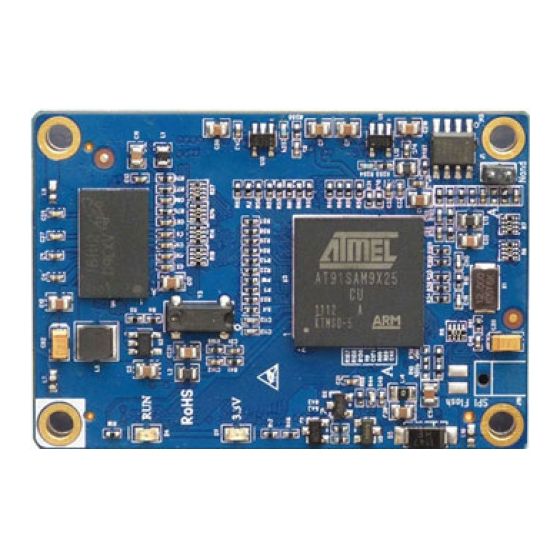

AT91SAM

ARM-based

Embedded MPU

SAM9X25

11054A–ATARM–27-Jul-11

Advertisement

Chapters

Table of Contents

Summary of Contents for Atmel SAM9X25

- Page 1 – Internal Low Power 32 kHz RC and Fast 12 MHz RC Oscillators – Selectable 32768 Hz Low-power Oscillator and 12 MHz Oscillator SAM9X25 – One PLL for the system and one PLL at 480 MHz optimized for USB High Speed –...

- Page 2 Device and Host, FS USB Host, two HS SDCard/SDIO/MMC interfaces, USARTs, SPIs, I2S, TWIs and 10-bit ADC. To ensure uninterrupted data transfer with minimum processor overhead, the SAM9X25 offers a 10-layer bus matrix coupled with 2 x 8 central DMA channels and dedicated DMAs for the high- speed connectivity peripherals.

- Page 3 SAM9X25 2. Block Diagram Figure 2-1. SAM9X25 Block Diagram 11054A–ATARM–27-Jul-11...

- Page 4 External Interrupt Input Input Fast Interrupt Input Input PIO Controller - PIOA - PIOB - PIOC - PIOD PA0-PA31 Parallel IO Controller A PB0-PB18 Parallel IO Controller B PC0-PC31 Parallel IO Controller C PD0-PD21 Parallel IO Controller D SAM9X25 11054A–ATARM–27-Jul-11...

- Page 5 SAM9X25 Table 3-1. Signal Description List (Continued) Signal Name Function Type Active Level External Bus Interface - EBI D0-D15 Data Bus D16-D31 Data Bus A0-A25 Address Bus Output NWAIT External Wait Signal Input Static Memory Controller - SMC NCS0-NCS5 Chip Select Lines...

- Page 6 Serial Peripheral Interface - SPIx SPIx_MISO Master In Slave Out SPIx_MOSI Master Out Slave In SPIx_SPCK SPI Serial Clock SPIx_NPCS0 SPI Peripheral Chip Select 0 SPIx_NPCS1-SPIx_NPCS3 SPI Peripheral Chip Select Output Two-Wire Interface -TWIx TWDx Two-wire Serial Data TWCKx Two-wire Serial Clock SAM9X25 11054A–ATARM–27-Jul-11...

- Page 7 SAM9X25 Table 3-1. Signal Description List (Continued) Signal Name Function Type Active Level Pulse Width Modulation Controller- PWMC PWM0-PWM3 Pulse Width Modulation Output Output USB Host High Speed Port - UHPHS HFSDPA USB Host Port A Full Speed Data +...

- Page 8 Analog-to-Digital Converter - ADC AD0-AD11 12 Analog Inputs Analog ADTRG ADC Trigger Input ADVREF ADC Reference Analog CAN Controller - CANx CANRXx CAN input Input CANTXx CAN output Output Soft Modem - SMD DIBN Soft Modem Signal DIBP Soft Modem Signal SAM9X25 11054A–ATARM–27-Jul-11...

- Page 9 SAM9X25 4. Package and Pinout The SAM9X25 is available in 217-ball BGA package. Overview of the 217-ball BGA Package Figure 4-1 shows the orientation of the 217-ball BGA Package. Figure 4-1. Orientation of the 217-ball BGA Package TOP VIEW A B C D E F G H J...

- Page 10 When “Reset State” is mentioned, the configuration is defined by the “Reset State” column of the Pin Description table. Table 4-2. SAM9X25 I/O Type Assignment and Frequency I/O Frequency Charge Load Output I/O Type (MHz) (pF) Current Signal Name GPIO...

- Page 11 SAM9X25 Indicates if Schmitt Trigger is enabled. Example: Note: The PB18 “Reset State” column shows “PIO, I, PU, ST”. That means the line PIO18 is configured as an Input with Pull-Up and Schmitt Trigger enabled. PD14 reset state is “PIO, I, PU”.

- Page 12 VDDANA GPIO E0_RXDV SPI0_NPCS3 PIO, I, PU, ST VDDANA GPIO_CLK E0_TXCK TWD2 PIO, I, PU, ST VDDANA GPIO E0_MDIO TWCK2 PIO, I, PU, ST VDDANA GPIO_ANA E0_MDC PIO, I, PU, ST VDDANA GPIO_ANA E0_TXEN PIO, I, PU, ST SAM9X25 11054A–ATARM–27-Jul-11...

- Page 13 SAM9X25 Table 4-3. Pin Description BGA217 (Continued) Primary Alternate PIO Peripheral A PIO Peripheral B PIO Peripheral C Reset State Signal, Dir, PU, Ball Power Rail I/O Type Signal Signal Signal Signal Signal PD, ST VDDANA GPIO_ANA E0_TXER PIO, I, PU, ST...

- Page 14 H10, GNDIOM GNDIOM VDDIOP0 POWER VDDIOP0 VDDIOP1 POWER VDDIOP1 GNDIOP GNDIOP VDDBU POWER VDDBU GNDBU GNDBU VDDANA POWER VDDANA GNDANA GNDANA VDDPLLA POWER VDDPLLA VDDOSC POWER VDDOSC GNDOSC GNDOSC H14, VDDCORE POWER VDDCORE GNDCORE GNDCORE VDDUTMII POWER VDDUTMII SAM9X25 11054A–ATARM–27-Jul-11...

- Page 15 SAM9X25 Table 4-3. Pin Description BGA217 (Continued) Primary Alternate PIO Peripheral A PIO Peripheral B PIO Peripheral C Reset State Signal, Dir, PU, Ball Power Rail I/O Type Signal Signal Signal Signal Signal PD, ST VDDUTMIC POWER VDDUTMIC GNDUTMI GNDUTMI...

- Page 16 I, ST VDDIOP0 RSTJTAG I, ST VDDIOP0 RSTJTAG VDDIOP0 RSTJTAG I, ST VDDIOP0 RSTJTAG RTCK VDDIOP0 RSTJTAG NRST I, PU, ST VDDIOP0 RSTJTAG NTRST I, PU, ST VDDBU CLOCK XIN32 VDDBU CLOCK XOUT32 VDDOSC CLOCK VDDOSC CLOCK XOUT SAM9X25 11054A–ATARM–27-Jul-11...

- Page 17 SAM9X25 5. Power Considerations Power Supplies The SAM9X25 has several types of power supply pins. Table 5-1. SAM9X25 Power Supplies Associated Name Voltage Range, nominal Powers Ground ARM core, internal memories, internal peripherals and VDDCORE 0.9-1.1V, 1.0V GNDCORE part of the system controller.

- Page 18 6. Memories Figure 6-1. SAM9X25 Memory Mapping Internal Memory Mapping Address Memory Space 0x0000 0000 0x0000 0000 1 MByte Boot Memory (1) 0x0010 0000 Notes: Internal Memories 256 MBytes 1 MByte (1) Can be ROM, EBI1_NCS0 or SRAM depending on BMS and REMAP...

- Page 19 Embedded Memories 6.2.1 Internal SRAM The SAM9X25 embeds a total of 32 Kbytes of high-speed SRAM. After reset and until the Remap Command is performed, the SRAM is only accessible at address 0x0030 0000. After Remap, the SRAM also becomes available at address 0x0.

- Page 20 • SDRAM Power-up Initialization by Software • CAS Latency of 2, 3 Supported • Auto Precharge Command Not Used • SDR-SDRAM with 16-bit Datapath and Eight Columns Not Supported – Clock Frequency Change in Precharge Power-down Mode Not Supported SAM9X25 11054A–ATARM–27-Jul-11...

- Page 21 SAM9X25 7. System Controller The System Controller is a set of peripherals that allows handling of key elements of the system, such as power, resets, clocks, time, interrupts, watchdog, etc. The System Controller User Interface also embeds the registers that configure the Matrix and a set of registers for the chip configuration.

- Page 22 Figure 7-1. SAM9X25 System Controller Block Diagram System Controller VDDCORE Powered nirq Advanced nfiq Interrupt periph_irq[2..30] Controller ntrst ARM926EJ-S pit_irq por_ntrst wdt_irq dbgu_irq proc_nreset pmc_irq rstc_irq Debug dbgu_irq periph_nreset debug Unit dbgu_txd dbgu_rxd Periodic jtag_nreset Boundary Scan debug pit_irq Interval...

- Page 23 • Chip ID: 0x819A_05A1 • Chip ID Extension: 4 • JTAG ID: 0x05B2_F03F • ARM926 TAP ID: 0x0792_603F Backup Section The SAM9X25 features a Backup Section that embeds: • RC Oscillator • Slow Clock Oscillator • Real Time Counter (RTC) • Shutdown Controller •...

- Page 24 Peripheral Identifiers Table 8-1 defines the Peripheral Identifiers of the SAM9X25. A peripheral identifier is required for the control of the peripheral interrupt with the Advanced Interrupt Controller and for the con- trol of the peripheral clock with the Power Management Controller.

- Page 25 Advanced Interrupt Controller Peripheral Signal Multiplexing on I/O Lines The SAM9X25 features 4 PIO Controllers, PIOA, PIOB, PIOC and PIOD, which multiplex the I/O lines of the peripheral set. Each PIO Controller controls 32 lines, 19 lines, 32 lines and 22 lines respectively for PIOA, PIOB, PIOC and PIOD.

- Page 26 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 27 SAM9X25 SAM9X25 ™ 9. ARM926EJ-S Description ™ The ARM926EJ-S processor is a member of the ARM9 family of general-purpose microproces- sors. The ARM926EJ-S implements ARM architecture version 5TEJ and is targeted at multi- tasking applications where full memory management, high performance, low die size and low power are all important features.

- Page 28 – Separate AMBA AHB Buses for Both the 32-bit Data Interface and the 32-bit Instructions Interface • Bus Interface Unit – Arbitrates and Schedules AHB Requests – Enables Multi-layer AHB to be Implemented – Increases Overall Bus Bandwidth – Makes System Architecture Mode Flexible SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 29 SAM9X25 SAM9X25 Block Diagram Figure 9-1. ARM926EJ-S Internal Functional Block Diagram External Coprocessors ETM9 CP15 System External Trace Port Configuration Coprocessor Interface Coprocessor Interface Write Data ARM9EJ-S Processor Core Instruction Fetches Read Data Data Instruction Address Address Instruction DTCM ITCM...

- Page 30 ARM instructions. The hardware/software split is invisible to the programmer, invisible to the application and invisible to the operating system. All existing ARM registers are re-used in Jazelle state and all registers then have particular functions in this mode. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 31 SAM9X25 SAM9X25 Minimum interrupt latency is maintained across both ARM state and Java state. Since byte codes execution can be restarted, an interrupt automatically triggers the core to switch from Java state to ARM state for the execution of the interrupt handler. This means that no special provision has to be made for handling interrupts while executing byte codes, whether in hard- ware or in software.

- Page 32 The Thumb state register set is a subset of the ARM state set. The programmer has direct access to: • Eight general-purpose registers r0-r7 • Stack pointer, SP • Link register, LR (ARM r14) • PC • CPSR SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 33 SAM9X25 SAM9X25 There are banked registers SPs, LRs and SPSRs for each privileged mode (for more details see the ARM9EJ-S Technical Reference Manual, revision r1p2 page 2-12). 9.4.7.1 Status Registers The ARM9EJ-S core contains one CPSR, and five SPSRs for exception handlers to use. The program status registers: •...

- Page 34 Execute stage in the pipeline. If the instruction is not executed, for example because a branch occurs while it is in the pipeline, the abort does not take place. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 35 SAM9X25 SAM9X25 The breakpoint (BKPT) instruction is a new feature of ARM9EJ-S that is destined to solve the problem of the Prefetch Abort. A breakpoint instruction operates as though the instruction caused a Prefetch Abort. A breakpoint instruction does not cause the ARM9EJ-S to take the Prefetch Abort exception until the instruction reaches the Execute stage of the pipeline.

- Page 36 Thumb Instruction Set Overview The Thumb instruction set is a re-encoded subset of the ARM instruction set. The Thumb instruction set is divided into: • Branch instructions • Data processing instructions • Load and Store instructions SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 37 SAM9X25 SAM9X25 • Load and Store multiple instructions • Exception-generating instruction For further details, see the ARM Technical Reference Manual. Table 9-4 gives the Thumb instruction mnemonic list. Table 9-4. Thumb Instruction Mnemonic List Mnemonic Operation Mnemonic Operation Move Move Not...

- Page 38 1. Register locations 0,5, and 13 each provide access to more than one register. The register accessed depends on the value of the opcode_2 field. 2. Register location 9 provides access to more than one register. The register accessed depends on the value of the CRm field. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 39 SAM9X25 SAM9X25 9.5.1 CP15 Registers Access CP15 registers can only be accessed in privileged mode by: • MCR (Move to Coprocessor from ARM Register) instruction is used to write an ARM register to CP15. • MRC (Move to ARM Register from Coprocessor) instruction is used to read the value of CP15 to an ARM register.

- Page 40 Virtual Address), the access control logic determines if the access is permitted and outputs the appropriate physical address corresponding to the MVA. If access is not permitted, the MMU signals the CPU core to abort. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 41 SAM9X25 SAM9X25 If the TLB does not contain an entry for the MVA, the translation table walk hardware is invoked to retrieve the translation information from the translation table in physical memory. 9.6.3 Translation Table Walk Hardware The translation table walk hardware is a logic that traverses the translation tables located in physical memory, gets the physical address and access permissions and updates the TLB.

- Page 42 The Write Buffer can hold up to 16 words of data and four separate addresses. DCache and Write Buffer operations are closely connected as their configuration is set in each section by the page descriptor in the MMU translation table. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 43 Any ARM9EJ-S core request that is not 1, 4, 8 words in size is split into packets of these sizes. Note that the Atmel bus is AHB-Lite protocol compliant, hence it does not support split and retry requests.

- Page 44 AHB. If the ARM9EJ-S is in Thumb state, then two instructions can be fetched at a time. 9.8.3 Address Alignment The ARM926EJ-S BIU performs address alignment checking and aligns AHB addresses to the necessary boundary. 16-bit accesses are aligned to halfword boundaries, and 32-bit accesses are aligned to word boundaries. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 45 10.1 Description The SAM9X25 features a number of complementary debug and test capabilities. A common JTAG/ICE (In-Circuit Emulator) port is used for standard debugging functions, such as down- loading code and single-stepping through programs. The Debug Unit provides a two-pin UART that can be used to upload an application into internal SRAM.

- Page 46 10.3 Block Diagram Figure 10-1. Debug and Test Block Diagram NTRST ICE/JTAG JTAGSEL Boundary Port RTCK Reset Test ARM9EJ-S ICE-RT ARM926EJ-S DTXD DBGU DRXD TAP: Test Access Port SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 47 SAM9X25 SAM9X25 10.4 Application Examples 10.4.1 Debug Environment Figure 10-2 shows a complete debug environment example. The ICE/JTAG interface is used for standard debugging functions, such as downloading code and single-stepping through the pro- gram. A software debugger running on a personal computer provides the user interface for configuring a Trace Port interface utilizing the ICE/JTAG interface.

- Page 48 These devices can be connected to form a single scan chain. Figure 10-3. Application Test Environment Example Test Adaptor Tester JTAG Interface ICE/JTAG Chip n Chip 2 Connector SAM9 Chip 1 SAM9-based Application Board In Test SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 49 SAM9X25 SAM9X25 10.5 Debug and Test Pin Description Table 10-1. Debug and Test Pin List Pin Name Function Type Active Level Reset/Test NRST Microcontroller Reset Input/Output Test Mode Select Input High ICE and JTAG NTRST Test Reset Signal Input Test Clock...

- Page 50 NTRST (optional in IEEE Standard 1149.1) is a Test-ReSeT input which is mandatory in ARM cores and used to reset the debug logic. On Atmel ARM926EJ-S-based cores, NTRST is a Power On Reset output. It is asserted on power on. If necessary, the user can also reset the debug logic with the NTRST pin assertion during 2.5 MCK periods.

- Page 51 SAM9X25 SAM9X25 10.6.4 Debug Unit The Debug Unit provides a two-pin (DXRD and TXRD) USART that can be used for several debug and trace purposes and offers an ideal means for in-situ programming solutions and debug monitor communication. Moreover, the association with two peripheral data controller channels permits packet handling of these tasks with processor time reduced to a minimum.

- Page 52 • VERSION[31:28]: Product Version Number Set to 0x0. • PART NUMBER[27:12]: Product Part Number Product part Number is 0x5B2F • MANUFACTURER IDENTITY[11:1] Set to 0x01F. Bit[0] required by IEEE Std. 1149.1. Set to 0x1. JTAG ID Code value is 0x05B2_F03F. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 53 SAM9X25 SAM9X25 11. Boot Strategies The system always boots at address 0x0. To ensure maximum boot possibilities, the memory layout can be changed thanks to the BMS pin. This allows the user to layout the ROM or an external memory to 0x0. The sampling of the BMS pin is done at reset.

- Page 54 48 MHz. If an external clock or crystal frequency running at 12 MHz is found, then the PLLA is configured to allow communication on the USB link for the SAM-BA Monitor; else the Main Clock is switched to the internal 12 MHz Fast RC, but USB will not be activated. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 55 SAM9X25 SAM9X25 11.4 NVM Boot 11.4.1 NVM Boot Sequence The boot sequence on external memory devices can be controlled using the Boot Sequence Register (BSCR). The 3 LSBs of the BSCR are available to control the sequence. The user can then choose to bypass some steps shown in Figure 11-2 “NVM Bootloader...

- Page 56 NAND Flash Bootloader NAND Flash to SRAM Y es Copy from SPI0 CS1 Flash Boot SPI Flash Bootloader SPI Flash to SRAM Y es Copy from TWI EEPROM Boot TWI EEPROM Bootloader TWI EEPROM to SRAM SAM-BA Monitor SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 57 SAM9X25 SAM9X25 11.4.2 NVM Bootloader Program Description Figure 11-3. NVM Bootloader Program Diagram Start Initialize NVM Restore the reset values Initialization OK ? for the peripherals and Jump to next boot solution Y es Valid code detection in NVM NVM contains valid code...

- Page 58 Unconditional instruction: 0xE for bits 31 to 28 Load PC with PC relative addressing instruction: – Rn = Rd = PC = 0xF – I==0 (12-bit immediate value) – P==1 (pre-indexed) – U offset added (U==1) or subtracted (U==0) – W==1 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 59 SAM9X25 SAM9X25 The sixth vector, at offset 0x14, contains the size of the image to download. The user must replace this vector with the user’s own vector. This information is described below. Figure 11-7. Structure of the ARM Vector 6 Size of the code to download in bytes The value has to be smaller than 24 kbytes.

- Page 60 NVM to internal SRAM. Restore the reset values for the peripherals. Perform the REMAP and set the PC to 0 to jump to the downloaded application Restore the reset values for the peripherals and Jump to next bootable memory SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 61 SAM9X25 SAM9X25 NAND Flash Specific Header Detection This is the first method used to determine NAND Flash parameters. After Initialization and Reset command, the Boot Program reads the first page without ECC check, to determine if the NAND parameter header is present. The header is made of 52 times the same 32-bit word (for redun- dancy reasons) which must contain NAND and PMECC parameters used to correctly perform the read of the rest of the data in the NAND.

- Page 62 PMECC_status, unsigned int pageBuffer) pPMECC: pointer to the PMECC base address, pPMERRLOC: pointer to the PMERRLOC base address, PMECC_desc: pointer to the PMECC descriptor, PMECC_status: the status returned by the read of PMECCISR register; SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 63 SAM9X25 SAM9X25 pageBuffer: address of the buffer containing the page to be corrected. The PMECC descriptor structure is: typedef struct _PMECC_paramDesc_struct { unsigned int pageSize; unsigned int spareSize; unsigned int sectorSize; // 0 for 512, 1 for 1024 bytes unsigned int errBitNbrCapability;...

- Page 64 For a full description and an example of how to use the PMECC detection and correction fea- ture, refer to the software package dedicated to this device on Atmel’s web site. 11.4.4.3 SD Card Boot The SD Card bootloader uses MCI0. It looks for a “boot.bin” file in the root directory of a FAT12/16/32 formatted SD Card.

- Page 65 SAM9X25 SAM9X25 Supported DataFlash Devices The SPI Flash Boot program supports all Atmel DataFlash devices. Table 11-2. DataFlash Device Device Density Page Size (bytes) Number of Pages AT45DB011 1 Mbit AT45DB021 2 Mbits 1024 AT45DB041 4 Mbits 2048 AT45DB081 8 Mbits...

- Page 66 – Check if USB Device enumeration has occurred – Check if characters have been received on the DBGU Once the communication interface is identified, the application runs in an infinite loop waiting for different commands as listed in Table 11-4. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 67 SAM9X25 SAM9X25 Figure 11-10. SAM-BA Monitor Diagram No valid code in NVM Init DBGU and USB USB Enumeration Character(s) received Successful ? on DBGU ? Run monitor Run monitor Wait for command Wait for command on the USB link on the DBGU link 11.5.1...

- Page 68 – <blk #> = binary number, starts at 01, increments by 1, and wraps 0FFH to 00H (not to 01) – <255-blk #> = 1’s complement of the blk#. – <checksum> = 2 bytes CRC16 Figure 11-11 shows a transmission using this protocol. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 69 ISDN modems and virtual COM ports. The Vendor ID is Atmel’s vendor ID 0x03EB. The product ID is 0x6124. These references are used by the host operating system to mount the correct driver. On Windows systems, the INF files contain the correspondence between vendor ID and product ID.

- Page 70 BA Boot commands are sent by the host through endpoint 1. If required, the message is split by the host into several data payloads by the host driver. If the command requires a response, the host can send IN transactions to pick up the response. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 71 SAM9X25 SAM9X25 12. Boot Sequence Controller (BSC) 12.1 Description The System Controller embeds a Boot Sequence Configuration Register to save timeout delays on boot. The boot sequence is programmable through the Boot Sequence Configuration Regis- ter (BSCR). This register is powered by VDDBU, the modification is saved and applied after the next reset.

- Page 72 Factory Value:0x0000_0000 BOOTKEY BOOT BOOT BOOT • BOOTx: Boot media sequence Is defined in the product-dependent ROM code. • BOOTKEY 0xB5 (VALID): valid boot key To avoid spurious writing, this key is necessary for write accesses. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 73 SAM9X25 SAM9X25 13. Advanced Interrupt Controller (AIC) 13.1 Description The Advanced Interrupt Controller (AIC) is an 8-level priority, individually maskable, vectored interrupt controller, providing handling of up to thirty-two interrupt sources. It is designed to sub- stantially reduce the software and real-time overhead in handling internal and external interrupts.

- Page 74 Advanced Interrupt Controller Processor Fast nFIQ External Interrupt Controller Source Controller Input Stage nIRQ IRQ0-IRQn Interrupt Fast PIOIRQ Processor Priority Forcing Clock Controller Internal Source Power Input Management Stage Embedded Controller Peripherals User Interface Wake Up SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 75 SAM9X25 SAM9X25 13.6 I/O Line Description Table 13-1. I/O Line Description Pin Name Pin Description Type Fast Interrupt Input IRQ0 - IRQn Interrupt 0 - Interrupt n Input 13.7 Product Dependencies 13.7.1 I/O Lines The interrupt signals FIQ and IRQ0 to IRQn are normally multiplexed through the PIO control- lers.

- Page 76 “Priority Controller” on page 79) and the register AIC_CISR gives an image of the signals nIRQ and nFIQ driven on the processor. Each status referred to above can be used to optimize the interrupt handling of the systems. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 77 SAM9X25 SAM9X25 Figure 13-4. Internal Interrupt Source Input Stage AIC_SMRI (SRCTYPE) Level/ AIC_IPR Source i Edge AIC_IMR Fast Interrupt Controller Priority Controller Edge AIC_IECR Detector Clear AIC_ISCR AIC_ICCR AIC_IDCR Figure 13-5. External Interrupt Source Input Stage AIC_SMRi SRCTYPE High/Low Level/...

- Page 78 Maximum FIQ Latency = 4 Cycles Figure 13-7. External Interrupt Level Sensitive Source IRQ or FIQ (High Level) IRQ or FIQ (Low Level) nIRQ Maximum IRQ Latency = 3 Cycles nFIQ Maximum FIQ Latency = 3 cycles SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 79 SAM9X25 SAM9X25 Figure 13-8. Internal Interrupt Edge Triggered Source nIRQ Maximum IRQ Latency = 4.5 Cycles Peripheral Interrupt Becomes Active Figure 13-9. Internal Interrupt Level Sensitive Source nIRQ Maximum IRQ Latency = 3.5 Cycles Peripheral Interrupt Becomes Active 13.8.3 Normal Interrupt 13.8.3.1...

- Page 80 This section gives an overview of the fast interrupt handling sequence when using the AIC. It is assumed that the programmer understands the architecture of the ARM processor, and espe- cially the processor interrupt modes and the associated status bits. It is assumed that: SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 81 SAM9X25 SAM9X25 1. The Advanced Interrupt Controller has been programmed, AIC_SVR registers are loaded with corresponding interrupt service routine addresses and interrupts are enabled. 2. The instruction at the ARM interrupt exception vector address is required to work with the vectoring LDR PC, [PC, # -&F20]...

- Page 82 2. The ARM core enters FIQ mode. 3. When the instruction loaded at address 0x1C is executed, the program counter is loaded with the value read in AIC_FVR. Reading the AIC_FVR has effect of automati- SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 83 SAM9X25 SAM9X25 cally clearing the fast interrupt, if it has been programmed to be edge triggered. In this case only, it de-asserts the nFIQ line on the processor. 4. The previous step enables branching to the corresponding interrupt service routine. It is not necessary to save the link register R14_fiq and SPSR_fiq if nested fast interrupts are not needed.

- Page 84 AIC_ISR. Extra AIC_IVR reads perform the same operations. However, it is recommended to not stop the processor between the read and the write of AIC_IVR of the interrupt service routine to make sure the debugger does not modify the AIC context. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 85 SAM9X25 SAM9X25 To summarize, in normal operating mode, the read of AIC_IVR performs the following opera- tions within the AIC: 1. Calculates active interrupt (higher than current or spurious). 2. Determines and returns the vector of the active interrupt. 3. Memorizes the interrupt.

- Page 86 The protected registers are: • “AIC Source Mode Register” on page 88 • “AIC Source Vector Register” on page 89 • “AIC Spurious Interrupt Vector Register” on page 100 • “AIC Debug Control Register” on page 101 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

-

Page 87: Table Of Contents

SAM9X25 SAM9X25 13.10 Advanced Interrupt Controller (AIC) User Interface 13.10.1 Base Address The AIC is mapped at the address 0xFFFF F000. It has a total 4-Kbyte addressing space. This permits the vectoring fea- ture, as the PC-relative load/store instructions of the ARM processor support only a ± 4-Kbyte offset. - Page 88 Positive edge triggered for internal source INT_EDGE_TRIGGERED Negative edge triggered for external source High level Sensitive for internal source EXT_HIGH_LEVEL High level Sensitive for external source Positive edge triggered for internal source EXT_POSITIVE_EDGE Positive edge triggered for external source SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

-

Page 89: Name Aic_Smr0

SAM9X25 SAM9X25 13.10.3 AIC Source Vector Register Name: AIC_SVR0..AIC_SVR31 Address: 0xFFFFF080 Access: Read-write Reset: VECTOR VECTOR VECTOR VECTOR This register can only be written if the WPEN bit is cleared in AIC Write Protect Mode Register • VECTOR: Source Vector The user may store in these registers the addresses of the corresponding handler for each interrupt source. -

Page 90: Aic_Ivr

The Source Vector Register is indexed using the current interrupt number when the Interrupt Vector Register is read. When there is no current interrupt, the Interrupt Vector Register reads the value stored in AIC_SPU. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11... -

Page 91: Aic_Fvr

SAM9X25 SAM9X25 13.10.5 AIC FIQ Vector Register Name: AIC_FVR Address: 0xFFFFF104 Access: Read-only Reset: FIQV FIQV FIQV FIQV • FIQV: FIQ Vector Register The FIQ Vector Register contains the vector programmed by the user in the Source Vector Register 0. When there is no fast interrupt, the FIQ Vector Register reads the value stored in AIC_SPU. -

Page 92: Aic_Isr

– – – – – – – – – – – – – – – – – – – – IRQID • IRQID: Current Interrupt Identifier The Interrupt Status Register returns the current interrupt source number. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 93: Aic_Ipr

SAM9X25 SAM9X25 13.10.7 AIC Interrupt Pending Register Name: AIC_IPR Address: 0xFFFFF10C Access: Read-only Reset: PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6... -

Page 94: Aic_Cisr

– – NIRQ NFIQ • NFIQ: NFIQ Status 0 = nFIQ line is deactivated. 1 = nFIQ line is active. • NIRQ: NIRQ Status 0 = nIRQ line is deactivated. 1 = nIRQ line is active. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 95: Aic_Iecr

SAM9X25 SAM9X25 13.10.10 AIC Interrupt Enable Command Register Name: AIC_IECR Address: 0xFFFFF120 Access: Write-only PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6... -

Page 96: Aic_Idcr

PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6 PID5 PID4 PID3 PID2 • FIQ, SYS, PID2-PID31: Interrupt Disable 0 = No effect. 1 = Disables corresponding interrupt. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 97: Aic_Iccr

SAM9X25 SAM9X25 13.10.12 AIC Interrupt Clear Command Register Name: AIC_ICCR Address: 0xFFFFF128 Access: Write-only PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6... -

Page 98: Aic_Iscr

PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6 PID5 PID4 PID3 PID2 • FIQ, SYS, PID2-PID31: Interrupt Set 0 = No effect. 1 = Sets corresponding interrupt. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 99: Aic_Eoicr

SAM9X25 SAM9X25 13.10.14 AIC End of Interrupt Command Register Name: AIC_EOICR Address: 0xFFFFF130 Access: Write-only – – – – – – – – – – – – – – – – – – – – – – – – –... -

Page 100: Aic_Spu

The user may store the address of a spurious interrupt handler in this register. The written value is returned in AIC_IVR in case of a spurious interrupt and in AIC_FVR in case of a spurious fast interrupt. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11... -

Page 101: Aic_Dcr

SAM9X25 SAM9X25 13.10.16 AIC Debug Control Register Name: AIC_DCR Address: 0xFFFFF138 Access: Read-write Reset: – – – – – – – – – – – – – – – – – – – – – – – – – –... - Page 102 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6 PID5 PID4 PID3 PID2 – • SYS, PID2-PID31: Fast Forcing Enable 0 = No effect. 1 = Enables the fast forcing feature on the corresponding interrupt. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 103 SAM9X25 SAM9X25 13.10.18 AIC Fast Forcing Disable Register Name: AIC_FFDR Address: 0xFFFFF144 Access: Write-only PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6...

- Page 104 PID6 PID5 PID4 PID3 PID2 – • SYS, PID2-PID31: Fast Forcing Status 0 = The Fast Forcing feature is disabled on the corresponding interrupt. 1 = The Fast Forcing feature is enabled on the corresponding interrupt. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 105 SAM9X25 SAM9X25 13.10.20 AIC Write Protect Mode Register Name: AIC_WPMR Address: 0xFFFFF1E4 Access: Read-write Reset: Table 13-3 WPKEY WPKEY WPKEY — — — — — — — WPEN • WPEN: Write Protect Enable 0 = Disables the Write Protect if WPKEY corresponds to 0x414943 ("AIC" in ASCII).

-

Page 106: Aic_Wpsr

• WPVSRC: Write Protect Violation Source When WPVS is active, this field indicates the write-protected register (through address offset or code) in which a write access has been attempted. Note: Reading AIC_WPSR automatically clears all fields. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... - Page 107 SAM9X25 SAM9X25 14. Reset Controller (RSTC) 14.1 Description The Reset Controller (RSTC), based on power-on reset cells, handles all the resets of the sys- tem without any external components. It reports which reset occurred last. The Reset Controller also drives independently or simultaneously the external reset and the peripheral and processor resets.

- Page 108 Characteristics in the Electrical Characteristics section of the product documentation. The Reset Controller Mode Register (RSTC_MR), allowing the configuration of the Reset Con- troller, is powered with VDDBU, so that its configuration is saved as long as VDDBU is on. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 109 SAM9X25 SAM9X25 14.4.2 NRST Manager After power-up, NRST is an output during the ERSTL time defined in the RSTC. When ERSTL elapsed, the pin behaves as an input and all the system is held in reset if NRST is tied to GND by an external signal.

- Page 110 VDDBU only activates the backup_nreset signal. The backup_nreset must be released so that any other reset can be generated by VDDCORE (Main Supply POR output). Figure 14-4 shows how the General Reset affects the reset signals. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 111 SAM9X25 SAM9X25 Figure 14-4. General Reset State SLCK Freq. Backup Supply POR output Startup Time Main Supply POR output backup_nreset Processor Startup proc_nreset RSTTYP 0x0 = General Reset periph_nreset NRST (nrst_out) EXTERNAL RESET LENGTH BMS Sampling = 2 cycles 14.4.5.2 Wake-up Reset The Wake-up Reset occurs when the Main Supply is down.

- Page 112 EXTERNAL_RESET_LENGTH Slow Clock cycles, as programmed in the field ERSTL. How- ever, if NRST does not rise after EXTERNAL_RESET_LENGTH because it is driven low externally, the internal reset lines remain asserted until NRST actually rises. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 113 SAM9X25 SAM9X25 Figure 14-6. User Reset State SLCK Freq. NRST Resynch. Processor Startup 2 cycles proc_nreset RSTTYP 0x4 = User Reset periph_nreset NRST (nrst_out) >= EXTERNAL RESET LENGTH 14.4.5.4 Software Reset The Reset Controller offers several commands used to assert the different reset signals. These commands are performed by writing the Control Register (RSTC_CR) with the following bits at •...

- Page 114 WDRSTEN is set, the Watchdog Timer is always reset after a Watchdog Reset and the Watchdog is enabled by default and with a period set to a maximum. When the WDRSTEN in WDT_MR bit is reset, the watchdog fault has no impact on the reset controller. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 115 SAM9X25 SAM9X25 Figure 14-8. Watchdog Reset SLCK Freq. wd_fault Processor Startup = 3 cycles proc_nreset RSTTYP 0x2 = Watchdog Reset periph_nreset Only if WDRPROC = 0 NRST (nrst_out) EXTERNAL RESET LENGTH 8 cycles (ERSTL=2) 14.4.6 Reset State Priorities The Reset State Manager manages the following priorities between the different reset sources, given in descending order: •...

- Page 116 14-9). . Reading the RSTC_SR status register resets the URSTS bit . Figure 14-9. Reset Controller Status and Interrupt read Peripheral Access RSTC_SR 2 cycle 2 cycle resynchronization resynchronization NRST NRSTL URSTS rstc_irq if (URSTEN = 0) and (URSTIEN = 1) SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 117 SAM9X25 SAM9X25 14.5 Reset Controller (RSTC) User Interface Table 14-1. Register Mapping Offset Register Name Access Reset Back-up Reset 0x00 Control Register RSTC_CR Write-only 0x04 Status Register RSTC_SR Read-only 0x0000_0001 0x0000_0000 0x08 Mode Register RSTC_MR Read-write 0x0000_0000 Note: 1. The reset value of RSTC_SR either reports a General Reset or a Wake-up Reset depending on last rising power supply.

- Page 118 • EXTRST: External Reset 0 = No effect. 1 = If KEY is correct, asserts the NRST pin. • KEY: Password Should be written at value 0xA5. Writing any other value in this field aborts the write operation. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 119 0 = No software command is being performed by the reset controller. The reset controller is ready for a software command. 1 = A software reset command is being performed by the reset controller. The reset controller is busy. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 120 Slow Clock cycles. This allows assertion duration to be programmed between 60 μs and 2 seconds. • KEY: Password Should be written at value 0xA5. Writing any other value in this field aborts the write operation. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 121 SAM9X25 SAM9X25 15. Real-time Clock (RTC) 15.1 Description The Real-time Clock (RTC) peripheral is designed for very low power consumption. It combines a complete time-of-day clock with alarm and a two-hundred-year Gregorian calen- dar, complemented by a programmable periodic interrupt. The alarm and calendar registers are accessed by a 32-bit data bus.

- Page 122 Each of these fields can be enabled or disabled to match the alarm condition: • If all the fields are enabled, an alarm flag is generated (the corresponding flag is asserted and an interrupt generated if enabled) at a given month, date, hour/minute/second. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 123 SAM9X25 SAM9X25 • If only the “seconds” field is enabled, then an alarm is generated every minute. Depending on the combination of fields enabled, a large number of possibilities are available to the user ranging from minutes to 365/366 days.

- Page 124 Set UPDTIM and/or UPDCAL bit(s) in RTC_CR Read RTC_SR Polling or IRQ (if enabled) ACKUPD = 1 ? Clear ACKUPD bit in RTC_SCCR Update Time and/or Calendar values in RTC_TIMR/RTC_CALR Clear UPDTIM and/or UPDCAL bit in RTC_CR SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 125 SAM9X25 SAM9X25 15.6 Real Time Clock (RTC) User Interface Table 15-1. Register Mapping Offset Register Name Access Reset 0x00 Control Register RTC_CR Read-write 0x04 Mode Register RTC_MR Read-write 0x08 Time Register RTC_TIMR Read-write 0x0C Calendar Register RTC_CALR Read-write 0x01210720 0x10...

-

Page 126: Rtc_Cr

The event that generates the flag CALEV in RTC_SR depends on the value of CALEVSEL Value Name Description WEEK Week change (every Monday at time 00:00:00) MONTH Month change (every 01 of each month at time 00:00:00) YEAR Year change (every January 1 at time 00:00:00) – SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 127: Rtc_Mr

SAM9X25 SAM9X25 15.6.2 RTC Mode Register Name: RTC_MR Address: 0xFFFFFEB4 Access: Read-write – – – – – – – – – – – – – – – – – – – – – – – – – – – –... -

Page 128: Rtc_Timr

The range that can be set is 1 - 12 (BCD) in 12-hour mode or 0 - 23 (BCD) in 24-hour mode. • AMPM: Ante Meridiem Post Meridiem Indicator This bit is the AM/PM indicator in 12-hour mode. 0 = AM. 1 = PM. All non-significant bits read zero. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 129: Rtc_Calr

SAM9X25 SAM9X25 15.6.4 RTC Calendar Register Name: RTC_CALR Address: 0xFFFFFEBC Access: Read-write – – DATE MONTH YEAR – CENT • CENT: Current Century The range that can be set is 19 - 20 (BCD). The lowest four bits encode the units. The higher bits encode the tens. -

Page 130: Rtc_Timalr

This field is the alarm field corresponding to the BCD-coded hour counter. • AMPM: AM/PM Indicator This field is the alarm field corresponding to the BCD-coded hour counter. • HOUREN: Hour Alarm Enable 0 = The hour-matching alarm is disabled. 1 = The hour-matching alarm is enabled. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 131: Rtc_Calalr

SAM9X25 SAM9X25 15.6.6 RTC Calendar Alarm Register Name: RTC_CALALR Address: 0xFFFFFEC4 Access: Read-write DATEEN – DATE MTHEN – – MONTH – – – – – – – – – – – – – – – – • MONTH: Month Alarm This field is the alarm field corresponding to the BCD-coded month counter. -

Page 132: Rtc_Sr

1 = At least one calendar event has occurred since the last clear. The calendar event is selected in the CALEVSEL field in RTC_CR and can be any one of the following events: week change, month change and year change. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11... -

Page 133: Rtc_Sccr

SAM9X25 SAM9X25 15.6.8 RTC Status Clear Command Register Name: RTC_SCCR Address: 0xFFFFFECC Access: Write-only – – – – – – – – – – – – – – – – – – – – – – – – – –... -

Page 134: Rtc_Ier

• TIMEN: Time Event Interrupt Enable 0 = No effect. 1 = The selected time event interrupt is enabled. • CALEN: Calendar Event Interrupt Enable 0 = No effect. • 1 = The selected calendar event interrupt is enabled. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 135: Rtc_Idr

SAM9X25 SAM9X25 15.6.10 RTC Interrupt Disable Register Name: RTC_IDR Address: 0xFFFFFED4 Access: Write-only – – – – – – – – – – – – – – – – – – – – – – – – – – –... -

Page 136: Rtc_Imr

0 = The selected time event interrupt is disabled. 1 = The selected time event interrupt is enabled. • CAL: Calendar Event Interrupt Mask 0 = The selected calendar event interrupt is disabled. 1 = The selected calendar event interrupt is enabled. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 137: Rtc_Ver

SAM9X25 SAM9X25 15.6.12 RTC Valid Entry Register Name: RTC_VER Address: 0xFFFFFEDC Access: Read-only – – – – – – – – – – – – – – – – – – – – – – – – – – –... - Page 138 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 139 SAM9X25 SAM9X25 16. Periodic Interval Timer (PIT) 16.1 Description The Periodic Interval Timer (PIT) provides the operating system’s scheduler interrupt. It is designed to offer maximum accuracy and efficient management, even for systems with long response time. 16.2 Embedded Characteristics •...

- Page 140 PIT counting. After the PIT Enable bit is reset (PITEN= 0), the CPIV goes on counting until the PIV value is reached, and is then reset. PIT restarts counting, only if the PITEN is set again. The PIT is stopped when the core enters debug state. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 141 SAM9X25 SAM9X25 Figure 16-2. Enabling/Disabling PIT with PITEN APB cycle APB cycle restarts MCK Prescaler MCK Prescaler PITEN CPIV PIV - 1 PICNT PITS (PIT_SR) APB Interface read PIT_PIVR 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 142 Table 16-1. Register Mapping Offset Register Name Access Reset 0x00 Mode Register PIT_MR Read-write 0x000F_FFFF 0x04 Status Register PIT_SR Read-only 0x0000_0000 0x08 Periodic Interval Value Register PIT_PIVR Read-only 0x0000_0000 0x0C Periodic Interval Image Register PIT_PIIR Read-only 0x0000_0000 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 143 SAM9X25 SAM9X25 16.5.1 Periodic Interval Timer Mode Register Name: PIT_MR Address: 0xFFFFFE30 Access: Read-write – – – – – – PITIEN PITEN – – – – • PIV: Periodic Interval Value Defines the value compared with the primary 20-bit counter of the Periodic Interval Timer (CPIV). The period is equal to (PIV + 1).

- Page 144 SAM9X25 SAM9X25 16.5.2 Periodic Interval Timer Status Register Name: PIT_SR Address: 0xFFFFFE34 Access: Read-only – – – – – – – – – – – – – – – – – – – – – – – – – –...

- Page 145 SAM9X25 SAM9X25 16.5.3 Periodic Interval Timer Value Register Name: PIT_PIVR Address: 0xFFFFFE38 Access: Read-only PICNT PICNT CPIV CPIV CPIV Reading this register clears PITS in PIT_SR. • CPIV: Current Periodic Interval Value Returns the current value of the periodic interval timer.

- Page 146 CPIV CPIV • CPIV: Current Periodic Interval Value Returns the current value of the periodic interval timer. • PICNT: Periodic Interval Counter Returns the number of occurrences of periodic intervals since the last read of PIT_PIVR. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 147 SAM9X25 SAM9X25 17. Watchdog Timer (WDT) 17.1 Description The Watchdog Timer can be used to prevent system lock-up if the software becomes trapped in a deadlock. It features a 12-bit down counter that allows a watchdog period of up to 16 seconds (slow clock at 32.768 kHz).

- Page 148 If a reset is generated or if WDT_SR is read, the status bits are reset, the interrupt is cleared, and the “wdt_fault” signal to the reset controller is deasserted. Writing the WDT_MR reloads and restarts the down counter. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 149 SAM9X25 SAM9X25 While the processor is in debug state or in idle mode, the counter may be stopped depending on the value programmed for the bits WDIDLEHLT and WDDBGHLT in the WDT_MR. Figure 17-2. Watchdog Behavior Watchdog Error Watchdog Underflow...

- Page 150 17.5 Watchdog Timer (WDT) User Interface Table 17-1. Register Mapping Offset Register Name Access Reset 0x00 Control Register WDT_CR Write-only 0x04 Mode Register WDT_MR Read-write Once 0x3FFF_2FFF 0x08 Status Register WDT_SR Read-only 0x0000_0000 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 151 SAM9X25 SAM9X25 17.5.1 Watchdog Timer Control Register Name: WDT_CR Address: 0xFFFFFE40 Access: Write-only – – – – – – – – – – – – – – – – – – – – – – – WDRSTT • WDRSTT: Watchdog Restart 0: No effect.

- Page 152 1: The Watchdog stops when the processor is in debug state. • WDIDLEHLT: Watchdog Idle Halt 0: The Watchdog runs when the system is in idle mode. 1: The Watchdog stops when the system is in idle state. • WDDIS: Watchdog Disable SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 153 SAM9X25 SAM9X25 0: Enables the Watchdog Timer. 1: Disables the Watchdog Timer. 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 154 1: At least one Watchdog underflow occurred since the last read of WDT_SR. • WDERR: Watchdog Error 0: No Watchdog error occurred since the last read of WDT_SR. 1: At least one Watchdog error occurred since the last read of WDT_SR. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 155 SAM9X25 SAM9X25 18. Shutdown Controller (SHDWC) 18.1 Description The Shutdown Controller controls the power supplies VDDIO and VDDCORE and the wake-up detection on debounced input lines. 18.2 Embedded Characteristics • Shutdown and Wake-up Logic – Software Assertion of the SHDW Output Pin –...

- Page 156 Shutdown Control Register (SHDW_CR) with the bit SHDW at 1. The shutdown is taken into account only 2 slow clock cycles after the write of SHDW_CR. This register is password-protected and so the value written SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 157 SAM9X25 SAM9X25 should contain the correct key for the command to be taken into account. As a result, the system should be powered down. A level change on WKUP0 is used as wake-up. Wake-up is configured in the Shutdown Mode Register (SHDW_MR).

- Page 158 18.7 Shutdown Controller (SHDWC) User Interface Table 18-2. Register Mapping Offset Register Name Access Reset 0x00 Shutdown Control Register SHDW_CR Write-only 0x04 Shutdown Mode Register SHDW_MR Read-write 0x0000_0003 0x08 Shutdown Status Register SHDW_SR Read-only 0x0000_0000 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 159 SAM9X25 SAM9X25 18.7.1 Shutdown Control Register Name: SHDW_CR Address: 0xFFFFFE10 Access: Write-only – – – – – – – – – – – – – – – – – – – – – – – SHDW • SHDW: Shutdown Command 0 = No effect.

- Page 160 (CPTWK x 16 + 1) Slow Clock cycles after the event on WKUP. • RTCWKEN: Real-time Clock Wake-up Enable 0 = The RTC Alarm signal has no effect on the Shutdown Controller. 1 = The RTC Alarm signal forces the de-assertion of the SHDN pin. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 161 • RTCWK: Real-time Clock Wake-up 0 = No wake-up alarm from the RTC occurred since the last read of SHDW_SR. 1 = At least one wake-up alarm from the RTC occurred since the last read of SHDW_SR. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 162 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 163 SAM9X25 SAM9X25 19. General Purpose Backup Registers (GPBR) 19.1 Description The System Controller embeds Four general-purpose backup registers. 19.2 Embedded Characteristics • Four 32-bit General Purpose Backup Registers 19.3 General Purpose Backup Registers (GPBR) User Interface Table 19-1. Register Mapping...

- Page 164 19.3.1 General Purpose Backup Register x Name: SYS_GPBRx Address: 0xFFFFFE60 [0], 0xFFFFFE64 [1], 0xFFFFFE68 [2], 0xFFFFFE6C [3] Access: Read-write GPBR_VALUEx GPBR_VALUEx GPBR_VALUEx GPBR_VALUEx • GPBR_VALUEx: Value of GPBR x SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 165 SAM9X25 SAM9X25 20. Slow Clock Controller (SCKC) 20.1 Description The System Controller embeds a Slow Clock Controller. The slow clock can be generated either by an external 32,768 Hz crystal oscillator or by the on- chip 32 kHz RC oscillator. The 32,768 Hz crystal oscillator can be bypassed by setting the bit OSC32BYP to accept an external slow clock on XIN32.

- Page 166 • Switch from 32,768 Hz oscillator to internal RC by setting the bit OSCSEL to 0. • Wait 5 slow clock cycles for internal resynchronization. • Disable the 32,768 Hz oscillator by setting the bit OSC32EN to 0. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 167 SAM9X25 SAM9X25 20.4 Slow Clock Configuration (SCKC) User Interface Table 20-1. Register Mapping Offset Register Name Access Reset Slow Clock Configuration Register SCKC_CR Read-write 0x0000_0001 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 168 SAM9X25 SAM9X25 20.4.1 Slow Clock Configuration Register Name: SCKC_CR Address: 0xFFFFFE50 Access: Read-write Reset: 0x0000_0001 – – – – – – – – – – – – – – – – – – – – – – – – –...

- Page 169 SAM9X25 SAM9X25 21. Clock Generator (CKGR) 21.1 Description The Clock Generator User Interface is embedded within the Power Management Controller and is described in Section 22.13 ”Power Management Controller (PMC) User Interface”. However, the Clock Generator registers are named CKGR_.

- Page 170 The internal 32 kHz RC oscillator and the 32,768 Hz oscillator can be enabled by setting to 1, respectively, RCEN bit and OSC32EN bit in the System Controller user interface. The OSCSEL command selects the slow clock source. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 171 SAM9X25 SAM9X25 Figure 21-2. Slow Clock Clock Generator RCEN On Chip RC OSC Slow Clock SLCK Slow Clock XIN32 Oscillator XOUT32 OSCSEL OSC32EN OSC32BYP RCEN, OSC32EN,OSCSEL and OSC32BYP bits are located in the Slow Clock Control Register (SCKCR) located at address 0xFFFFFE50 in the backed up part of the System Controller and so are preserved while VDDBU is present.

- Page 172 • Switch from 32768 Hz oscillator to internal RC by setting the bit OSCSEL to 0. • Wait 5 slow clock cycles for internal resynchronization. • Disable the 32768 Hz oscillator by setting the bit OSC32EN to 0. • Switch the master clock back to the slow clock domain SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 173 SAM9X25 SAM9X25 21.4.4 Slow Clock Configuration Register Name: SCKCR Address: 0xFFFFFE50 Access: Read-write Reset Value: 0x0000_0001 – – – – – – – – – – – – – – – – – – – – – – – –...

- Page 174 12 MHz RC oscillator. This fast RC oscillator allows the processor to start or restart in a few microseconds when 12 MHz internal RC is selected. The 12 MHz crystal oscillator can be bypassed by setting the bit MOSCXTBY to accept an exter- nal main clock on XIN. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 175 SAM9X25 SAM9X25 Figure 21-4. Main Clock Selection MOSCRCEN On Chip 12M RC OSC Main Clock Main Clock Oscillator XOUT MOSCSEL MOSCXTEN MOSCXTBY MOSCRCEN, MOSCXTEN, MOSCSEL and MOSCXTBY bits are located in the PMC Clock Generator Main Oscillator Register (CKGR_MOR). After a VDDBU power on reset, the default configuration is MOSCRCEN = 1, MOSCXTEN = 0 and MOSCSEL = 0, the 12 MHz RC oscillator is started as Main clock.

- Page 176 (PMC_IER) can trigger an interrupt to the processor. 21.6.6 3 to 20 MHz Crystal Oscillator After reset, the 3 to 20 MHz Crystal Oscillator is disabled and it is not selected as the source of MAINCK. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 177 SAM9X25 SAM9X25 The user can select the 3 to 20 MHz crystal oscillator to be the source of MAINCK, as it provides a more accurate frequency. The software enables or disables the main oscillator so as to reduce power consumption by clearing the MOSCXTEN bit in the Main Oscillator Register (CKGR_MOR).

- Page 178 MAINCK, the 12 MHz frequency must also be selected because the UTMI PLL multiplier contains a built-in multiplier of x 40 to obtain the USB High Speed 480 MHz. A 12 MHz crystal is needed to use the USB. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 179 SAM9X25 SAM9X25 Figure 21-7. UTMI PLL Block Diagram UPLLEN MAINCK UTMI PLL UPLLCK UPLLCOUNT UTMI PLL SLCK LOCKU Counter Whenever the UTMI PLL is enabled by writing UPLLEN in CKGR_UCKR, the LOCKU bit in PMC_SR is automatically cleared. The values written in the PLLCOUNT field in CKGR_UCKR are loaded in the UTMI PLL counter.

- Page 180 • Slow Clock Mode, processor and peripherals running at low frequency • Standby Mode, mix of Idle and Backup Mode, peripheral running at low frequency, processor stopped waiting for an interrupt • Backup Mode, Main Power Supplies off, VDDBU powered by a battery SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 181 SAM9X25 SAM9X25 22.3 Master Clock Controller The Master Clock Controller provides selection and division of the Master Clock (MCK). MCK is the clock provided to all the peripherals and the memory controller. The Master Clock is selected from one of the clocks provided by the Clock Generator. Selecting the Slow Clock provides a Slow Clock signal to the whole device.

- Page 182 Note: The ARM Wait for Interrupt mode is entered by means of CP15 coprocessor operation. Refer to the Atmel application note, Optimizing Power Consumption for AT91SAM9261-based Systems, http://www.atmel.com/dyn/resources/prod_documents/doc6217.pdf. When the Processor Clock is disabled, the current instruction is finished before the clock is stopped, but this does not prevent data transfers from other masters of the system bus.

- Page 183 SAM9X25 SAM9X25 22.6 USB Device and Host Clocks The USB Device and Host High Speed ports clocks are controlled by the UDPHS and UHPHS bits in PMC_PCER. To save power on this peripheral when they are is not used, the user can set these bits in PMC_PCDR.

- Page 184 PMC_SR register to be set. This can be done either by polling the status register or by wait- ing the interrupt line to be raised if the associated interrupt to MOSCS has been enabled in the PMC_IER register. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 185 SAM9X25 SAM9X25 2. Setting PLLA and divider: All parameters needed to configure PLLA and the divider are located in the CKGR_PLLAR register. The DIVA field is used to control the divider itself. A value between 0 and 255 can be pro- grammed.

- Page 186 LOCK goes high and MCKRDY is set. While PLLA is unlocked, the Master Clock selection is automatically changed to Main Clock. For further information, see Section 22.12.2. “Clock Switching Waveforms” on page 189. Code Example: write_register(PMC_MCKR,0x00000001) wait (MCKRDY=1) write_register(PMC_MCKR,0x00000011) SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 187 SAM9X25 SAM9X25 wait (MCKRDY=1) The Master Clock is main clock divided by 16. The Processor Clock is the Master Clock. 5. Selection of Programmable clocks Programmable clocks are controlled via registers; PMC_SCER, PMC_SCDR and PMC_SCSR. Programmable clocks can be enabled and/or disabled via the PMC_SCER and PMC_SCDR registers.

- Page 188 4 x SLCK + PLLACOUNT x SLCK 1.5 x PLLA Clock 3 x UPLL Clock + 2.5 x UPLL Clock + UPLL Clock 4 x SLCK + 4 x SLCK + 1.5 x UPLL Clock UPLLCOUNT x SLCK SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 189 SAM9X25 SAM9X25 22.12.2 Clock Switching Waveforms Figure 22-3. Switch Master Clock from Slow Clock to PLL Clock Slow Clock PLL Clock LOCK MCKRDY Master Clock Write PMC_MCKR Figure 22-4. Switch Master Clock from Main Clock to Slow Clock Slow Clock...

- Page 190 PLLA Clock LOCKA MCKRDY Master Clock Slow Clock Write CKGR_PLLAR Figure 22-6. Programmable Clock Output Programming PLL Clock PCKRDY PCKx Output Write PMC_PCKx PLL Clock is selected Write PMC_SCER PCKx is enabled Write PMC_SCDR PCKx is disabled SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 191 SAM9X25 SAM9X25 22.13 Power Management Controller (PMC) User Interface Table 22-3. Register Mapping Offset Register Name Access Reset 0x0000 System Clock Enable Register PMC_SCER Write-only N.A. 0x0004 System Clock Disable Register PMC_SCDR Write-only N.A. 0x0008 System Clock Status Register PMC_SCSR...

-

Page 192: Pmc_Scer

• UDP: USB Device Clock Enable 0 = No effect. 1 = Enables the USB Device clock. • PCKx: Programmable Clock x Output Enable 0 = No effect. 1 = Enables the corresponding Programmable Clock output. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 193: Pmc_Scdr

SAM9X25 SAM9X25 22.13.2 PMC System Clock Disable Register Name: PMC_SCDR Address: 0xFFFFFC04 Access: Write-only – – – – – – – – – – – – – – – – – – – – – – PCK1 PCK0 – SMDCK –... -

Page 194: Pmc_Scsr

0 = The USB Device clock is disabled. 1 = The USB Device clock is enabled. • PCKx: Programmable Clock x Output Status 0 = The corresponding Programmable Clock output is disabled. 1 = The corresponding Programmable Clock output is enabled. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... - Page 195 SAM9X25 SAM9X25 22.13.4 PMC Peripheral Clock Enable Register Name: PMC_PCER Address: 0xFFFFFC10 Access: Write-only PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6...

- Page 196 PID2 • PIDx: Peripheral Clock x Disable 0 = No effect. 1 = Disables the corresponding peripheral clock. Note: PID2 to PID31 refer to identifiers as defined in the section “Peripheral Identifiers” in the product datasheet. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 197 SAM9X25 SAM9X25 22.13.6 PMC Peripheral Clock Status Register Name: PMC_PCSR Address: 0xFFFFFC18 Access: Read-only PID31 PID30 PID29 PID28 PID27 PID26 PID25 PID24 PID23 PID22 PID21 PID20 PID19 PID18 PID17 PID16 PID15 PID14 PID13 PID12 PID11 PID10 PID9 PID8 PID7 PID6...

-

Page 198: Ckgr_Uckr

• BIASEN: UTMI BIAS Enable 0 = The UTMI BIAS is disabled. 1 = The UTMI BIAS is enabled. • BIASCOUNT: UTMI BIAS Start-up Time Specifies the number of Slow Clock cycles for the UTMI BIAS start-up time. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 199: Ckgr_Mor

SAM9X25 SAM9X25 22.13.8 PMC Clock Generator Main Oscillator Register Name: CKGR_MOR Address: 0xFFFFFC20 Access: Read-write – – – – – – CFDEN MOSCSEL MOSCXTST – – – – MOSCRCEN – MOSCXTBY MOSCXTEN • KEY: Password Should be written at value 0x37. Writing any other value in this field aborts the write operation. -

Page 200: Ckgr_Mcfr

Gives the number of Main Clock cycles within 16 Slow Clock periods. • MAINFRDY: Main Clock Ready 0 = MAINF value is not valid or the Main Oscillator is disabled. 1 = The Main Oscillator has been enabled previously and MAINF value is available. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 201: Ckgr_Pllar

SAM9X25 SAM9X25 22.13.10 PMC Clock Generator PLLA Register Name: CKGR_PLLAR Address: 0xFFFFFC28 Access: Read-write – – – – MULA MULA OUTA PLLACOUNT DIVA Possible limitations on PLL input frequencies and multiplier factors should be checked before using the PMC. Warning: Bit 29 must always be set to 1 when programming the CKGR_PLLAR register. - Page 202 SysClk DDR is equal to 2 x MCK. DDRCK is equal to MCK. Master Clock is Prescaler Output Clock divided by 3. PCK_DIV3 SysClk DDR is equal to 2 x MCK. DDRCK is equal to MCK. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 203 SAM9X25 SAM9X25 • PLLADIV2: PLLA divisor by 2 Value Name Description NOT_DIV2 PLLA clock frequency is divided by 1. DIV2 PLLA clock frequency is divided by 2. 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 204 • USBS: USB OHCI Input Clock Selection 0 = USB Clock Input is PLLA 1 = USB Clock Input is UPLL • USBDIV: Divider for USB OHCI Clock. USB Clock is Input clock divided by USBDIV+1 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

-

Page 205: Pmc_Smd

SAM9X25 SAM9X25 22.13.13 PMC SMD Clock Register Name: PMC_SMD Address: 0xFFFFFC3C Access: Read-write – – – – – – – – – – – – – – – – – – – SMDDIV – – – – – – –... - Page 206 Selected clock divided by 2 CLOCK_DIV4 Selected clock divided by 4 CLOCK_DIV8 Selected clock divided by 8 CLOCK_DIV16 Selected clock divided by 16 CLOCK_DIV32 Selected clock divided by 32 CLOCK_DIV64 Selected clock divided by 64 Reserved Reserved SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

-

Page 207: Pmc_Ier

SAM9X25 SAM9X25 22.13.15 PMC Interrupt Enable Register Name: PMC_IER Address: 0xFFFFFC60 Access: Write-only – – – – – – – – – – – – – CFDEV MOSCRCS MOSCSELS – – – – – – PCKRDY1 PCKRDY0 – LOCKU –... -

Page 208: Pmc_Idr

• LOCKU: UTMI PLL Lock Interrupt Enable • PCKRDYx: Programmable Clock Ready x Interrupt Disable • MOSCSELS: Main Oscillator Selection Status Interrupt Disable • MOSCRCS: Main On-Chip RC Status Interrupt Disable • CFDEV: Clock Failure Detector Event Interrupt Disable SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... -

Page 209: Pmc_Sr

SAM9X25 SAM9X25 22.13.17 PMC Status Register Name: PMC_SR Address: 0xFFFFFC68 Access: Read-only – – – – – – – – – – – CFDS CFDEV MOSCRCS MOSCSELS – – – – – – PCKRDY1 PCKRDY0 OSCSELS LOCKU – – MCKRDY... - Page 210 1 = A clock failure of the main on-chip RC oscillator clock is detected. • FOS: Clock Failure Detector Fault Output Status 0 = The fault output of the clock failure detector is inactive. 1 = The fault output of the clock failure detector is active. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

-

Page 211: Pmc_Imr

SAM9X25 SAM9X25 22.13.18 PMC Interrupt Mask Register Name: PMC_IMR Address: 0xFFFFFC6C Access: Read-only – – – – – – – – – – – – – CFDEV MOSCRCS MOSCSELS – – – – – – PCKRDY1 PCKRDY0 – – –... -

Page 212: Pmc_Pllicpr

– – – – – ICPLLA • ICPLLA: Charge Pump Current To optimize clock performance, this field must be programmed as specified in “PLL A Characteristics” in the Electrical Char- acteristics section of the product datasheet. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... - Page 213 SAM9X25 SAM9X25 22.13.20 PMC Write Protect Mode Register Name: PMC_WPMR Address: 0xFFFFFCE4 Access: Read-write Reset: Table 22-3 WPKEY WPKEY WPKEY — — — — — — — WPEN • WPEN: Write Protect Enable 0 = Disables the Write Protect if WPKEY corresponds to 0x504D43 (“PMC” in ASCII).

-

Page 214: Pmc_Wpsr

WPVSRC. • WPVSRC: Write Protect Violation Source When WPVS is active, this field indicates the write-protected register (through address offset or code) in which a write access has been attempted. Reading PMC_WPSR automatically clears all fields. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11... - Page 215 SAM9X25 SAM9X25 22.13.22 PMC Peripheral Control Register Name: PMC_PCR Address: 0xFFFFFD0C Access: Read-write — — — — — — — — — — — — — — — — — — — — — — • PID: Peripheral ID Only the following Peripheral IDs can have a DIV value other than 0: PID2, PID3, PID5 to PID11, PID13 to PID19, PID28 to PID30.

- Page 216 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 217 SAM9X25 SAM9X25 23. Parallel Input/Output Controller (PIO) 23.1 Description The Parallel Input/Output Controller (PIO) manages up to 32 fully programmable input/output lines. Each I/O line may be dedicated as a general-purpose I/O or be assigned to a function of an embedded peripheral. This assures effective optimization of the pins of a product.

- Page 218 Up to 32 pins Up to 32 peripheral IOs Embedded Peripheral PIN 31 Figure 23-2. Application Block Diagram On-Chip Peripheral Drivers Keyboard Driver Control & Command Driver On-Chip Peripherals PIO Controller Keyboard Driver General Purpose I/Os External Devices SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 219 SAM9X25 SAM9X25 23.4 Product Dependencies 23.4.1 Pin Multiplexing Each pin is configurable, according to product definition as either a general-purpose I/O line only, or as an I/O line multiplexed with one or two peripheral I/Os. As the multiplexing is hard- ware defined and thus product-dependent, the hardware designer and programmer must carefully determine the configuration of the PIO controllers required by their application.

- Page 220 PIO_ISR[0] (Up to 32 possible inputs) EVENT DETECTOR Programmable PIO Clock Glitch PIO Interrupt Resynchronization Slow Clock Debouncing Stage Clock Filter PIO_IER[0] Divider PIO_SCDR PIO_IMR[0] PIO_IDR[0] PIO_IFER[0] PIO_IFSR[0] PIO_ISR[31] PIO_IFSCER[0] PIO_IFDR[0] PIO_IFSCSR[0] PIO_IER[31] PIO_IFSCDR[0] PIO_IMR[31] PIO_IDR[31] SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 221 SAM9X25 SAM9X25 23.5.1 Pull-up and Pull-down Resistor Control Each I/O line is designed with an embedded pull-up resistor and an embedded pull-down resis- tor. The pull-up resistor can be enabled or disabled by writing respectively PIO_PUER (Pull-up Enable Register) and PIO_PUDR (Pull-up Disable Resistor). Writing in these registers results in setting or clearing the corresponding bit in PIO_PUSR (Pull-up Status Register).

- Page 222 I/O line which is driven low only by each device. An external pull-up resistor (or enabling of the internal one) is generally required to guar- antee a high level on the line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11...

- Page 223 SAM9X25 SAM9X25 The Multi Drive feature is controlled by PIO_MDER (Multi-driver Enable Register) and PIO_MDDR (Multi-driver Disable Register). The Multi Drive can be selected whether the I/O line is controlled by the PIO controller or assigned to a peripheral function. PIO_MDSR (Multi-driver Status Register) indicates the pins that are configured to support external drivers.

- Page 224 1.5 cycles Pin Level 1 cycle 1 cycle 1 cycle 1 cycle PIO_PDSR if PIO_IFSR = 0 2 cycles 1 cycle up to 2.5 cycles PIO_PDSR if PIO_IFSR = 1 up to 2 cycles SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 225 SAM9X25 SAM9X25 Figure 23-6. Input Debouncing Filter Timing PIO_IFCSR = 1 Divided Slow Clock Pin Level up to 2 cycles Tmck up to 2 cycles Tmck PIO_PDSR if PIO_IFSR = 0 1 cycle Tdiv_slclk 1 cycle Tdiv_slclk up to 1.5 cycles Tdiv_slclk...

- Page 226 • High Level on PIO line 4 • High Level on PIO line 5 • Falling edge on PIO line 6 • Rising edge on PIO line 7 • Any edge on the other lines The configuration required is described below. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 227 SAM9X25 SAM9X25 23.5.10.2 Interrupt Mode Configuration All the interrupt sources are enabled by writing 32’hFFFF_FFFF in PIO_IER. Then the Additional Interrupt Mode is enabled for line 0 to 7 by writing 32’h0000_00FF in PIO_AIMER. 23.5.10.3 Edge or Level Detection Configuration Lines 3, 4 and 5 are configured in Level detection by writing 32’h0000_0038 in PIO_LSR.

- Page 228 23.5.14 Programmable Schmitt Trigger It is possible to configure each input for the Schmitt Trigger. By default the Schmitt trigger is ™ active. Disabling the Schmitt Trigger is requested when using the QTouch Library. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 229 SAM9X25 SAM9X25 23.5.15 Write Protection Registers To prevent any single software error that may corrupt PIO behavior, certain address spaces can be write-protected by setting the WPEN bit in the “PIO Write Protect Mode Register” (PIO_WPMR). If a write access to the protected registers is detected, then the WPVS flag in the PIO Write Pro- tect Status Register (PIO_WPSR) is set and the field WPVSRC indicates in which register the write access has been attempted.

- Page 230 0x0000_00FF PIO_ODR 0xFFFF_FF00 PIO_IFER 0x0000_0F00 PIO_IFDR 0xFFFF_F0FF PIO_SODR 0x0000_0000 PIO_CODR 0x0FFF_FFFF PIO_IER 0x0F00_0F00 PIO_IDR 0xF0FF_F0FF PIO_MDER 0x0000_000F PIO_MDDR 0xFFFF_FFF0 PIO_PUDR 0xFFF0_00F0 PIO_PUER 0x000F_FF0F PIO_PPDDR 0xFF0F_FFFF PIO_PPDER 0x00F0_0000 PIO_ABCDSR1 0xF0F0_0000 PIO_ABCDSR2 0xFF00_0000 PIO_OWER 0x0000_000F PIO_OWDR 0x0FFF_ FFF0 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 231 SAM9X25 SAM9X25 23.7 Parallel Input/Output Controller (PIO) User Interface Each I/O line controlled by the PIO Controller is associated with a bit in each of the PIO Control- ler User Interface registers. Each register is 32 bits wide. If a parallel I/O line is not defined, writing to the corresponding bits has no effect.

- Page 232 Read-only 0x00000000 0x00E4 Write Protect Mode Register PIO_WPMR Read-write 0x00E8 Write Protect Status Register PIO_WPSR Read-only 0x00EC Reserved 0x00F8 0x0100 Schmitt Trigger Register PIO_SCHMITT Read-write 0x00000000 0x0104- Reserved 0x010C 0x0110 IO Delay Register PIO_DELAYR Read-write 0x00000000 SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 233 SAM9X25 SAM9X25 Table 23-2. Register Mapping (Continued) Offset Register Name Access Reset 0x0114 I/O Drive Register 1 PIO_DRIVER1 Read-write 0x00000000 0x0118 I/O Drive Register 2 PIO_DRIVER2 Read-write 0x00000000 0x011C Reserved Notes: 1. Reset value depends on the product implementation. 2. PIO_ODSR is Read-only or Read/Write depending on PIO_OWSR I/O lines.

- Page 234 This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: PIO Disable 0: No effect. 1: Disables the PIO from controlling the corresponding pin (enables peripheral control of the pin). SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 235 SAM9X25 SAM9X25 23.7.3 PIO Status Register Name: PIO_PSR Address: 0xFFFFF408 (PIOA), 0xFFFFF608 (PIOB), 0xFFFFF808 (PIOC), 0xFFFFFA08 (PIOD) Access: Read-only • P0-P31: PIO Status 0: PIO is inactive on the corresponding I/O line (peripheral is active). 1: PIO is active on the corresponding I/O line (peripheral is inactive).

- Page 236 PIO Output Status Register Name: PIO_OSR Address: 0xFFFFF418 (PIOA), 0xFFFFF618 (PIOB), 0xFFFFF818 (PIOC), 0xFFFFFA18 (PIOD) Access: Read-only • P0-P31: Output Status 0: The I/O line is a pure input. 1: The I/O line is enabled in output. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 237 SAM9X25 SAM9X25 23.7.7 PIO Input Filter Enable Register Name: PIO_IFER Address: 0xFFFFF420 (PIOA), 0xFFFFF620 (PIOB), 0xFFFFF820 (PIOC), 0xFFFFFA20 (PIOD) Access: Write-only This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Input Filter Enable 0: No effect.

- Page 238 PIO Set Output Data Register Name: PIO_SODR Address: 0xFFFFF430 (PIOA), 0xFFFFF630 (PIOB), 0xFFFFF830 (PIOC), 0xFFFFFA30 (PIOD) Access: Write-only • P0-P31: Set Output Data 0: No effect. 1: Sets the data to be driven on the I/O line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 239 SAM9X25 SAM9X25 23.7.11 PIO Clear Output Data Register Name: PIO_CODR Address: 0xFFFFF434 (PIOA), 0xFFFFF634 (PIOB), 0xFFFFF834 (PIOC), 0xFFFFFA34 (PIOD) Access: Write-only • P0-P31: Clear Output Data 0: No effect. 1: Clears the data to be driven on the I/O line.

- Page 240 PIO Interrupt Enable Register Name: PIO_IER Address: 0xFFFFF440 (PIOA), 0xFFFFF640 (PIOB), 0xFFFFF840 (PIOC), 0xFFFFFA40 (PIOD) Access: Write-only • P0-P31: Input Change Interrupt Enable 0: No effect. 1: Enables the Input Change Interrupt on the I/O line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 241 SAM9X25 SAM9X25 23.7.15 PIO Interrupt Disable Register Name: PIO_IDR Address: 0xFFFFF444 (PIOA), 0xFFFFF644 (PIOB), 0xFFFFF844 (PIOC), 0xFFFFFA44 (PIOD) Access: Write-only • P0-P31: Input Change Interrupt Disable 0: No effect. 1: Disables the Input Change Interrupt on the I/O line. 23.7.16...

- Page 242 Access: Write-only This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Multi Drive Enable. 0: No effect. 1: Enables Multi Drive on the I/O line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 243 SAM9X25 SAM9X25 23.7.19 PIO Multi-driver Disable Register Name: PIO_MDDR Address: 0xFFFFF454 (PIOA), 0xFFFFF654 (PIOB), 0xFFFFF854 (PIOC), 0xFFFFFA54 (PIOD) Access: Write-only This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Multi Drive Disable.

- Page 244 This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Pull Up Enable. 0: No effect. 1: Enables the pull up resistor on the I/O line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 245 SAM9X25 SAM9X25 23.7.23 PIO Pull Up Status Register Name: PIO_PUSR Address: 0xFFFFF468 (PIOA), 0xFFFFF668 (PIOB), 0xFFFFF868 (PIOC), 0xFFFFFA68 (PIOD) Access: Read-only • P0-P31: Pull Up Status. 0: Pull Up resistor is enabled on the I/O line. 1: Pull Up resistor is disabled on the I/O line.

- Page 246 1: Assigns the I/O line to the Peripheral B function. If the same bit is set to 1 in PIO_ABCDSR2: 0: Assigns the I/O line to the Peripheral C function. 1: Assigns the I/O line to the Peripheral D function. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 247 SAM9X25 SAM9X25 23.7.25 PIO Peripheral ABCD Select Register 2 Name: PIO_ABCDSR2 Access: Read-write This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Peripheral Select. If the same bit is set to 0 in PIO_ABCDSR1: 0: Assigns the I/O line to the Peripheral A function.

- Page 248 PIO Input Filter Slow Clock Enable Register Name: PIO_IFSCER Address: 0xFFFFF484 (PIOA), 0xFFFFF684 (PIOB), 0xFFFFF884 (PIOC), 0xFFFFFA84 (PIOD) Access: Write-only • P0-P31: Debouncing Filtering Select. 0: No Effect. 1: The Debouncing Filter is able to filter pulses with a duration < Tdiv_slclk/2. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...

- Page 249 SAM9X25 SAM9X25 23.7.28 PIO Input Filter Slow Clock Status Register Name: PIO_IFSCSR Address: 0xFFFFF488 (PIOA), 0xFFFFF688 (PIOB), 0xFFFFF888 (PIOC), 0xFFFFFA88 (PIOD) Access: Read-only • P0-P31: Glitch or Debouncing Filter Selection Status 0: The Glitch Filter is able to filter glitches with a duration < Tmck2.

- Page 250 This register can only be written if the WPEN bit is cleared in “PIO Write Protect Mode Register” • P0-P31: Pull Down Enable. 0: No effect. 1: Enables the pull down resistor on the I/O line. SAM9X25 SAM9X25 11054A–ATARM–27-Jul-11 11054A–ATARM–27-Jul-11...