Table of Contents

Advertisement

Quick Links

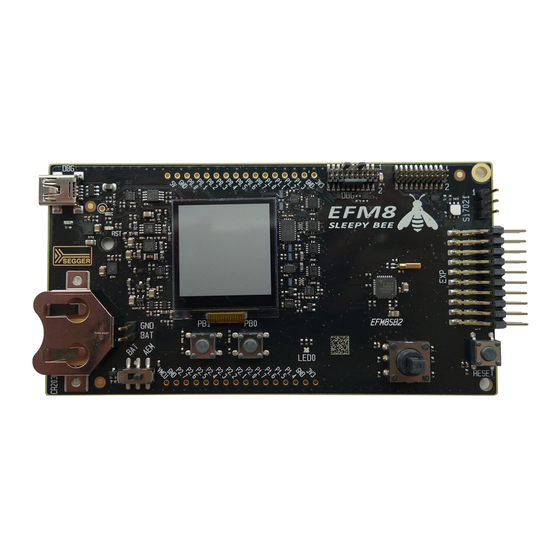

EFM8 Sleepy Bee Family

EFM8SB2 Reference Manual

The EFM8SB2, part of the Sleepy Bee family of MCUs, is the

world's most energy friendly 8-bit microcontrollers with a compre-

hensive feature set in small packages.

These devices offer lowest power consumption by combining innovative low energy tech-

niques and short wakeup times from energy saving modes into small packages, making

them well-suited for any battery operated applications. With an efficient 8051 core, 6-bit

current reference, and precision analog, the EFM8SB2 family is also optimal for embed-

ded applications.

EFM8SB2 applications include the following:

• Hand-held devices

• Industrial controls

Core / Memory

CIP-51 8051 Core

(25 MHz)

Flash Program

RAM Memory

Memory

(4352 bytes)

(up to 64 KB)

Serial Interfaces

UART

2 x SPI

2

I

C / SMBus

Lowest power mode with peripheral operational:

Normal

Idle

silabs.com | Smart. Connected. Energy-friendly.

• Battery-operated consumer electronics

• Sensor interfaces

Debug Interface

External 32 kHz

with C2

RTC Oscillator

I/O Ports

External

Pin Reset

Interrupts

General

Pin Wakeup

Purpose I/O

Suspend

Sleep

Clock Management

Low Power 20

External

MHz RC

Oscillator

Oscillator

High Frequency

24.5 MHz RC

Oscillator

8-bit SFR bus

Timers and Triggers

Timers

PCA/PWM

0/1/2/3

Watchdog

Real Time

Timer

Clock

ENERGY FRIENDLY FEATURES

• Lowest MCU sleep current with supply

brownout detection (50 nA)

• Lowest MCU active current with these

features (170 μA / MHz at 24.5 MHz clock

rate)

• Lowest MCU sleep current using internal

RTC operating and supply brownout

detection (<300 nA)

• Ultra-fast wake up for digital and analog

peripherals (< 2 μs)

• Integrated low drop out (LDO) voltage

regulator to maintain ultra-low active

current at all voltages

Energy Management

Internal LDO

Power-On Reset

Regulator

Brown-Out Detector

Analog Interfaces

ADC

Comparator 0

Internal Voltage

Comparator 1

Reference

Internal Current Reference

Security

16/32-bit CRC

Rev. 0.1

Advertisement

Table of Contents

Summary of Contents for Silicon Laboratories EFM8SB2

- Page 1 (170 μA / MHz at 24.5 MHz clock rate) them well-suited for any battery operated applications. With an efficient 8051 core, 6-bit current reference, and precision analog, the EFM8SB2 family is also optimal for embed- • Lowest MCU sleep current using internal RTC operating and supply brownout ded applications.

-

Page 2: System Overview

Analog Peripherals 20 MHz Oscillator Comparators External Internal External XTAL1 Oscillator VREF VREF XTAL2 Circuit VREF 10-bit Temp 6-bit IREF0 300ksps Sensor IREF XTAL3 Oscillator XTAL4 Figure 1.1. Detailed EFM8SB2 Block Diagram silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 1... -

Page 3: Power

EFM8SB2 Reference Manual System Overview 1.2 Power All internal circuitry draws power from the VDD supply pin. External I/O pins are powered from the VIO supply voltage (or VDD on devi- ces without a separate VIO connection), while most of the internal circuitry is supplied by an on-chip LDO regulator. Control over the device power can be achieved by enabling/disabling individual peripherals as needed. -

Page 4: Counters/Timers And Pwm

EFM8SB2 Reference Manual System Overview 1.5 Counters/Timers and PWM Real Time Clock (RTC0) The RTC is an ultra low power, 36 hour 32-bit independent time-keeping Real Time Clock with alarm. The RTC has a dedicated 32 kHz oscillator. No external resistor or loading capacitors are required, and a missing clock detector features alerts the system if the external crystal fails. -

Page 5: Communications And Other Digital Peripherals

EFM8SB2 Reference Manual System Overview Watchdog Timer (WDT0) The device includes a programmable watchdog timer (WDT) integrated within the PCA0 peripheral. A WDT overflow forces the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT overflows and causes a reset. -

Page 6: Analog

EFM8SB2 Reference Manual System Overview External Memory Interface (EMIF0) The External Memory Interface (EMIF) enables access of off-chip memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) with the target address specified in either 8-bit or 16-bit formats. - Page 7 EFM8SB2 Reference Manual System Overview 10-Bit Analog-to-Digital Converter (ADC0) The ADC is a successive-approximation-register (SAR) ADC with 10- and 8-bit modes, integrated track-and hold and a programmable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer.

-

Page 8: Reset Sources

1.9 Debugging The EFM8SB2 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow flash programming and in-system debug- ging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. -

Page 9: Memory Organization

EFM8SB2 Reference Manual Memory Organization 2. Memory Organization 2.1 Memory Organization The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. - Page 10 EFM8SB2 Reference Manual Memory Organization Bit Addressable Locations In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also ac- cessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07.

-

Page 11: Memory Map

EFM8SB2 Reference Manual Memory Organization 2.4 Memory Map 0xFFFF Reserved 0xFBFF Lock Byte 0xFBFE Security Page 1024 Bytes 0xF800 63 KB Flash (63 x 1024 Byte pages) 0x03FF Scratchpad 1024 Bytes 0x0000 0x0000 Figure 2.1. Flash Memory Map — 64 KB Devices silabs.com | Smart. - Page 12 EFM8SB2 Reference Manual Memory Organization 0xFFFF Reserved 0x7FFF Lock Byte 0x7FFE Security Page 1024 Bytes 0x7C00 32 KB Flash (32 x 1024 Byte pages) 0x03FF Scratchpad 1024 Bytes 0x0000 0x0000 Figure 2.2. Flash Memory Map — 32 KB Devices silabs.com | Smart. Connected. Energy-friendly.

- Page 13 EFM8SB2 Reference Manual Memory Organization 0xFFFF Reserved 0x3FFF Lock Byte 0x3FFE Security Page 1024 Bytes 0x3C00 16 KB Flash 0x03FF Scratchpad (16 x 1024 Byte pages) 1024 Bytes 0x0000 0x0000 Figure 2.3. Flash Memory Map — 16 KB Devices On-Chip RAM...

- Page 14 EFM8SB2 Reference Manual Memory Organization On-Chip XRAM Accessed with MOVX Instructions 0xFFFF Shadow XRAM Duplicates 0x0000-0x0FFF On 4096 B boundaries 0x1000 0x0FFF XRAM 4096 Bytes 0x0000 Figure 2.5. XRAM Memory silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 13...

-

Page 15: Special Function Registers

The CIP-51 features SFR paging, allowing the device to map many SFRs into the 0x80 to 0xFF memory address space. The SFR memory space has 256 pages. In this way, each memory location from 0x80 to 0xFF can access up to 256 SFRs. The EFM8SB2 devices utilize multiple SFR pages. -

Page 16: Special Function Register Memory Map

EFM8SB2 Reference Manual Special Function Registers 3.2 Special Function Register Memory Map Table 3.1. Special Function Registers by Address Address SFR Page Address SFR Page (*bit-addressable) 0x00 0x0F (*bit-addressable) 0x00 0x0F 0x80* 0xC0* SMB0CN0 0x81 0xC1 SMB0CF 0x82 0xC2 SMB0DAT... - Page 17 EFM8SB2 Reference Manual Special Function Registers Address SFR Page Address SFR Page (*bit-addressable) 0x00 0x0F (*bit-addressable) 0x00 0x0F 0xA1 SPI0CFG 0xE1 XBR0 0xA2 SPI0CKR 0xE2 XBR1 0xA3 SPI0DAT 0xE3 XBR2 0xA4 P0MDOUT P0DRV 0xE4 IT01CF 0xA5 P1MDOUT P1DRV 0xE5 0xA6...

- Page 18 EFM8SB2 Reference Manual Special Function Registers Register Address SFR Pages Description ADC0CF 0xBC 0x00 ADC0 Configuration ADC0CN0 0xE8 0x00 ADC0 Control 0 ADC0GTH 0xC4 0x00 ADC0 Greater-Than High Byte ADC0GTL 0xC3 0x00 ADC0 Greater-Than Low Byte ADC0H 0xBE 0x00 ADC0 Data Word High Byte...

- Page 19 EFM8SB2 Reference Manual Special Function Registers Register Address SFR Pages Description HFO0CAL 0xB3 0x00 High Frequency Oscillator Calibration HFO0CN 0xB2 0x00 High Frequency Oscillator Control 0xA8 Interrupt Enable 0xB8 Interrupt Priority IREF0CN0 0xB9 0x00 Current Reference Control 0 IT01CF 0xE4...

- Page 20 EFM8SB2 Reference Manual Special Function Registers Register Address SFR Pages Description PCA0CPL5 0xD2 0x00 PCA Channel 5 Capture Module Low Byte PCA0CPM0 0xDA 0x00 PCA Channel 0 Capture/Compare Mode PCA0CPM1 0xDB 0x00 PCA Channel 1 Capture/Compare Mode PCA0CPM2 0xDC 0x00...

-

Page 21: Sfr Access Control Registers

EFM8SB2 Reference Manual Special Function Registers Register Address SFR Pages Description SPI1DAT 0x86 0x00 SPI1 Data TCON 0x88 0x00 Timer 0/1 Control 0x8C 0x00 Timer 0 High Byte 0x8D 0x00 Timer 1 High Byte 0x8A 0x00 Timer 0 Low Byte... -

Page 22: Flash Memory

EFM8SB2 Reference Manual Flash Memory 4. Flash Memory 4.1 Introduction On-chip, re-programmable flash memory is included for program code and non-volatile data storage. The flash memory is organized in 1024-byte pages. It can be erased and written through the C2 interface or from firmware by overloading the MOVX instruction. Any individual byte in flash memory must only be written once between page erase operations. - Page 23 EFM8SB2 Reference Manual Flash Memory 0xFFFF Reserved 0x7FFF Lock Byte 0x7FFE Security Page 1024 Bytes 0x7C00 32 KB Flash (32 x 1024 Byte pages) 0x03FF Scratchpad 1024 Bytes 0x0000 0x0000 Figure 4.2. Flash Memory Map — 32 KB Devices silabs.com | Smart. Connected. Energy-friendly.

-

Page 24: Features

EFM8SB2 Reference Manual Flash Memory 0xFFFF Reserved 0x3FFF Lock Byte 0x3FFE Security Page 1024 Bytes 0x3C00 16 KB Flash 0x03FF Scratchpad (16 x 1024 Byte pages) 1024 Bytes 0x0000 0x0000 Figure 4.3. Flash Memory Map — 16 KB Devices 4.2 Features The flash memory has the following features: •... -

Page 25: Functional Description

EFM8SB2 Reference Manual Flash Memory 4.3 Functional Description 4.3.1 Security Options The CIP-51 provides security options to protect the flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the flash memory from accidental modification by software. -

Page 26: Programming The Flash Memory

EFM8SB2 Reference Manual Flash Memory Target Area for Read / Write / Erase Permissions from C2 interface [R] = Read permitted [W] = Write permitted [E] = Erase permitted Device Erase Only = No read, write, or individual page erase is allowed. Must erase entire flash space. -

Page 27: Flash Write And Erase Precautions

EFM8SB2 Reference Manual Flash Memory 7. Clear the PSWE bit. 4.3.3 Flash Write and Erase Precautions Any system which contains routines which write or erase flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of supply voltage, system clock frequency or temperature. -

Page 28: Minimizing Flash Read Current

EFM8SB2 Reference Manual Flash Memory 4.3.4 Minimizing Flash Read Current The flash memory is responsible for a substantial portion of the total digital supply current when the device is executing code. Below are suggestions to minimize flash read current. 1. Use low power modes while waiting for an interrupt, rather than polling the interrupt flag. -

Page 29: Flash Control Registers

EFM8SB2 Reference Manual Flash Memory 4.4 Flash Control Registers 4.4.1 PSCTL: Program Store Control Name Reserved SFLE PSEE PSWE Access Reset 0x00 SFR Page = 0x0; SFR Address: 0x8F Name Reset Access Description Reserved Must write reset value. SFLE Scratchpad Flash Memory Access Enable. -

Page 30: Flkey: Flash Lock And Key

EFM8SB2 Reference Manual Flash Memory 4.4.2 FLKEY: Flash Lock and Key Name FLKEY Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xB7 Name Reset Access Description FLKEY 0x00 Flash Lock and Key Register. Write: This register provides a lock and key function for flash erasures and writes. Flash writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY register. -

Page 31: Device Identification

EFM8SB2 Reference Manual Device Identification 5. Device Identification 5.1 Unique Identifier A 32-bit unique identifier (UID) is pre-loaded upon device reset into the last four bytes of the XRAM area on all devices. The UID can be read by firmware using MOVX instructions and through the debug port. -

Page 32: Interrupts

EFM8SB2 Reference Manual Interrupts 6. Interrupts 6.1 Introduction The MCU core includes an extended interrupt system supporting multiple interrupt sources and priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. -

Page 33: Interrupt Summary

EFM8SB2 Reference Manual Interrupts 6.2.3 Interrupt Summary Table 6.1. Interrupt Priority Table Interrupt Source Vector Priority Primary Enable Auxiliary Enable(s) Pending Flag(s) Reset 0x0000 External Interrupt 0 0x0003 IE_EX0 TCON_IE0 Timer 0 Overflow 0x000B IE_ET0 TCON_TF0 External Interrupt 1 0x0013... - Page 34 EFM8SB2 Reference Manual Interrupts Interrupt Source Vector Priority Primary Enable Auxiliary Enable(s) Pending Flag(s) SPI1 0x0093 EIE2_ESPI1 SPI1CN0_MODF SPI1CN0_RXOVRN SPI1CN0_SPIF SPI1CN0_WCOL silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 33...

-

Page 35: Interrupt Control Registers

EFM8SB2 Reference Manual Interrupts 6.3 Interrupt Control Registers 6.3.1 IE: Interrupt Enable Name ESPI0 Access Reset SFR Page = ALL; SFR Address: 0xA8 (bit-addressable) Name Reset Access Description All Interrupts Enable. Globally enables/disables all interrupts and overrides individual interrupt mask settings. - Page 36 EFM8SB2 Reference Manual Interrupts Name Reset Access Description External Interrupt 1 Enable. This bit sets the masking of External Interrupt 1. Value Name Description DISABLED Disable external interrupt 1. ENABLED Enable interrupt requests generated by the INT1 input. Timer 0 Interrupt Enable.

-

Page 37: Ip: Interrupt Priority

EFM8SB2 Reference Manual Interrupts 6.3.2 IP: Interrupt Priority Name Reserved PSPI0 Access Reset SFR Page = ALL; SFR Address: 0xB8 (bit-addressable) Name Reset Access Description Reserved Must write reset value. PSPI0 Serial Peripheral Interface (SPI0) Interrupt Priority Control. This bit sets the priority of the SPI0 interrupt. - Page 38 EFM8SB2 Reference Manual Interrupts Name Reset Access Description Value Name Description Timer 0 interrupt set to low priority level. HIGH Timer 0 interrupt set to high priority level. External Interrupt 0 Priority Control. This bit sets the priority of the External Interrupt 0 interrupt.

-

Page 39: Eie1: Extended Interrupt Enable 1

EFM8SB2 Reference Manual Interrupts 6.3.3 EIE1: Extended Interrupt Enable 1 Name ECP1 ECP0 EPCA0 EADC0 EWADC0 ERTC0A ESMB0 Access Reset SFR Page = ALL; SFR Address: 0xE6 Name Reset Access Description Timer 3 Interrupt Enable. This bit sets the masking of the Timer 3 interrupt. - Page 40 EFM8SB2 Reference Manual Interrupts Name Reset Access Description Value Name Description DISABLED Disable ADC0 Window Comparison interrupt. ENABLED Enable interrupt requests generated by ADC0 Window Compare flag (ADWINT). ERTC0A RTC Alarm Interrupt Enable. This bit sets the masking of the RTC Alarm interrupt.

-

Page 41: Eip1: Extended Interrupt Priority 1

EFM8SB2 Reference Manual Interrupts 6.3.4 EIP1: Extended Interrupt Priority 1 Name PCP1 PCP0 PPCA0 PADC0 PWADC0 PRTC0A PSMB0 Access Reset SFR Page = ALL; SFR Address: 0xF6 Name Reset Access Description Timer 3 Interrupt Priority Control. This bit sets the priority of the Timer 3 interrupt. - Page 42 EFM8SB2 Reference Manual Interrupts Name Reset Access Description Value Name Description ADC0 Window interrupt set to low priority level. HIGH ADC0 Window interrupt set to high priority level. PRTC0A RTC Alarm Interrupt Priority Control. This bit sets the priority of the RTC Alarm interrupt.

-

Page 43: Eie2: Extended Interrupt Enable 2

EFM8SB2 Reference Manual Interrupts 6.3.5 EIE2: Extended Interrupt Enable 2 Name Reserved ESPI1 ERTC0F EMAT EWARN Access Reset SFR Page = ALL; SFR Address: 0xE7 Name Reset Access Description Reserved Must write reset value. ESPI1 Serial Peripheral Interface (SPI1) Interrupt Enable. -

Page 44: Eip2: Extended Interrupt Priority 2

EFM8SB2 Reference Manual Interrupts 6.3.6 EIP2: Extended Interrupt Priority 2 Name Reserved PSPI1 PRTC0F PMAT PWARN Access Reset SFR Page = ALL; SFR Address: 0xF7 Name Reset Access Description Reserved Must write reset value. PSPI1 Serial Peripheral Interface (SPI1) Interrupt Priority Control. -

Page 45: Power Management And Internal Regulators

EFM8SB2 Reference Manual Power Management and Internal Regulators 7. Power Management and Internal Regulators 7.1 Introduction All internal circuitry draws power from the VDD supply pin. External I/O pins are powered from the VIO supply voltage (or VDD on devi- ces without a separate VIO connection), while most of the internal circuitry is supplied by an on-chip LDO regulator. -

Page 46: Features

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.2 Features • Supports four power modes: • Normal mode: Core and all peripherals fully operational. • Idle mode: Core halted, peripherals fully operational, core waiting for interrupt to continue. • Suspend mode: Similar to Sleep mode, with faster wake-up times, but higher current consumption. Code resumes execution at the next instruction. -

Page 47: Suspend Mode

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.5 Suspend Mode Suspend mode is entered by setting the SUSPEND bit while operating from the internal 24.5 MHz oscillator (HFOSC0) or the internal 20 MHz oscillator (LPOSC0). Upon entry into suspend mode, the hardware halts all of the internal oscillators and goes into a low power state as soon as the instruction that sets the bit completes execution. -

Page 48: Sleep Mode

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.6 Sleep Mode Setting the sleep mode select bit in the PMU0CF register turns off the internal 1.8 V core LDO regulator and switches the power supply of all on-chip RAM to the VDD pin. Power to most digital logic on the chip is disconnected; only the power management unit and RTC remain powered. -

Page 49: Determining The Event That Caused The Last Wakeup

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.6.2 Determining the Event that Caused the Last Wakeup When waking from Idle mode, the CPU will vector to the interrupt which caused it to wake up. When waking from Stop mode, the RSTSRC register may be read to determine the cause of the last reset. -

Page 50: Pmu0Cf: Power Management Unit Configuration

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.7.2 PMU0CF: Power Management Unit Configuration Name SLEEP SUSPEND CLEAR RSTWK RTCFWK RTCAWK PMATWK CPT0WK Access Reset Varies Varies Varies Varies Varies SFR Page = 0x0; SFR Address: 0xB5 Name Reset Access... -

Page 51: Reg0Cn: Voltage Regulator Control

EFM8SB2 Reference Manual Power Management and Internal Regulators 7.7.3 REG0CN: Voltage Regulator Control Name Reserved OSCBIAS Reserved Access Reset SFR Page = 0x0; SFR Address: 0xC9 Name Reset Access Description Reserved Must write reset value. OSCBIAS High Frequency Oscillator Bias. -

Page 52: Clocking And Oscillators

EFM8SB2 Reference Manual Clocking and Oscillators 8. Clocking and Oscillators 8.1 Introduction The CPU core and peripheral subsystem may be clocked by both internal and external oscillator resources. By default, the system clock comes up running from the 20 MHz low power oscillator divided by 8. -

Page 53: Rtc0 Oscillator

EFM8SB2 Reference Manual Clocking and Oscillators 8.3.4 RTC0 Oscillator The system clock can be derived from the RTC0 oscillator, which can run from either an external 32 kHz crystal or an internal 16.4 kHz ±20% low frequency oscillator (LFOSC0). No loading capacitors are required for the crystal, and it can be connected directly to the XTAL3 and XTAL4 pins. -

Page 54: External Crystal

EFM8SB2 Reference Manual Clocking and Oscillators 8.3.5 External Crystal If a crystal or ceramic resonator is used as the external oscillator, the crystal/resonator and a 10 MΩ resistor must be wired across the XTAL1 and XTAL2 pins. Appropriate loading capacitors should be added to XTAL1 and XTAL2, and both pins should be configured for analog I/O with the digital output drivers disabled. - Page 55 EFM8SB2 Reference Manual Clocking and Oscillators Table 8.1. Recommended XFCN Settings for Crystal Mode XFCN Field Setting Crystal Frequency Approximate Bias Current f ≤ 20 kHz 0.5 µA 20 kHz < f ≤ 58 kHz 1.5 µA 58 kHz < f ≤ 155 kHz 4.8 µA...

-

Page 56: External Rc And C Modes

EFM8SB2 Reference Manual Clocking and Oscillators 8.3.6 External RC and C Modes External RC Example An RC network connected to the XTAL2 pin can be used as a basic oscillator. XTAL1 is not affected in RC mode. XTAL1 XTAL2 Figure 8.5. External RC Oscillator Configuration The capacitor should be no greater than 100 pF;... - Page 57 EFM8SB2 Reference Manual Clocking and Oscillators External Capacitor Example If a capacitor is used as the external oscillator, the circuit should be configured as shown in . The capacitor should be added to XTAL2, and XTAL2 should be configured for analog I/O with the digital output drivers disabled. XTAL1 is not affected in C mode.

-

Page 58: External Cmos

EFM8SB2 Reference Manual Clocking and Oscillators Recommended XFCN Settings for RC and C Modes Table 8.2. Recommended XFCN Settings for RC and C Modes XFCN Field Setting Approximate Frequency K Factor (C Mode) Actual Measured Frequency Range (C Mode) f ≤ 25 kHz K Factor = 0.87... -

Page 59: Clocking And Oscillator Control Registers

EFM8SB2 Reference Manual Clocking and Oscillators 8.4 Clocking and Oscillator Control Registers 8.4.1 CLKSEL: Clock Select Name CLKRDY CLKDIV Reserved CLKSL Access Reset SFR Page = ALL; SFR Address: 0xA9 Name Reset Access Description CLKRDY System Clock Divider Clock Ready Flag. -

Page 60: Hfo0Cal: High Frequency Oscillator Calibration

EFM8SB2 Reference Manual Clocking and Oscillators 8.4.2 HFO0CAL: High Frequency Oscillator Calibration Name HFO0CAL Access Reset Varies SFR Page = 0x0; SFR Address: 0xB3 Name Reset Access Description Spread Spectrum Enable. Value Name Description DISABLED Spread Spectrum clock dithering disabled. -

Page 61: Xosc0Cn: External Oscillator Control

EFM8SB2 Reference Manual Clocking and Oscillators 8.4.4 XOSC0CN: External Oscillator Control Name XCLKVLD XOSCMD Reserved XFCN Access Reset SFR Page = 0x0; SFR Address: 0xB1 Name Reset Access Description XCLKVLD External Oscillator Valid Flag. Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by 2. -

Page 62: Real Time Clock (Rtc0)

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9. Real Time Clock (RTC0) 9.1 Introduction The RTC is an ultra low power, 36 hour 32-bit independent time-keeping Real Time Clock with alarm. The RTC has a dedicated 32 kHz oscillator. No external resistor or loading capacitors are required, and a missing clock detector features alerts the system if the external crystal fails. - Page 63 EFM8SB2 Reference Manual Real Time Clock (RTC0) Accessing Internal RTC Registers The RTC internal registers can be read and written using RTC0ADR and RTC0DAT. The RTC0ADR register selects the RTC internal register that will be targeted by subsequent reads or writes. Recommended instruction timing is provided in this section. If the recom- mended instruction timing is not followed, then firmware should check the BUSY bit prior to each read or write operation to make sure the RTC interface is not busy performing the previous read or write operation.

-

Page 64: Clocking Options

EFM8SB2 Reference Manual Real Time Clock (RTC0) Autoincrement Feature For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current RTC timer value. Auto- increment is always enabled. - Page 65 EFM8SB2 Reference Manual Real Time Clock (RTC0) Using Self-Oscillate Mode When using self-oscillate mode, the XTAL3 and XTAL4 pins should be shorted together. The RTC0PIN register can be used to internal- ly short XTAL3 and XTAL4. To configure the RTC for self-oscillate mode: 1.

- Page 66 EFM8SB2 Reference Manual Real Time Clock (RTC0) Automatic Gain Control (Crystal Mode Only) and Bias Doubling Automatic gain control (AGC) allows the RTC oscillator to trim the oscillation amplitude of a crystal in order to achieve the lowest possi- ble power consumption. Automatic gain control automatically detects when the oscillation amplitude has reached a point where it safe to reduce the drive current, so it may be enabled during crystal startup.

-

Page 67: Timer And Alarm

EFM8SB2 Reference Manual Real Time Clock (RTC0) Missing Clock Detector The missing RTC detector is a one-shot circuit enabled by setting MCLKEN to 1. When the RTC missing clock detector is enabled, OSCFAIL is set by hardware if the RTC oscillator remains high or low for more than 100 μs. An RTC missing clock detector timeout can trigger an interrupt, wake the device from a low power mode, or reset the device. -

Page 68: Rtc Control Registers

EFM8SB2 Reference Manual Real Time Clock (RTC0) Software Considerations The RTC timer and alarm have two operating modes to suit varying applications: Mode 1 The first mode uses the RTC timer as a perpetual timebase which is never reset to zero. Every 36 hours, the timer is allowed to over- flow without being stopped or disrupted. -

Page 69: Rtc0Adr: Rtc Address

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.2 RTC0ADR: RTC Address Name BUSY AUTORD Reserved SHORT ADDR Access Reset SFR Page = 0x0; SFR Address: 0xAC Name Reset Access Description BUSY RTC Interface Busy Indicator. This bit indicates the RTC interface status. Writing a 1 to this bit initiates an indirect read. -

Page 70: Rtc0Cn0: Rtc Control 0

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.4 RTC0CN0: RTC Control 0 Name RTC0EN MCLKEN OSCFAIL RTC0TR RTC0AEN ALRM RTC0SET RTC0CAP Access Reset Varies Indirect Address: 0x04 Name Reset Access Description RTC0EN RTC Enable. Enables/disables the RTC oscillator and associated bias currents. - Page 71 EFM8SB2 Reference Manual Real Time Clock (RTC0) Name Reset Access Description Alarm event flag is set or enable the auto reset function. RTC0SET RTC Timer Set. Writing 1 initiates a RTC timer set operation. This bit is cleared to 0 by hardware to indicate that the timer set operation is complete.

-

Page 72: Rtc0Xcn0: Rtc Oscillator Control 0

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.5 RTC0XCN0: RTC Oscillator Control 0 Name AGCEN XMODE BIASX2 CLKVLD Reserved Access Reset Indirect Address: 0x05 Name Reset Access Description AGCEN RTC Oscillator Automatic Gain Control (AGC) Enable. Value Name Description DISABLED Disable AGC. -

Page 73: Rtc0Xcf: Rtc Oscillator Configuration

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.6 RTC0XCF: RTC Oscillator Configuration Name AUTOSTP LOADRDY Reserved LOADCAP Access Reset Varies Indirect Address: 0x06 Name Reset Access Description AUTOSTP 0 Automatic Load Capacitance Stepping Enable. Enables/disables automatic load capacitance stepping. Value... -

Page 74: Capture1: Rtc Timer Capture 1

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.8 CAPTURE1: RTC Timer Capture 1 Name CAPTURE1 Access Reset 0x00 Indirect Address: 0x01 Name Reset Access Description CAP- 0x00 RTC Timer Capture 1. TURE1 The CAPTURE3-CAPTURE0 registers are used to read or set the 32-bit RTC timer. Data is transferred to or from the RTC timer when the RTC0SET or RTC0CAP bits are set. -

Page 75: Alarm0: Rtc Alarm Programmed Value 0

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.11 ALARM0: RTC Alarm Programmed Value 0 Name ALARM0 Access Reset 0x00 Indirect Address: 0x08 Name Reset Access Description ALARM0 0x00 RTC Alarm Programmed Value 0. The ALARM3-ALARM0 registers are used to set an alarm event for the RTC timer. The RTC alarm should be disabled (RTC0AEN=0) when updating these registers. -

Page 76: Alarm3: Rtc Alarm Programmed Value 3

EFM8SB2 Reference Manual Real Time Clock (RTC0) 9.4.14 ALARM3: RTC Alarm Programmed Value 3 Name ALARM3 Access Reset 0x00 Indirect Address: 0x0B Name Reset Access Description ALARM3 0x00 RTC Alarm Programmed Value 3. The ALARM3-ALARM0 registers are used to set an alarm event for the RTC timer. The RTC alarm should be disabled (RTC0AEN=0) when updating these registers. -

Page 77: Reset Sources And Power Supply Monitor

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10. Reset Sources and Power Supply Monitor 10.1 Introduction Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur: •... -

Page 78: Functional Description

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.3 Functional Description 10.3.1 Device Reset Upon entering a reset state from any source, the following events occur: • The processor core halts program execution. • Special Function Registers (SFRs) are initialized to their defined reset values. -

Page 79: Power-On Reset

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.3.2 Power-On Reset During power-up, the POR circuit fires. When POR fires, the device is held in a reset state and the RSTb pin is high-impedance with the weak pull-up either on or off until the supply voltage settles above V . -

Page 80: Supply Monitor Reset

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.3.3 Supply Monitor Reset The supply monitor senses the voltage on the device's supply pin and can generate a reset if the supply drops below the corresponding threshold. This monitor is enabled and enabled as a reset source after initial power-on to protect the device until the supply is an ade- quate and stable voltage. -

Page 81: Pca Watchdog Timer Reset

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.3.7 PCA Watchdog Timer Reset The programmable watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in the PCA documentation. -

Page 82: Reset Sources And Supply Monitor Control Registers

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.4 Reset Sources and Supply Monitor Control Registers 10.4.1 RSTSRC: Reset Source Name RTC0RE FERROR C0RSEF SWRSF WDTRSF MCDRSF PORSF PINRSF Access Reset Varies Varies Varies Varies Varies Varies Varies Varies SFR Page = 0x0;... -

Page 83: Vdm0Cn: Vdd Supply Monitor Control

EFM8SB2 Reference Manual Reset Sources and Power Supply Monitor 10.4.2 VDM0CN: VDD Supply Monitor Control Name VDMEN VDDSTAT VDDOK Reserved Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xFF Name Reset Access Description VDMEN V<subscript>DD</subscript> Supply Monitor Enable. This bit turns the V supply monitor circuit on/off. -

Page 84: Microcontroller Core

EFM8SB2 Reference Manual CIP-51 Microcontroller Core 11. CIP-51 Microcontroller Core 11.1 Introduction The CIP-51 microcontroller core is a high-speed, pipelined, 8-bit core utilizing the standard MCS-51™ instruction set. Any standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. -

Page 85: Features

EFM8SB2 Reference Manual CIP-51 Microcontroller Core Performance The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. The CIP-51 core executes 76 of its 109 instructions in one or two clock cycles, with no instructions taking more than eight clock cycles. The table below shows the distribution of instructions vs. -

Page 86: Instruction Set

EFM8SB2 Reference Manual CIP-51 Microcontroller Core 11.3.2 Instruction Set The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51™ instruction set. Standard 8051 de- velopment tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51™... - Page 87 EFM8SB2 Reference Manual CIP-51 Microcontroller Core Mnemonic Description Bytes Clock Cycles ANL A, @Ri AND indirect RAM to A ANL A, #data AND immediate to A ANL direct, A AND A to direct byte ANL direct, #data AND immediate to direct byte...

- Page 88 EFM8SB2 Reference Manual CIP-51 Microcontroller Core Mnemonic Description Bytes Clock Cycles MOV @Ri, direct Move direct byte to indirect RAM MOV @Ri, #data Move immediate to indirect RAM MOV DPTR, #data16 Load DPTR with 16-bit constant MOVC A, @A+DPTR Move code byte relative DPTR to A...

-

Page 89: Cpu Core Registers

EFM8SB2 Reference Manual CIP-51 Microcontroller Core Mnemonic Description Bytes Clock Cycles RETI Return from interrupt AJMP addr11 Absolute jump LJMP addr16 Long jump SJMP rel Short jump (relative address) JMP @A+DPTR Jump indirect relative to DPTR JZ rel Jump if A equals zero... -

Page 90: Dph: Data Pointer High

EFM8SB2 Reference Manual CIP-51 Microcontroller Core 11.4.2 DPH: Data Pointer High Name Access Reset 0x00 SFR Page = ALL; SFR Address: 0x83 Name Reset Access Description 0x00 Data Pointer High. The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indirectly addressed flash memory or XRAM. -

Page 91: B: B Register

EFM8SB2 Reference Manual CIP-51 Microcontroller Core 11.4.5 B: B Register Name Access Reset 0x00 SFR Page = ALL; SFR Address: 0xF0 (bit-addressable) Name Reset Access Description 0x00 B Register. This register serves as a second accumulator for certain arithmetic operations. -

Page 92: Psw: Program Status Word

EFM8SB2 Reference Manual CIP-51 Microcontroller Core 11.4.6 PSW: Program Status Word Name PARITY Access Reset SFR Page = ALL; SFR Address: 0xD0 (bit-addressable) Name Reset Access Description Carry Flag. This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow (subtraction). It is cleared to logic 0 by all other arithmetic operations. -

Page 93: Port I/O, Crossbar, External Interrupts, And Port Match

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12. Port I/O, Crossbar, External Interrupts, and Port Match 12.1 Introduction Digital and analog resources are externally available on the device’s multi-purpose I/O pins. Port pins P0.0-P2.6 can be defined as gen- eral-purpose I/O (GPIO), assigned to one of the internal digital resources through the crossbar or dedicated channels, or assigned to an analog function. -

Page 94: Functional Description

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.3 Functional Description 12.3.1 Port I/O Modes of Operation Port pins are configured by firmware as digital or analog I/O using the special function registers. Port I/O initialization consists of the following general steps: 1. -

Page 95: Pin Drive Strength

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Configuring Port Pins For Digital Modes Any pins to be used by digital peripherals or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers. -

Page 96: Port I/O Digital Assignments

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.3.2.2 Port I/O Digital Assignments The following table displays the potential mapping of port I/O to each digital function. Table 12.2. Port I/O Assignment for Digital Functions Digital Function... -

Page 97: Priority Crossbar Decoder

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.3.3 Priority Crossbar Decoder The priority crossbar decoder assigns a priority to each I/O function, starting at the top with UART0. The XBRn registers are used to control which crossbar resources are assigned to physical I/O port pins. -

Page 98: Crossbar Functional Map

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.3.3.1 Crossbar Functional Map Figure 12.4 Full Crossbar Map on page 98 shows all of the potential peripheral-to-pin assignments available to the crossbar. Note that this does not mean any peripheral can always be assigned to the highlighted pins. The actual pin assignments are determined by the priority of the enabled peripherals. - Page 99 EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Port Pin Number QFN-24 Package QFN-32 Package AD0m — AD7m, A8 — A11 QFP-32 Package UART0-TX UART0-RX SPI1-SCK SPI1-MISO SPI1-MOSI SPI1-NSS* SPI0-SCK SPI0-MISO SPI0-MOSI SPI0-NSS* SMB0-SDA SMB0-SCL CMP0-CP0 CMP0-CP0A...

-

Page 100: Int0 And Int1

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.3.4 INT0 and INT1 Two direct-pin digital interrupt sources (INT0 and INT1) are included, which can be routed to port 0 pins. Additional I/O interrupts are available through the port match function. As is the case on a standard 8051 architecture, certain controls for these two interrupt sour- ces are available in the Timer0/1 registers. -

Page 101: Port I/O Control Registers

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4 Port I/O Control Registers 12.4.1 XBR0: Port I/O Crossbar 0 Name CP1AE CP1E CP0AE CP0E SYSCKE SMB0E SPI0E URT0E Access Reset SFR Page = 0x0; SFR Address: 0xE1... - Page 102 EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description Value Name Description DISABLED SPI I/O unavailable at Port pins. ENABLED SPI I/O routed to Port pins. The SPI can be assigned either 3 or 4 GPIO pins.

-

Page 103: Xbr1: Port I/O Crossbar 1

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.2 XBR1: Port I/O Crossbar 1 Name Reserved SPI1E ECIE PCA0ME Access Reset SFR Page = 0x0; SFR Address: 0xE2 Name Reset Access Description Reserved Must write reset value. -

Page 104: Xbr2: Port I/O Crossbar 2

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description CEX0_CEX1_CEX2_C CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins. EX3_CEX4_CEX5 12.4.3 XBR2: Port I/O Crossbar 2 Name WEAKPUD XBARE Reserved Access Reset 0x00 SFR Page = 0x0;... -

Page 105: P0Mask: Port 0 Mask

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.4 P0MASK: Port 0 Mask Name Access Reset SFR Page = 0x0; SFR Address: 0xC7 Name Reset Access Description Port 0 Bit 7 Mask Value. Value Name Description IGNORED P0.7 pin logic value is ignored and will not cause a port mismatch event. -

Page 106: P0Mat: Port 0 Match

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.5 P0MAT: Port 0 Match Name Access Reset SFR Page = 0x0; SFR Address: 0xD7 Name Reset Access Description Port 0 Bit 7 Match Value. Value Name Description P0.7 pin logic value is compared with logic LOW. -

Page 107: P0: Port 0 Pin Latch

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.6 P0: Port 0 Pin Latch Name Access Reset SFR Page = ALL; SFR Address: 0x80 (bit-addressable) Name Reset Access Description Port 0 Bit 7 Latch. Value Name Description P0.7 is low. -

Page 108: P0Mdin: Port 0 Input Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.7 P0MDIN: Port 0 Input Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xF1 Name Reset Access Description Port 0 Bit 7 Input Mode. Value Name Description ANALOG P0.7 pin is configured for analog mode. -

Page 109: P0Mdout: Port 0 Output Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.8 P0MDOUT: Port 0 Output Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xA4 Name Reset Access Description Port 0 Bit 7 Output Mode. Value Name Description OPEN_DRAIN P0.7 output is open-drain. -

Page 110: P0Skip: Port 0 Skip

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.9 P0SKIP: Port 0 Skip Name Access Reset SFR Page = 0x0; SFR Address: 0xD4 Name Reset Access Description Port 0 Bit 7 Skip. Value Name Description NOT_SKIPPED P0.7 pin is not skipped by the crossbar. -

Page 111: P0Drv: Port 0 Drive Strength

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.10 P0DRV: Port 0 Drive Strength Name Access Reset SFR Page = 0xF; SFR Address: 0xA4 Name Reset Access Description Port 0 Bit 7 Drive Strength. Value Name Description LOW_DRIVE P0.7 output has low output drive strength. -

Page 112: P1Mask: Port 1 Mask

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description HIGH_DRIVE P0.1 output has high output drive strength. Port 0 Bit 0 Drive Strength. Value Name Description LOW_DRIVE P0.0 output has low output drive strength. -

Page 113: P1Mat: Port 1 Match

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.12 P1MAT: Port 1 Match Name Access Reset SFR Page = 0x0; SFR Address: 0xCF Name Reset Access Description Port 1 Bit 7 Match Value. Value Name Description P1.7 pin logic value is compared with logic LOW. -

Page 114: P1: Port 1 Pin Latch

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.13 P1: Port 1 Pin Latch Name Access Reset SFR Page = ALL; SFR Address: 0x90 (bit-addressable) Name Reset Access Description Port 1 Bit 7 Latch. Value Name Description P1.7 is low. -

Page 115: P1Mdin: Port 1 Input Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.14 P1MDIN: Port 1 Input Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xF2 Name Reset Access Description Port 1 Bit 7 Input Mode. Value Name Description ANALOG P1.7 pin is configured for analog mode. -

Page 116: P1Mdout: Port 1 Output Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.15 P1MDOUT: Port 1 Output Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xA5 Name Reset Access Description Port 1 Bit 7 Output Mode. Value Name Description OPEN_DRAIN P1.7 output is open-drain. -

Page 117: P1Skip: Port 1 Skip

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.16 P1SKIP: Port 1 Skip Name Access Reset SFR Page = 0x0; SFR Address: 0xD5 Name Reset Access Description Port 1 Bit 7 Skip. Value Name Description NOT_SKIPPED P1.7 pin is not skipped by the crossbar. -

Page 118: P1Drv: Port 1 Drive Strength

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.17 P1DRV: Port 1 Drive Strength Name Access Reset SFR Page = 0xF; SFR Address: 0xA5 Name Reset Access Description Port 1 Bit 7 Drive Strength. Value Name Description LOW_DRIVE P1.7 output has low output drive strength. -

Page 119: P2: Port 2 Pin Latch

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description HIGH_DRIVE P1.1 output has high output drive strength. Port 1 Bit 0 Drive Strength. Value Name Description LOW_DRIVE P1.0 output has low output drive strength. -

Page 120: P2Mdin: Port 2 Input Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.19 P2MDIN: Port 2 Input Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xF3 Name Reset Access Description Port 2 Bit 7 Input Mode. Value Name Description ANALOG P2.7 pin is configured for analog mode. -

Page 121: P2Mdout: Port 2 Output Mode

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.20 P2MDOUT: Port 2 Output Mode Name Access Reset SFR Page = 0x0; SFR Address: 0xA6 Name Reset Access Description Port 2 Bit 7 Output Mode. Value Name Description OPEN_DRAIN P2.7 output is open-drain. -

Page 122: P2Skip: Port 2 Skip

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.21 P2SKIP: Port 2 Skip Name Access Reset SFR Page = 0x0; SFR Address: 0xD6 Name Reset Access Description Port 2 Bit 7 Skip. Value Name Description NOT_SKIPPED P2.7 pin is not skipped by the crossbar. -

Page 123: P2Drv: Port 2 Drive Strength

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.4.22 P2DRV: Port 2 Drive Strength Name Access Reset SFR Page = 0xF; SFR Address: 0xA6 Name Reset Access Description Port 2 Bit 7 Drive Strength. Value Name Description LOW_DRIVE P2.7 output has low output drive strength. - Page 124 EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description HIGH_DRIVE P2.1 output has high output drive strength. Port 2 Bit 0 Drive Strength. Value Name Description LOW_DRIVE P2.0 output has low output drive strength.

-

Page 125: Int0 And Int1 Control Registers

EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match 12.5 INT0 and INT1 Control Registers 12.5.1 IT01CF: INT0/INT1 Configuration Name IN1PL IN1SL IN0PL IN0SL Access Reset SFR Page = 0x0; SFR Address: 0xE4 Name Reset Access Description IN1PL INT1 Polarity. - Page 126 EFM8SB2 Reference Manual Port I/O, Crossbar, External Interrupts, and Port Match Name Reset Access Description P0_3 Select P0.3. P0_4 Select P0.4. P0_5 Select P0.5. P0_6 Select P0.6. P0_7 Select P0.7. silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 125...

-

Page 127: Analog-To-Digital Converter (Adc0)

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13. Analog-to-Digital Converter (ADC0) 13.1 Introduction The ADC is a successive-approximation-register (SAR) ADC with 10- and 8-bit modes, integrated track-and hold and a programmable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer. -

Page 128: Features

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.2 Features • Up to 22 external inputs. • Single-ended 10-bit mode. • Supports an output update rate of 300 ksps samples per second. • Operation in low power modes at lower conversion speeds. -

Page 129: Ground Reference

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.3.2.5 Ground Reference To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for the ADC during both the tracking/sampling and the conversion periods is taken from the AGND pin. -

Page 130: Gain Setting

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) ADC0MX setting Signal Name Enumeration Name QFP32 Pin QFN32 Pin QFN24 Pin Name Name Name 10101 ADC0.21 ADC0P21 P2.5 P2.5 Reserved 10110 ADC0.22 ADC0P22 P2.6 P2.6 Reserved 10111 - 11010 ADC0.23 - ADC0.26 Reserved... - Page 131 EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) Settling Time Requirements The absolute minimum tracking time is given in the electrical specifications tables. It may be necessary to track for longer than the mini- mum tracking time specification, depending on the application. For example, if the ADC input is presented with a large series impe- dance, it will take longer for the sampling cap to settle on the final value during the tracking phase.

- Page 132 EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) Configuring the Tracking Time When burst mode is disabled, the ADTM bit controls the ADC track-and-hold mode. In its default state the ADC input is continuously tracked, except when a conversion is in progress. A conversion will begin immediately when the start-of-conversion trigger occurs.

-

Page 133: Burst Mode

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) Figure 13.4. Burst Mode Timing Convert Start ADTM = 1 Powered Power-Up Powered Power-Up T C.. ADEN = 0 Down and Track Down and Track ADTM = 0 Powered Power-Up Powered Power-Up T C T C T C T C.. -

Page 134: Output Formatting

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.3.9 Output Formatting The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code from the ADC at the completion of each conversion. Data can be right-justified or left-justified, depending on the setting of the ADSJST field. When the repeat count is set to 1 in 10-bit mode, conversion codes are represented as 10-bit unsigned integers. -

Page 135: Window Comparator

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.3.10 Window Comparator The ADC's programmable window detector continuously compares the ADC output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt driven system, saving code space and CPU bandwidth while delivering faster system response times. - Page 136 EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) Comparison Register Settings Output Code (ADC0H:L) ADWINT Effects ADC0GTH:L = 0x0040 0x0040 ADWINT Not Affected 0x003F 0x0000 Table 13.8. ADC Window Comparator Example (Outside the 0x0040 to 0x0080 range) Comparison Register Settings Output Code (ADC0H:L)

-

Page 137: Temperature Sensor

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.3.11 Temperature Sensor An on-chip analog temperature sensor is available to the ADC multiplexer input. To use the ADC to measure the temperature sensor, the ADC mux channel should select the temperature sensor. The temperature sensor transfer function is shown in Figure 13.5 Temper-... -

Page 138: Adc0 Control Registers

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4 ADC0 Control Registers 13.4.1 ADC0CN0: ADC0 Control 0 Name ADEN ADBMEN ADINT ADBUSY ADWINT ADCM Access Reset SFR Page = 0x0; SFR Address: 0xE8 (bit-addressable) Name Reset Access Description ADEN ADC Enable. Value... -

Page 139: Adc0Cf: Adc0 Configuration

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.2 ADC0CF: ADC0 Configuration Name ADSC AD8BE ADTM ADGN Access Reset 0x1F SFR Page = 0x0; SFR Address: 0xBC Name Reset Access Description ADSC 0x1F SAR Clock Divider. This field sets the ADC clock divider value. It should be configured to be as close to the maximum SAR clock speed as the datasheet will allow. -

Page 140: Adc0Ac: Adc0 Accumulator Configuration

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.3 ADC0AC: ADC0 Accumulator Configuration Name Reserved ADAE ADSJST ADRPT Access Reset SFR Page = 0x0; SFR Address: 0xBA Name Reset Access Description Reserved Must write reset value. ADAE Accumulate Enable. Enables multiple conversions to be accumulated when burst mode is disabled. -

Page 141: Adc0Pwr: Adc0 Power Control

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.4 ADC0PWR: ADC0 Power Control Name Reserved ADPWR Access Reset SFR Page = 0xF; SFR Address: 0xBA Name Reset Access Description Reserved Must write reset value. ADPWR Burst Mode Power Up Time. This field sets the time delay allowed for the ADC to power up from a low power state. When ADTM is set, an additional 3 SARCLKs are added to this time. -

Page 142: Adc0L: Adc0 Data Word Low Byte

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.7 ADC0L: ADC0 Data Word Low Byte Name ADC0L Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xBD Name Reset Access Description ADC0L 0x00 Data Word Low Byte. When read, this register returns the least significant byte of the 16-bit ADC0 accumulator, formatted according to the set- tings in ADSJST. -

Page 143: Adc0Lth: Adc0 Less-Than High Byte

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.10 ADC0LTH: ADC0 Less-Than High Byte Name ADC0LTH Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xC6 Name Reset Access Description ADC0LTH 0x00 Less-Than High Byte. Most significant byte of the 16-bit less-than window compare register. -

Page 144: Ref0Cn: Voltage Reference Control

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.13 REF0CN: Voltage Reference Control Name Reserved GNDSL REFSL TEMPE Reserved REFOE Access Reset SFR Page = 0x0; SFR Address: 0xD1 Name Reset Access Description Reserved Must write reset value. GNDSL Analog Ground Reference. -

Page 145: Toffh: Temperature Sensor Offset High

EFM8SB2 Reference Manual Analog-to-Digital Converter (ADC0) 13.4.14 TOFFH: Temperature Sensor Offset High Name TOFF Access Reset Varies SFR Page = 0xF; SFR Address: 0x86 Name Reset Access Description TOFF Varies Temperature Sensor Offset High. Most Significant Bits of the 10-bit temperature sensor offset measurement. -

Page 146: Programmable Current Reference (Iref0)

EFM8SB2 Reference Manual Programmable Current Reference (IREF0) 14. Programmable Current Reference (IREF0) 14.1 Introduction The programmable current reference (IREF0) module enables current source or sink with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63 µA (1 µA steps) and the maximum current output in High Current Mode is 504 µA (8 µA steps). -

Page 147: Iref0 Control Registers

EFM8SB2 Reference Manual Programmable Current Reference (IREF0) 14.4 IREF0 Control Registers 14.4.1 IREF0CN0: Current Reference Control 0 Name SINK MDSEL IREF0DAT Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xB9 Name Reset Access Description SINK IREF0 Current Sink Enable. -

Page 148: Comparators (Cmp0 And Cmp1)

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15. Comparators (CMP0 and CMP1) 15.1 Introduction Analog comparators are used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. External input connections to device I/O pins and internal connections are available through separate multiplexers on the positive and negative inputs. -

Page 149: Functional Description

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.3 Functional Description 15.3.1 Response Time and Supply Current Response time is the amount of time delay between a change at the comparator inputs and the comparator's reaction at the output. The comparator response time may be configured in software via the CPMD field in the CMPnMD register. Selecting a longer response time reduces the comparator supply current, while shorter response times require more supply current. -

Page 150: Multiplexer Channel Selection

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.3.3.1 Multiplexer Channel Selection Table 15.1. CMP0 Positive Input Multiplexer Channels CMXP Setting in Signal Name Enumeration Name QFP32 Pin QFN32 Pin QFN24 Pin Register Name Name Name CMP0MX 0000 CMP0P.0 CMP0P0 P0.0 P0.0... - Page 151 EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) CMXN Setting in Signal Name Enumeration Name QFP32 Pin QFN32 Pin QFN24 Pin Register Name Name Name CMP0MX 1101 CMP0N.13 VDD_DIV_2 VDD divided by 2 1110 CMP0N.14 LDO_OUT Internal 1.8V LDO output 1111 CMP0N.15...

-

Page 152: Output Routing

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) CMXN Setting in Signal Name Enumeration Name QFP32 Pin QFN32 Pin QFN24 Pin Register Name Name Name CMP1MX 1001 CMP1N.9 CMP1N9 P2.3 P2.3 Reserved 1010 CMP1N.10 CMP1N10 P2.5 P2.5 Reserved 1011 CMP1N.11 Reserved... -

Page 153: Cmp0 Control Registers

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.4 CMP0 Control Registers 15.4.1 CMP0CN0: Comparator 0 Control 0 Name CPEN CPOUT CPRIF CPFIF CPHYP CPHYN Access Reset SFR Page = 0x0; SFR Address: 0x9B Name Reset Access Description CPEN Comparator Enable. -

Page 154: Cmp0Md: Comparator 0 Mode

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) Name Reset Access Description Value Name Description DISABLED Negative Hysteresis disabled. ENABLED_MODE1 Negative Hysteresis = Hysteresis 1. ENABLED_MODE2 Negative Hysteresis = Hysteresis 2. ENABLED_MODE3 Negative Hysteresis = Hysteresis 3 (Maximum). 15.4.2 CMP0MD: Comparator 0 Mode... -

Page 155: Cmp0Mx: Comparator 0 Multiplexer Selection

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.4.3 CMP0MX: Comparator 0 Multiplexer Selection Name CMXN CMXP Access Reset SFR Page = 0x0; SFR Address: 0x9F Name Reset Access Description CMXN Comparator Negative Input MUX Selection. This field selects the negative input for the comparator. -

Page 156: Cmp1 Control Registers

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.5 CMP1 Control Registers 15.5.1 CMP1CN0: Comparator 1 Control 0 Name CPEN CPOUT CPRIF CPFIF CPHYP CPHYN Access Reset SFR Page = 0x0; SFR Address: 0x9A Name Reset Access Description CPEN Comparator Enable. -

Page 157: Cmp1Md: Comparator 1 Mode

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) Name Reset Access Description Value Name Description DISABLED Negative Hysteresis disabled. ENABLED_MODE1 Negative Hysteresis = Hysteresis 1. ENABLED_MODE2 Negative Hysteresis = Hysteresis 2. ENABLED_MODE3 Negative Hysteresis = Hysteresis 3 (Maximum). 15.5.2 CMP1MD: Comparator 1 Mode... -

Page 158: Cmp1Mx: Comparator 1 Multiplexer Selection

EFM8SB2 Reference Manual Comparators (CMP0 and CMP1) 15.5.3 CMP1MX: Comparator 1 Multiplexer Selection Name CMXN CMXP Access Reset SFR Page = 0x0; SFR Address: 0x9E Name Reset Access Description CMXN Comparator Negative Input MUX Selection. This field selects the negative input for the comparator. -

Page 159: Cyclic Redundancy Check (Crc0)

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16. Cyclic Redundancy Check (CRC0) 16.1 Introduction The cyclic redundancy check (CRC) module performs a CRC using a 16-bit or 32-bit polynomial. CRC0 accepts a stream of 8-bit data and posts the result to an internal register. In addition to using the CRC block for data manipulation, hardware can automatically CRC the flash contents of the device. -

Page 160: Functional Description

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.3 Functional Description 16.3.1 16-bit CRC Algorithm The CRC unit generates a 16-bit CRC result equivalent to the following algorithm: 1. XOR the input with the most-significant bits of the current CRC result. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF). -

Page 161: 32-Bit Crc Algorithm

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.3.2 32-bit CRC Algorithm The CRC unit generates a 32-bit CRC result equivalent to the following algorithm: 1. XOR the least-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x00000000 or 0xFFFFFFFF). -

Page 162: Writing To Crc0Cn0

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.3.3 Writing to CRC0CN0 The third op-code byte fetched from program memory following a write to CRC0CN0 that initiates a CRC0 operation is indeterminate. If the indeterminate op-code byte is the first or second byte in an instruction, improper code execution may result. Writes to CRC0CN0 that initiate a CRC0 operation must be immediately followed by a benign 3-byte instruction whose third byte is a don’t care. -

Page 163: Crc0 Control Registers

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.4 CRC0 Control Registers 16.4.1 CRC0CN0: CRC0 Control 0 Name Reserved POLYSEL CRCINIT CRCVAL CRCPNT Access Reset SFR Page = 0xF; SFR Address: 0x92 Name Reset Access Description Reserved Must write reset value. -

Page 164: Crc0In: Crc0 Data Input

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.4.2 CRC0IN: CRC0 Data Input Name CRC0IN Access Reset 0x00 SFR Page = 0xF; SFR Address: 0x93 Name Reset Access Description CRC0IN 0x00 CRC Data Input. Each write to CRC0IN results in the written data being computed into the existing CRC result according to the CRC algo- rithm. -

Page 165: Crc0Cnt: Crc0 Automatic Flash Sector Count

EFM8SB2 Reference Manual Cyclic Redundancy Check (CRC0) 16.4.5 CRC0CNT: CRC0 Automatic Flash Sector Count Name Reserved CRCCNT Access Reset 0x00 SFR Page = 0xF; SFR Address: 0x97 Name Reset Access Description Reserved Must write reset value. CRCCNT 0x00 Automatic CRC Calculation Block Count. -

Page 166: Programmable Counter Array (Pca0)

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17. Programmable Counter Array (PCA0) 17.1 Introduction The programmable counter array (PCA) provides multiple channels of enhanced timer and PWM functionality while requiring less CPU intervention than standard counter/timers. The PCA consists of a dedicated 16-bit counter/timer and one 16-bit capture/compare mod- ule for each channel. -

Page 167: Functional Description

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3 Functional Description 17.3.1 Counter / Timer The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte of the 16-bit counter/timer and PCA0L is the low byte. Reading PCA0L automatically latches the value of PCA0H into a “snapshot” register; the following PCA0H read accesses this “snapshot”... - Page 168 EFM8SB2 Reference Manual Programmable Counter Array (PCA0) Table 17.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules Operational Mode PCA0CPMn PCA0PWM Bit Name Capture triggered by positive edge on CEXn Capture triggered by negative edge on CEXn Capture triggered by any transition on...

-

Page 169: Edge-Triggered Capture Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.4 Edge-Triggered Capture Mode In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). -

Page 170: Software Timer (Compare) Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.5 Software Timer (Compare) Mode In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN0 is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. -

Page 171: High-Speed Output Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.6 High-Speed Output Mode In High-Speed Output mode, a module’s associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the capture/compare flag (CCFn) in PCA0CN0 is set to logic 1. -

Page 172: Frequency Output Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.7 Frequency Output Mode Frequency Output Mode produces a programmable-frequency square wave on the module’s associated CEXn pin. The capture/ compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is... - Page 173 EFM8SB2 Reference Manual Programmable Counter Array (PCA0) Edge Aligned PWM When configured for edge-aligned mode, a module generates an edge transition at two points for every 2 PCA clock cycles, where N is the selected PWM resolution in bits. In edge-aligned mode, these two edges are referred to as the “match” and “overflow” edges. The polarity at the output pin is selectable and can be inverted by setting the appropriate channel bit to 1 in the PCA0POL register.

-

Page 174: To 11-Bit Pwm Modes

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.8.1 8 to 11-Bit PWM Modes Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequen- cy of the output is dependent on the timebase for the PCA counter/timer and the setting of the PWM cycle length (8 through 11-bits). -

Page 175: Watchdog Timer Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.3.9 Watchdog Timer Mode A programmable watchdog timer (WDT) function is available through the last PCA module (module 5). The WDT is used to generate a reset if the time between writes to the WDT update register (PCA0CPH5) exceed a specified limit. The WDT can be configured and enabled/disabled as needed by software. - Page 176 EFM8SB2 Reference Manual Programmable Counter Array (PCA0) Watchdog Timer Usage To configure the WDT, perform the following tasks: 1. Disable the WDT by writing a 0 to the WDTE bit. 2. Select the desired PCA clock source (with the CPS field).

-

Page 177: Pca0 Control Registers

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4 PCA0 Control Registers 17.4.1 PCA0CN0: PCA Control 0 Name CCF5 CCF4 CCF3 CCF2 CCF1 CCF0 Access Reset SFR Page = 0x0; SFR Address: 0xD8 (bit-addressable) Name Reset Access Description PCA Counter/Timer Overflow Flag. -

Page 178: Pca0Md: Pca Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.2 PCA0MD: PCA Mode Name CIDL WDTE WDLCK Reserved Access Reset SFR Page = 0x0; SFR Address: 0xD9 Name Reset Access Description CIDL PCA Counter/Timer Idle Control. Specifies PCA behavior when CPU is in Idle Mode. - Page 179 EFM8SB2 Reference Manual Programmable Counter Array (PCA0) Name Reset Access Description Value Name Description OVF_INT_DISABLED Disable the CF interrupt. OVF_INT_ENABLED Enable a PCA Counter/Timer Overflow interrupt request when CF is set. When the WDTE bit is set to 1, the other bits in the PCA0MD register cannot be modified. To change the contents of the PCA0MD register, the Watchdog Timer must first be disabled.

-

Page 180: Pca0Pwm: Pca Pwm Configuration

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.3 PCA0PWM: PCA PWM Configuration Name ARSEL ECOV COVF Reserved CLSEL Access Reset SFR Page = 0x0; SFR Address: 0xDF Name Reset Access Description ARSEL Auto-Reload Register Select. This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload reg- isters at the same SFR addresses. -

Page 181: Pca0L: Pca Counter/Timer Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.4 PCA0L: PCA Counter/Timer Low Byte Name PCA0L Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xF9 Name Reset Access Description PCA0L 0x00 PCA Counter/Timer Low Byte. The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. -

Page 182: Pca0Cpm0: Pca Channel 0 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.6 PCA0CPM0: PCA Channel 0 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xDA Name Reset Access Description PWM16 Channel 0 16-bit Pulse Width Modulation Enable. -

Page 183: Pca0Cpl0: Pca Channel 0 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.7 PCA0CPL0: PCA Channel 0 Capture Module Low Byte Name PCA0CPL0 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xFB Name Reset Access Description PCA0CPL0 0x00 PCA Channel 0 Capture Module Low Byte. -

Page 184: Pca0Cpm1: Pca Channel 1 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.9 PCA0CPM1: PCA Channel 1 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xDB Name Reset Access Description PWM16 Channel 1 16-bit Pulse Width Modulation Enable. -

Page 185: Pca0Cpl1: Pca Channel 1 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.10 PCA0CPL1: PCA Channel 1 Capture Module Low Byte Name PCA0CPL1 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xE9 Name Reset Access Description PCA0CPL1 0x00 PCA Channel 1 Capture Module Low Byte. -

Page 186: Pca0Cpm2: Pca Channel 2 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.12 PCA0CPM2: PCA Channel 2 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xDC Name Reset Access Description PWM16 Channel 2 16-bit Pulse Width Modulation Enable. -

Page 187: Pca0Cpl2: Pca Channel 2 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.13 PCA0CPL2: PCA Channel 2 Capture Module Low Byte Name PCA0CPL2 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xEB Name Reset Access Description PCA0CPL2 0x00 PCA Channel 2 Capture Module Low Byte. -

Page 188: Pca0Cpm3: Pca Channel 3 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.15 PCA0CPM3: PCA Channel 3 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xDD Name Reset Access Description PWM16 Channel 3 16-bit Pulse Width Modulation Enable. -

Page 189: Pca0Cpl3: Pca Channel 3 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.16 PCA0CPL3: PCA Channel 3 Capture Module Low Byte Name PCA0CPL3 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xED Name Reset Access Description PCA0CPL3 0x00 PCA Channel 3 Capture Module Low Byte. -

Page 190: Pca0Cpm4: Pca Channel 4 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.18 PCA0CPM4: PCA Channel 4 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xDE Name Reset Access Description PWM16 Channel 4 16-bit Pulse Width Modulation Enable. -

Page 191: Pca0Cpl4: Pca Channel 4 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.19 PCA0CPL4: PCA Channel 4 Capture Module Low Byte Name PCA0CPL4 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xFD Name Reset Access Description PCA0CPL4 0x00 PCA Channel 4 Capture Module Low Byte. -

Page 192: Pca0Cpm5: Pca Channel 5 Capture/Compare Mode

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.21 PCA0CPM5: PCA Channel 5 Capture/Compare Mode Name PWM16 ECOM CAPP CAPN ECCF Access Reset SFR Page = 0x0; SFR Address: 0xCE Name Reset Access Description PWM16 Channel 5 16-bit Pulse Width Modulation Enable. -

Page 193: Pca0Cpl5: Pca Channel 5 Capture Module Low Byte

EFM8SB2 Reference Manual Programmable Counter Array (PCA0) 17.4.22 PCA0CPL5: PCA Channel 5 Capture Module Low Byte Name PCA0CPL5 Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xD2 Name Reset Access Description PCA0CPL5 0x00 PCA Channel 5 Capture Module Low Byte. -

Page 194: External Memory Interface (Emif0)

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18. External Memory Interface (EMIF0) 18.1 Introduction The External Memory Interface (EMIF) enables access of off-chip memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) with the target address specified in either 8-bit or 16-bit formats. -

Page 195: Functional Description

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.3 Functional Description 18.3.1 Overview The devices include RAM mapped into the external data memory space (XRAM). Devices with enough pins also have an External Memory Interface (EMIF0) which can be used to access off-chip memories and memory-mapped devices connected to the GPIO ports. - Page 196 Address Bit 10 P2.2 P2.2 Not Available A11m Address Bit 11 P2.3 P2.3 Not Available Note: 1. EFM8SB2 devices support only multiplexed EMIF modes. 2. EFM8SB2 devices support up to 12 address lines. silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 195...

-

Page 197: Multiplexed External Memory Interface

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.3.3 Multiplexed External Memory Interface For a Multiplexed external memory interface, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]m. For most devices with an 8-bit interface, the upper address bits are not used and can be used as GPIO if the external memory interface is used in 8-bit non-banked mode. -

Page 198: Operating Modes

EFM8SB2 Reference Manual External Memory Interface (EMIF0) A[15:8]m Address Bus A[15:8] 74HC373 ALEm AD[7:0]m Address/Data Bus A[7:0] 4K X 8 EMIF SRAM (Optional) I/O[7:0] Figure 18.3. Multiplexed to Non-Multiplexed Configuration Example 18.3.4 Operating Modes The external data memory space can be configured in one of four operating modes based on the EMIF Mode bits in the EMI0CF regis- ter. - Page 199 EFM8SB2 Reference Manual External Memory Interface (EMIF0) Internal Only In Internal Only mode, all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap and will always target on-chip XRAM. As an example, if the entire address space is consecutively written and the data pointer is incremented after each write, the write pointer will always point to the first byte of on-chip XRAM after the last byte of on-chip XRAM has been written.

-

Page 200: Timing

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.3.5 Timing The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RDb and WRb strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods. -

Page 201: Multiplexed Mode

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.3.5.1 Multiplexed Mode Figure 18.5 Multiplexed 16-bit MOVX Timing on page 200 through Figure 18.7 Multiplexed 8-bit MOVX with Bank Select Timing on page 202 show the timing diagrams for the different External Memory Interface multiplexed modes and MOVX operations. - Page 202 EFM8SB2 Reference Manual External Memory Interface (EMIF0) Muxed 8-bit Write Without Bank Select A[15:8]m Port Latch Controlled (GPIO) A[15:8]m AD[7:0]m EMIF Address (8 LSBs) from R0 or R1 EMIF Write Data AD[7:0]m ALEH ALEL ALEm ALEm Muxed 8-bit Read Without Bank Select...

- Page 203 EFM8SB2 Reference Manual External Memory Interface (EMIF0) Muxed 8-bit Write with Bank Select A[15:8]m EMIF Address (8 MSBs) from EMI0CN A[15:8]m AD[7:0]m EMIF Address (8 LSBs) from R0 or R1 EMIF Write Data AD[7:0]m ALEH ALEL ALEm ALEm Muxed 8-bit Read with Bank Select...

-

Page 204: Emif0 Control Registers

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.4 EMIF0 Control Registers 18.4.1 EMI0CN: External Memory Interface Control Name Reserved PGSEL Access Reset 0x00 SFR Page = 0x0; SFR Address: 0xAA Name Reset Access Description Reserved Must write reset value. PGSEL 0x00 XRAM Page Select. -

Page 205: Emi0Cf: External Memory Configuration

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.4.2 EMI0CF: External Memory Configuration Name Reserved EALE Access Reset SFR Page = 0x0; SFR Address: 0xAB Name Reset Access Description Reserved Must write reset value. EMIF Operating Mode Select. Value Name Description INTERNAL_ONLY Internal Only: MOVX accesses on-chip XRAM only. -

Page 206: Emi0Tc: External Memory Timing Control

EFM8SB2 Reference Manual External Memory Interface (EMIF0) 18.4.3 EMI0TC: External Memory Timing Control Name ASETUP PWIDTH AHOLD Access Reset SFR Page = 0x0; SFR Address: 0xAF Name Reset Access Description ASETUP EMIF Address Setup Time. Value Name Description 0_CLOCKS Address setup time = 0 SYSCLK cycles. - Page 207 EFM8SB2 Reference Manual External Memory Interface (EMIF0) Name Reset Access Description 3_CLOCKS Address hold time = 3 SYSCLK cycles. silabs.com | Smart. Connected. Energy-friendly. Rev. 0.1 | 206...

-

Page 208: Serial Peripheral Interfaces (Spi0 And Spi1)