User Manuals: Renesas RL78/F14 Microcontrollers

Manuals and User Guides for Renesas RL78/F14 Microcontrollers. We have 5 Renesas RL78/F14 Microcontrollers manuals available for free PDF download: User Manual

Renesas RL78/F14 User Manual (1879 pages)

16-Bit Single-Chip Microcontrollers

Brand: Renesas

|

Category: Microcontrollers

|

Size: 21 MB

Table of Contents

-

-

-

P140 (Port 14)111

-

Reset113

-

Regc113

-

-

Memory Space120

-

Mirror Area150

-

SFR Addressing222

-

Based Addressing224

-

Stack Addressing229

-

-

-

-

X1 Oscillator427

-

XT1 Oscillator427

-

PLL Circuit431

-

Usage Notes455

-

-

-

I/O Pins576

-

Operation588

-

Timer Mode589

-

-

-

Registers601

-

Operation645

-

PWM Function665

-

PWM3 Mode676

-

Count Source682

-

-

-

-

-

-

Operation819

-

Noise Filter820

-

-

Master Reception876

-

Slave Reception906

-

Master Reception940

-

Slave Reception970

-

UART Reception1002

-

LIN Reception1017

-

Data Transmission1032

-

Data Reception1037

-

-

Pin Configuration1069

-

Start Conditions1072

-

Addresses1073

-

Acknowledge (ACK)1074

-

Stop Condition1075

-

Wait1076

-

Canceling Wait1078

-

Arbitration1081

-

Wakeup Function1083

-

Cautions1090

-

Timing Charts1119

-

-

Registers for UART1197

-

Modes1227

-

LIN Reset Mode1229

-

LIN Mode1230

-

UART Mode1232

-

LIN Mode1233

-

Status1248

-

Error Status1250

-

UART Mode1256

-

Status1274

-

Error Status1275

-

LIN Self-Test Mode1276

-

Baud Rate Generator1283

-

LIN Slave Mode1285

-

UART Mode1287

-

Noise Filter1288

-

Interrupts1290

-

-

Input/Output Pins1294

-

CAN Modes1412

-

Channel Modes1414

-

Reception Function1419

-

Timestamp1421

-

Test Function1427

-

Interrupt1429

-

RAM Window1433

-

Initial Settings1434

-

Clock Setting1436

-

Receive Rule Setting1439

-

Buffer Setting1440

-

Reception Procedure1442

-

Test Settings1454

-

-

Chapter 19 Dtc

1458-

Registers1460

-

DTC Vector Table1464

-

Operation1481

-

Normal Mode1483

-

Repeat Mode1485

-

Chain Transfers1489

-

Notes on DTC1492

-

DTC Response Time1496

-

-

Advertisement

Renesas RL78/F14 User Manual (59 pages)

Emulator

Brand: Renesas

|

Category: Computer Hardware

|

Size: 1 MB

Table of Contents

-

Overview7

-

RESET# Pin25

-

TOOL0 Pin28

-

Gnd29

-

VDD29

-

Reset46

-

Flash Memory46

-

Gdidis47

-

Go to Here]49

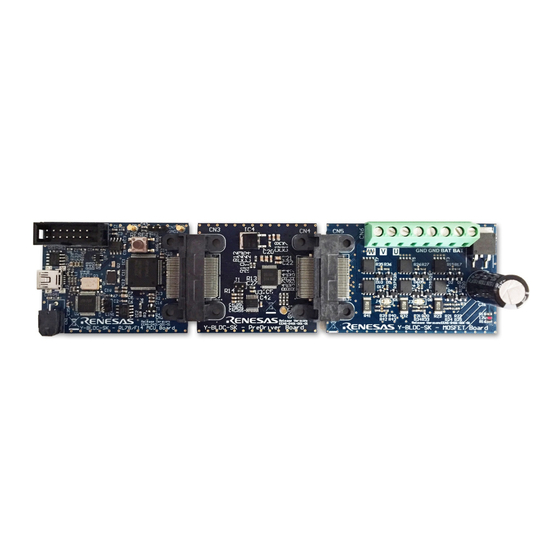

Renesas RL78/F14 User Manual (101 pages)

BLDC Starter Kit

Brand: Renesas

|

Category: Controller

|

Size: 5 MB

Table of Contents

Advertisement

Renesas RL78/F14 User Manual (58 pages)

E1/E20/E2 Emulator, E2 Emulator Lite

Brand: Renesas

|

Category: Computer Hardware

|

Size: 0 MB

Table of Contents

-

Overview7

-

RESET# Pin25

-

TOOL0 Pin28

-

Gnd29

-

VDD29

-

Reset46

-

Flash Memory46

-

Gdidis47

-

Go to Here]49

Renesas RL78/F14 User Manual (55 pages)

Brand: Renesas

|

Category: Computer Hardware

|

Size: 0 MB

Table of Contents

-

-

-

-

-

RESET# Pin25

-

TOOL0 Pin28

-

Gnd29

-

VDD29

-

-

-

Reset45

-

Flash Memory45

-

Gdidis46

-

-

Go to Here]48