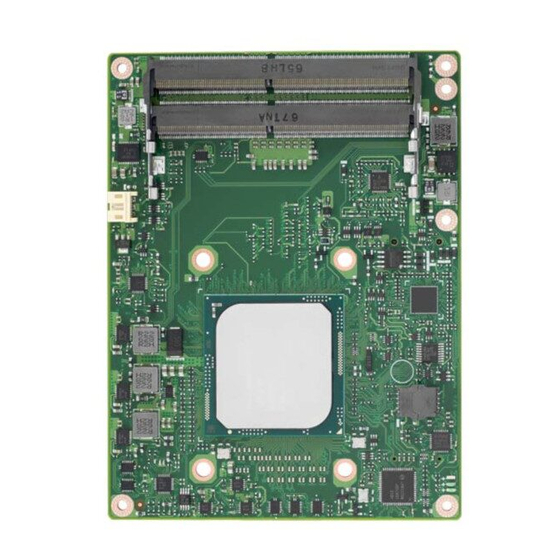

Advantech SOM-5992 Manuals

Manuals and User Guides for Advantech SOM-5992. We have 2 Advantech SOM-5992 manuals available for free PDF download: Design Manual, User Manual

Advantech SOM-5992 Design Manual (129 pages)

COM Express, COMe TYPE7

Brand: Advantech

|

Category: Single board computers

|

Size: 4 MB

Table of Contents

Advertisement

Advantech SOM-5992 User Manual (112 pages)

Intel Xeon Processor D-1500

COM Express R3.0 Type 7

Module

Brand: Advantech

|

Category: Computer Hardware

|

Size: 2 MB