Summary of Contents for Acrosser Technology AR-B1320 CPU

- Page 1 ’ ’ AR-B1320 PC/104 386SX CPU BOARD User’ s Guide Edition: 1.2...

-

Page 2: Copyright Notice And Disclaimer

Furthermore, Acrosser Technology reserves the right to revise this publication and to make changes from time to time in the contents hereof without obligation of Acrosser Technology to notify any person of such revisions or changes. Check for updates at www.acrosser.com Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Acrosser or an authorized sublicensor. -

Page 3: Table Of Contents

’ ’ Table of Contents PREFACE............................V WELCOME TO THE AR-B1320 CPU BOARD.................V BEFORE YOU USE THIS GUIDE ....................V RETURNING YOUR BOARD FOR SERVICE .................V TECHNICAL SUPPORT AND USER COMMENTS.................V ORGANIZATION ........................... VI STATIC ELECTRICITY PRECAUTIONS ..................VI OVERVIEW ..........................1-1 INTRODUCTION........................... - Page 4 ’ ’ 3.15.3 WD TIMER COUNTER(24 BITS) - INDEX 39H, 3AH, AND 3BH............3-14 3.15.4 TIMEOUT STATUS & RESET WATCHDOG - INDEX 3CH............... 3-15 3.15.5 PROGRAMMING WATCHDOG - BASIC OPERATION..............3-15 3.16 USING THE FLASH DISK......................3-16 3.16.1 SSD CONFIGURATION ........................3-17 3.16.2 SOFTWARE PROGRAMMING ......................

-

Page 5: Preface

If you have suggestions for improving particular sections or if you find any errors, please indicate the manual title and book number. Please send your comments to Acrosser Technology Co., Ltd. or your local sales representative. Send Internet electronic mail to: Sales@acrosser.com... -

Page 6: Organization

’ ’ ORGANIZATION This information covers the following topics (see the Table of Contents for a detailed listing): Chapter 1, “Overview,” provides an overview of the system features and packing list. Chapter 2, “System Controller,” describes the major structure. Chapter 3, “Setting the System,” describes how to adjust the jumpers, and the connector settings. -

Page 7: Overview

’ ’ OVERVIEW This chapter provides an overview of your system features and capabilities. The following topics are covered: Introduction Packing List Features INTRODUCTION The AR-B1320, PC/104 CPU module is a lower power consuming, high performance 386 based computer. By using the space-saving features of the ALI M6117C CPU, this module is able to support up to 4MB of DRAM and 1.5 MB of Flash memory on board. -

Page 8: Features

’ ’ FEATURES This system provides a number of special features that enhance its reliability, ensure its availability, and improve its expansion capabilities, as well as its hardware structure. 80386SX-40 MHz CPU PC/104 extension bus System of up to 4MB DRAM (2 MB already on-board) Supports 2 RS-232C/RS-485 serial ports PC/AT compatible keyboard interface Supports up to 1.5MB flash disk... -

Page 9: System Controller

’ ’ SYSTEM CONTROLLER This chapter describes the major structure. The following topics are covered: Microprocessor DMA Controller DRAM Configuration I/O Port Address Map Interrupt Controller Serial Port Parallel Port Timer Real-Time Clock and Non-Volatile RAM Watch-Dog Timer FLASH Disk MICROPROCESSOR The AR-B1320 uses the ALI M6117C CPU;... -

Page 10: Dram Configuration

’ ’ DRAM CONFIGURATION There are two 16-bit memory banks on the AR-B1320 board. The first bank is embedded with a 1MBx16-bit (2MB, 60ns) EDO RAM and the other is 42-pin SOJ socket for extra 2MB DRAM with 1MBx16-bit (2MB, 60ns) EDO RAM. -

Page 11: I/O Port Address Map

’ ’ I/O PORT ADDRESS MAP Hex Range Device Factory Preset 000-01F DMA controller 1 020-021 Interrupt controller 1 022-023 ALI M6117C chipset address 040-04F Timer 1 050-05F Timer 2 060-06F 8042 keyboard/controller 070-071 Real-time clock (RTC), non-maskable interrupt (NMI) 080-09F DMA page registers 0A0-0A1... -

Page 12: Interrupt Controller

’ ’ INTERRUPT CONTROLLER The ALI M6117C also provides two cascaded 8259 Programmable Interrupt Controllers (PIC). They accept requests from the peripherals, resolve priorities on pending interrupts in service, issue interrupt requests to the CPU, and provide vectors which are used as acceptance indexed by the CPU to determine which interrupt service routine should be executed. -

Page 13: Serial Ports

’ ’ SERIAL PORTS The ACEs (Asynchronous Communication Elements ACE1 and ACE2) are used to convert the parallel data to a serial format on the transmit side and convert the serial data to parallel on the receiver side. The serial format, in order of transmission and reception, is a start bit, followed by five to eight data bits, a parity bit (if programmed) and one, one and half (five-bit format only) or two stop bits. - Page 14 ’ ’ Line Control Register (LCR) Bit 0: Word Length Select Bit 0 (WLS0) Bit 1: Word Length Select Bit 1 (WLS1) WLS1 WLS0 Word Length 5 Bits 6 Bits 7 Bits 8 Bits Bit 2: Number of Stop Bit (STB) Bit 3: Parity Enable (PEN) Bit 4: Even Parity Select (EPS) Bit 5: Stick Parity...

-

Page 15: Parallel Port

’ ’ Divisor Latch (LS, MS) Byte Data Bit 0: Bit 0 Bit 8 Bit 1: Bit 1 Bit 9 Bit 2: Bit 2 Bit 10 Bit 3: Bit 3 Bit 11 Bit 4: Bit 4 Bit 12 Bit 5: Bit 5 Bit 13 Bit 6:... - Page 16 ’ ’ (3) Data Swapper The system microprocessor can read the contents of the printer's Data Latch through the Data Swapper by reading the Data Swapper address. (4) Printer Status Buffer The system microprocessor can read the printer status by reading the address of the Printer Status Buffer.

-

Page 17: Timer

’ ’ TIMER The AR-B1320 provides three programmable timers, each with a timing frequency of 1.19 MHz. Timer 0 The output of this timer is tied to interrupt request 0. (IRQ 0) Timer 1 This timer is used to trigger memory refresh cycles. Timer 2 This timer provides the speaker tone. -

Page 18: Real-Time Clock And Non-Volatile Ram

’ ’ 2.10 REAL-TIME CLOCK AND NON-VOLATILE RAM The AR-B1320 contains a real-time clock compartment that maintains the date and time in addition to storing configuration information about the computer system. It contains 14 bytes of clock and registers and 114 bytes of general purpose RAM. Because of the use of CMOS technology, it consumes very little power and can be maintained for long periods of time using an internal lithium battery. -

Page 19: Watchdog Timer

2.12 FLASH DISK The AR-B1320 supports three kinds of flash disks. They are Acrosser’ s SSD, DiskOnChip, and DiskOnModule. For the SSD, AR-B1320 provides two 32-pin PLCC sockets and 1 32-pin JEDEC DIP socket, which may be populated with up to 1.5MB of flash disk. The 32-pin JEDEC DIP socket supports the DiskOnChip from 2MB to 144MB. -

Page 21: Setting The System

’ ’ SETTING THE SYSTEM This section describes the pin assignments of all connectors and settings of all switches and jumpers. It also guides you on how to expand the system and control the onboard devices. The jumper pins allow you to set specific system parameters. Set them by changing the pin location of jumper blocks. -

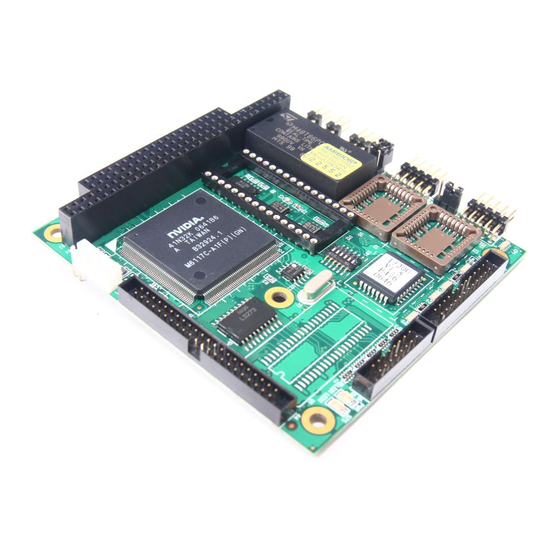

Page 22: Board Layout

’ ’ BOARD LAYOUT The AR-B1320 is a small, easy to use, all-in-one 386SX grade CPU board with 2 RS-232/RS-485 ports and a flash disk. Below is the AR-B1320 board layout. LED1 LED2 [M1] BIOS [M2] SSD/DOC [M3] AR-B1320 VER:1.1 Figure 3-1 AR-B1320 Board Layout... - Page 23 ’ ’ Name Function Section CPU base clock select RS-485 terminator select (COM-A) 3.11.3 RS-485 terminator select (COM-B) 3.11.3 Switch 1 The base I/O address of SSD selector Switch 2 The memory segment of SSD selector Switch 3 The memory segment of DiskOnChip selector Switch 4 Reserved Switch 5...

-

Page 24: Cpu Base Clock Select (Jp1)

’ ’ CPU BASE CLOCK SELECT (JP1) This board provides six types of CPU input clocks; they are 33.3MHz, 50MHz, 60MHz, 66.7MHz, 75MHz, and 80MHz. The CPU input clock is twice that of the operating clock. JP1 is a 6-pin jumper located between CN3 and CN4. -

Page 25: Keyboard Connector (J2)

’ ’ KEYBOARD CONNECTOR (J2) The J2 is a 6-pin 2.0mm JST connector. Use the keyboard adapter cable to connect a PS/2 type keyboard. The following shows the pin assignment of the adapter cable. 6 Pin Mini-Din 1 Reserved 1 DATA 2 KB Data 2 N.C. -

Page 26: Power Connector (J5)

’ ’ POWER CONNECTOR (J5) The J5 is a 4-pin, 2.5mm, right angle JST connector; you can directly connect the DC power source to J5 for stand-alone applications. 1: VCC (+5V) 2: GND 3: GND 4: +12V Front View Figure 3-7 J5: Power Connector PRINTER CONNECTOR (CN1) To enable or disable the printer port, please use the BIOS Setup program. -

Page 27: Floppy Connector (Cn2)

’ ’ 3.10 FLOPPY CONNECTOR (CN2) The AR-B1320 provides a 16-pin 2.0mm connector (CN2) to support one floppy disk drive. The floppy drives may be one of the following: • 5.25" : 360K or 1.2M • 3.5" : 720K or 1.44M To enable or disable the floppy disk controller, please use the BIOS Setup program. -

Page 28: Rs-232C Connectors (Cn3 & Cn4)

’ ’ 3.11.1 RS-232C CONNECTORS (CN3 & CN4) CN3 is the RS-232C- interface connector of COM-A port and CN4 is the RS-232C connector for the COM-B port. They are both 10-pin 2.54mm right angle headers. AR-B1320 provides 2 adapter cables to transfer to the PC/AT standard connector (DB9 male). The next figure and table show the pin definitions of the adapter cable: CN3 &... -

Page 29: Rs-485 Terminator (Jp2 & Jp3)

’ ’ 3.11.3 RS-485 TERMINATOR (JP2 & JP3) JP2 & JP3 are used to enable the RS-485 terminator resistor of COM-A and COM-B port respectively. The value of the terminator resistor is 150 ohms. Close the jumper to enable the RS-485 terminator and leave the jumper open to disable it. -

Page 30: Pc/104 Connector (Cn7 & Cn8)

’ 3.13 PC/104 CONNECTOR (CN7 & CN8) The AR-B1320 CPU board has the stack-through expandable feature. You may stack a PC/104 module from either the back side or front side of this board through the PC-104 connector. 3.13.1 64 PIN PC/104 CONNECTOR – CN8 (BUS A & B) -

Page 31: Pc/104 Channel Signal Description

’ ’ 3.13.3 PC/104 CHANNEL SIGNAL DESCRIPTION Name Description BUSCLK [Output] The BUSCLK signal of the I/O channel is asynchronous to the CPU clock. RSTDRV [Output] This signal goes high during power-up, low line-voltage or hardware reset SA0 – SA19 [Input / Output] The System Address lines run from bit 0 to 19. -

Page 32: Led Indicator (Led1 & Led2)

’ ’ 3.14 LED INDICATOR (LED1 & LED2) AR-B1320 provides 2 on-board LEDs; one is power LED and the other is user-defined status LED. Both LEDs are located at the right-hand corner of the board next to the CN2 floppy connector. 3.14.1 POWER LED (LED1) This LED indicates if the VCC(+5V) power is supplied or not. -

Page 33: Using The Watchdog Timer

’ ’ The following table illustrates the flash rate information. FR-Data Flash Rate (Hz) Remark 00h-09h Reserved The flash rate is too fast to see 3.15 USING THE WATCHDOG TIMER This section describes how to use, disable, and enable the watchdog timer. 3.15.1 WD ENABLE REGISTER - INDEX 37H This register is used to enable or disable the watchdog timer. -

Page 34: Wd Report Register - Index 38H

’ ’ 3.15.2 WD REPORT REGISTER - INDEX 38H This register is used to select the watchdog report when the watchdog times out. Bit 7-4 Watchdog Timer Time-out Report Signal Select 0000 No output signal 0001 IRQ3 selected 0010 IRQ4 selected 0011 IRQ5 selected 0100... -

Page 35: Timeout Status & Reset Watchdog - Index 3Ch

’ ’ 3.15.4 TIMEOUT STATUS & RESET WATCHDOG - INDEX 3CH Bit 7(read only) 0: Timer timeout not happened 1: Timer timeout happened Bit 6 Write this bit “1” to reset timer Bit 0-5 The value on this bit has no meaning. Other function. -

Page 36: Using The Flash Disk

’ ’ (4) Write Data to Configuration Register Example 1: Write data 68h to INDEX 3Bh Unlock_Cfg_Reg ;Unlock configuration register al, 3bh ;Points to index 3bh 22h, al al, 68h 23h, al ;Write data Lock_Cfg_Reg ;Lock configuration register Note: The utility diskette includes the watchdog utility files, “WD6117C.EXE” and “WD6117C.CPP.” “WD6117C.EXE”... -

Page 37: Ssd Configuration

’ ’ 3.16.1 SSD CONFIGURATION The SSD function enables you to use 5V FLASH, allowing you to directly program the flash without having to purchase any additional programming equipment to write or erase data. You can format the flash disk and copy files onto flash disk just like using a floppy disk. If you would like to update 1 or more files to the flash disk, you just copy these files onto the flash disk, you don’... -

Page 38: Diskonmodule

’ ’ 3.16.3 DISKONMODULE AR-B1320 provides DiskOnModule function which is interfaced with the 44-pin hard disk connector. Align the pin 1 of the DiskOnModule with the hard disk connector; the module functions just like a hard disk. 3-18... -

Page 39: Bios Console

’ ’ BIOS CONSOLE This chapter describes the AR-B1320 BIOS menu and explains how to perform the common tasks required to get the system up and running, and it also presents detailed explanations of the elements found in each of the BIOS menu. The following topics are covered: BIOS Setup Overview Standard CMOS Setup Advanced CMOS Setup... -

Page 40: Standard Cmos Setup

1) The factory-default settings are set according to the <Auto Configuration with Optimal Settings>. Acrosser recommends the user use the BIOS default settings unless he/she is very familiar with the setting functions, or contact the technical support engineer for service. - Page 41 ’ ’ Hard Disk Setup The BIOS supports various types for the user settings. The BIOS supports <Pri Master> and <Pri Slave>, so the user can install up to two hard disks. For the master and slave jumpers, please refer to the hard disk’...

-

Page 42: Advanced Cmos Setup

’ ’ ADVANCED CMOS SETUP The <Advanced CMOS SETUP> option consists of configuration entries that allow you to improve your system performance, or let you set up some system features according to your preference. Some entries here are required by the CPU board’ s design to remain in their default settings. Available Options Figure 4-3 BIOS: Advanced CMOS Setup 1st Boot Device... - Page 43 ’ ’ BootUp Num-Lock This item is used to activate the Num-Lock function upon system boot. If the setting is on, after a boot, the Num-Lock light is lit, and user can use the number key. Available options: On, Off Floppy Drive Swap The option reverses the drive letter assignments of your floppy disk drives in the Swap A, B setting;...

- Page 44 ’ ’ C000, 32k Shadow C800, 32k Shadow D000, 32k Shadow D800, 32k Shadow These options control the location of the contents of the 16KB of ROM beginning at the specified memory location. If no adapter ROM is using the named ROM area, this area is made available to the local bus.

-

Page 45: Advanced Chipset Setup

14.318/2, PLCK2/3, PLCK2/4, PLCK2/5, PLCK2/6, PLCK2/8, PLCK2/10, PLCK2/12 NOTE: 1) PLCK means the CPU input clock. 2) Acrosser recommends the user set this function at the range from 8MHz to 10MHz. Slow Refresh This option sets the DRAM refresh cycle time. - Page 46 ’ ’ I/O Recovery/ I/O Recovery Period If I/O Recovery Feature options is enabled, the BIOS inserts a delay time between two I/O commands. The delay time is defined in I/O Recovery Period option. Available options for I/O Recovery: Enable, Disable Available options for I/O Recovery Period: 0 us, 0.25 us, 0.50 us, 0.75 us, 1.00 us, 1.25 us, 1.50 us, 1.75 us, 2.00 us, 2.25 us, 2.50 us, 2.75 us, 3.00us, 3.25us, 3.50 us 16Bit ISA Insert Wait...

-

Page 47: Peripheral Setup

’ ’ PERIPHERAL SETUP This section is used to configure the peripheral features. Figure 4-5 BIOS: Peripheral Setup Hard Disk Delay If this option is set to Disabled and the system BIOS executes too fast, the result is that the BIOS can’ t find the hard disk drive. -

Page 48: Auto-Detect Hard Disks

’ ’ OnBoard Serial Port2 IRQ This option selects the IRQ for the onboard serial port2. Available options: 3, 4, 5, 9 Onboard Parallel Port This option configures the onboard the parallel port. Available options: Auto, Disabled, 378, 278, 3BC Parallel Port Mode This option specifies the parallel port mode. -

Page 49: Load The Default Setting

’ ’ LOAD THE DEFAULT SETTING This section permits you to select a group of settings for all BIOS Setup options. Not only can you use these items to quickly set system configuration parameters, you can choose a group of settings that have a better chance of working when the system is having configuration related problems. -

Page 50: Bios Update

’ ’ 4.11 BIOS UPDATE The BIOS program instructions are contained within the computer chips called FLASH ROM that is located on your system board. The chip can be electronically reprogrammed, allowing you to upgrade your BIOS firmware without removing and re-installing it. The AR-B1320 provides a FLASH BIOS update function for you to easily upgrade to a new BIOS version. - Page 51 ’ ’...

-

Page 53: Appendix

’ ’ APPENDIX SPECIFICATIONS CPU & Chipset: ALI M6117C, 33/40 MHz Bus Interface: PC/104 bus DRAM: Up to 4MB with 2 MB on-board Serial Port: 2 full RS-232C ports with 10-pin header, or 2 RS-485 ports for twisted pair multi-drop use IDE: One 44-pin 2.0 mm connector supports 2 IDE drives... -

Page 54: Supported Flash Memory

’ ’ SUPPORTED FLASH MEMORY The AR-B1320 supports small page 5V Flash memory listed as follows: Brand Model Specification ATMEL AT29C512 (64KX8, 512K bits) PH29EE512 (64KX8, 512K bits) ATMEL AT29C010 (128KX8, 1M bits) 28EE010 (128KX8, 1M bits) 29EE011 (128KX8, 1M bits) PH29EE010 (128KX8, 1M bits) WINBOND... -

Page 55: Board Dimensions

’ ’ AR-B1320 Ver 1.1 BOARD DIMENSIONS 1350 1500 125*5 2405 2795 3350 3550 Unit: mil (1 inch=1000 mil) -

Page 56: Programming The Rs-485

Step 2: Disable DTR (Data Terminal Relay) the bit 0 of the address of offset+4 just sets to “0”. åNOTE: Control the AR-B1320 CPU card’ s DTR signal to enable/disable the RS-485’ s TXC communication. (2) Send out one character (Transmit) Step 1: Enable the DTR signal, and the bit 0 of the address of offset+4 just sets to “1”. - Page 57 ’ ’ (4) Receive data The RS-485 operation of receiving data is the same as RS-232’ s. (5) Basic Language Example a.) Initial 86C450 UART 10 OPEN “COM1:9600,m,8,1”AS #1 LEN=1 20 REM Reset DTR 30 OUT &H3FC, (INP(%H3FC) AND &HFA) 40 RETURN b.) Send out one character to COM1 10 REM Enable transmitter by setting DTR ON...

Need help?

Do you have a question about the AR-B1320 CPU and is the answer not in the manual?

Questions and answers