Table of Contents

Advertisement

Quick Links

UM11853

KITPF5030FRDMEVM evaluation board

Rev. 1.0 — 7 March 2023

Document information

Information

Keywords

Abstract

Content

PF5030, KITPF5030FRDMEVM, KL25Z, I

The KITPF5030FRDMEVM provides flexibility to explore all the features of the device and make

measurements on the main part of the application.

2

C, spf-53090

User manual

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for NXP Semiconductors KITPF5030FRDMEVM

- Page 1 Rev. 1.0 — 7 March 2023 User manual Document information Information Content Keywords PF5030, KITPF5030FRDMEVM, KL25Z, I C, spf-53090 Abstract The KITPF5030FRDMEVM provides flexibility to explore all the features of the device and make measurements on the main part of the application.

- Page 2 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Revision history Date Description v.1.0 20230307 • Initial release UM11853 All information provided in this document is subject to legal disclaimers. © 2023 NXP B.V. All rights reserved. User manual Rev. 1.0 — 7 March 2023...

- Page 3 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Important notice NXP provides the enclosed product(s) under the following conditions: This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals.

-

Page 4: Introduction

PF5030 Configurable Power Management IC. The KITPF5030FRDMEVM enables development on PF5030 family of devices. The kit can be connected to the NXP GUI software, which allows you to explore registers, try OTP configurations, and burn the part. -

Page 5: Additional Hardware

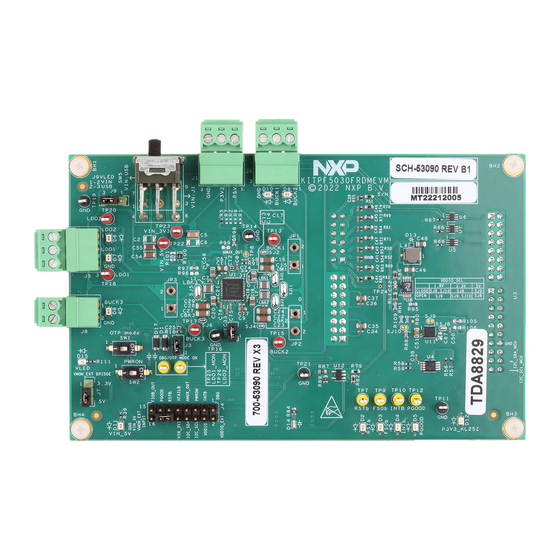

- latest version 4 Getting to know the hardware The KITPF5030FRDMEVM provides flexibility to explore all the features of the device and make measurements on the main part of the application. In combination with the FRDM-KL25Z MCU board, the NXP GUI software allows access to the registers in read and write mode. -

Page 6: Kitpf5030Frdmevm Features

• Support OTP fuse capabilities • Voltage monitoring jumper setting 4.3 Schematic, board layout, and bill of materials The schematic, board layout, and bill of materials for the KITPF5030FRDMEVM board are available at www.nxp.com/KITPF5030FRDMEVM. 4.3.1 VMON board configuration The VMON configuration is highly dependent on the use case. This kit is delivered with a default configuration. -

Page 7: I2C

I C bus on J4 connector, but R58 and R59 must be removed. In addition to this change, make sure that the VDDIO voltage domain and ground are the same on MCU side and KITPF5030FRDMEVM side. 4.3.3 VDDIO The VDDIO pin is powered through VDDIO net and is used to supply internal buffers and I C communication. -

Page 8: Kit Featured Components

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board For VDDIO_SEL 1.8 V: Close SJ8, SJ10 and Open SJ9 For VDDIO_SEL 3.3 V: Close SJ8 and Open SJ9, SJ10 For VDDIO_SEL 5 V: Close SJ9 and Open SJ8 10 nF VDDIO 115 kΩ... -

Page 9: Connectors

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 1. Evaluation board featured components location Number Description VIN_5V and VIN_3V3 power supply input VIN three position switch • Left position: VIN from USB • Middle position: board not supplied • Right position: VIN from J1... -

Page 10: Vin Connector (J1)

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 6. Evaluation board connectors location 4.4.1.1 VIN connector (J1) Table 2. VIN_5V and VIN_3V3 connector (J1) Schematic label Signal name Description J1-1 VIN_5V 5 V voltage supply input J1-2 VIN_3V3 3.3 V voltage supply input... -

Page 11: Debug Connector (J4)

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 4. BUCK1/2 connector (J6) Schematic label Signal name Description J6-1 BUCK2 BUCK2 regulator output J6-2 BUCK1 BUCK1 regulator output J6-3 Ground Table 5. BUCK3 connector (J8) Schematic label Signal name Description J8-1 BUCK3 BUCK3 regulator output... - Page 12 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 7. FRDM-KL25Z safety output connector (J1) ...continued Schematic label Signal name Description J1-9 to J1-11 n.c. Not connected J1-12 FS0b_MCU Fail-safe (active low-logic level) J1-13 to J1-16 n.c. Not connected Table 8. FRDM-KL25Z I C connector (J2)

-

Page 13: Test Points

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 10. FRDM-KL25Z supply connector (J14) ...continued Schematic label Signal name Description J14-10 P5V_KL25Z 5.0 V generated from USB J14-11 n.c. Not connected J14-12 Ground J14-13 n.c. Not connected J14-14 Ground J14-15 n.c. Not connected J14-16 n.c. -

Page 14: Jumpers

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 12. Evaluation board test points description Test point name Signal name Description RSTB Reset pin (active low) AMUX Analog multiplexer output FS0B Fail-safe pin (active low) TP10 INTB Interruption pin (active low) TP12 PGOOD... - Page 15 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 8. Evaluation board jumpers location (with default position) Table 13. Evaluation board jumpers description Name Function Pin number Description Apply voltage to DBG pin 1−2 Either 4.5 V (DBG mode) or 7.95 V (OTP / test mode). See SW1 position VMON_EXT input selection 10−12...

-

Page 16: Led Signaling

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board 4.4.4 LED signaling Figure 9 shows the LEDs provided as visual output devices for the evaluation board: Figure 9. Evaluation board LED signaling location Table 14. Evaluation board LED signaling description Label Name Color Description RSTB... -

Page 17: Switches

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board 4.4.5 Switches Figure 10 Figure 11 show switches locations for board operation. Figure 10. Switches location top UM11853 All information provided in this document is subject to legal disclaimers. © 2023 NXP B.V. All rights reserved. - Page 18 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 11. Switches location bottom Table 15. SW1 description Position Function Description PF5030 OTP can be emulated and RIGHT OTP mode ON programmed when J3 populated PF5030 OTP cannot be emulated LEFT OTP mode OFF and programmed Table 16. SW2 description...

-

Page 19: Installing And Configuring Software And Tools

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Table 17. SW3 description Switch number Voltage rail Description VIN_5V Each LED is connected through an BUCK1 independent switch. Disconnecting BUCK2 them allows more accurate efficiency measurement. BUCK3 The switches also disconnect the LDO1 FRDM-KL25Z ADC inputs. -

Page 20: Installing Nxp Gui Software Package

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 12. Services configuration 2. Press the RST push button and connect the USB cable to the SDA port on the FRDM-KL25Z board. • A new “bootloader” device appears on the left pane of the file explorer 3. - Page 21 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Then double click on the "NXP_GUI-version-Setup.exe" shown in Figure 15 and follow the instructions. Figure 15. NXP_GUI_version_Setup.exe To install the application on Windows PC, proceed with the pop-up windows shown in Figure 16 Figure Figure 16. NXP GUI setup 1/2 Figure 17. NXP GUI setup 2/2...

-

Page 22: Using Pf5030 Nxp Gui

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 18. NXP GUI setup completion Select Finish to complete the installation. When installation is finished, you can search the application on the Windows search bar as “NXPGUI”. Click to launch. 6 Using PF5030 NXP GUI To follow the steps in this section, ensure that the board is connected using the appropriate hardware configuration. - Page 23 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 19. Kit selection window To avoid the kit selection window on every launch, you can check the box “Use this configuration and do not ask again”. The window shown in Figure 20 opens. Figure 20. NXP GUI framework You are now using the PF5030 GUI interface.

-

Page 24: Power Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board • Micro and Device Status: Indicates if the computer USB is connected to the kit. Displays firmware and GUI version. Displays the current state of the fail-safe state machine. Click Display button to refresh. -

Page 25: System Configuration Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board • Calculator These four tabs are used to define the entire FS86 OTP configuration. When the OTP configuration is defined, TBB/OTP scripts can be generated using the Export menu. Generate a TBB file for emulation and an OTP file for OTP programming. -

Page 26: Switching And Ldo Regulators Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 23. OTP System Configuration tab, part 2 of 2: Power-up sequence diagram 6.3.2 Switching and LDO regulators tab The switching and LDO Regulators tab shown in Figure 24 has several sections: • Block diagram: Summarize the output voltages of each regulator •... -

Page 27: Establishing The Connection Between The Nxp Gui And The Hardware

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 25. OTP Functional Safety tab 6.4 Establishing the connection between the NXP GUI and the hardware The device manager allows the connection of the FS86 development board with the NXP GUI. Before plugging the KL25Z USB port USB to the computer, the MCU is in a “NOT DETECTED” state. -

Page 28: Otp Mode And Device Programming

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board The current mode can be read using the refresh button and loop refresh button highlighted in red. Clicking Refresh reads the state one time. Clicking the loop refresh latches and reads the state periodically until a new click deactivates it. - Page 29 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 26. Device programming To set up the hardware before OTP burning, see Section 7.3 configure put device in OTP mode, then follow the steps: • Start the device in OTP mode. • Enter Test mode.

-

Page 30: User Mode Controls

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board To check if a valid OTP configuration is already burned, switch off the supply and then on again. Start the device by clicking the "Exit OTP Mode" button. The device starts with the OTP configuration. -

Page 31: Management Commands

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 28. Script editor Help window 6.6.1.2 Management commands Some commands are used for formatting the scripts. Figure 29 shows the description of each button. Figure 29. Script editor commands • Run: Runs the script once. -

Page 32: Script Generator

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board • Script Editor Help Window: Describes the commands available in script editor and their formats. 6.6.1.3 Script generator The script editor allows the user to save script sequence files, as shown in Figure 30. However, a script sequence file is already saved as an example in the script generator. - Page 33 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 31. Main mirrors tab Figure 32. Fail-safe mirrors tab UM11853 All information provided in this document is subject to legal disclaimers. © 2023 NXP B.V. All rights reserved. User manual Rev. 1.0 — 7 March 2023...

-

Page 34: Access Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board 6.6.3 Access tab 6.6.3.1 Register map All PF5030 I C registers can be accessed in write and read mode using this tab shown in Figure 33. These registers are divided into three sections: • Functional: Main functional I C registers (diagnostics, configuration, and controls) •... -

Page 35: Init Safety Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 34. Bitmap dialog Writing an INIT_FS register automatically updates the corresponding NOT register. 6.6.3.2 INIT Safety tab This tab allows the initialization phase (INIT_FS state) configuration, that must be done before the first good watchdog refresh until the 2 seconds timeout limit. -

Page 36: Watchdog Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 35. INIT safety tab To ease the configuration, Read and Write All buttons are implemented. 6.6.3.3 Watchdog tab The watchdog tab gathers all the registers and configurations having an impact on the watchdog, except "Watchdog Type". -

Page 37: Diagnostic Safety Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 36. Watchdog tab 6.6.3.4 Diagnostic Safety tab The diagnostic safety tab shown in Figure 37 makes it possible to know the safety status of the device. The safety function events, like voltage monitoring flags, analog and logical BIST status, and safety pins are automatically reported in this tab. -

Page 38: Main Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board 6.6.3.5 Main tab Main configuration is possible from the main tab shown in Figure 38. The clock management box allows the configuration of the clock modulation. A regulator can be assigned to a voltage monitoring using the VMON assignment box, leading to a shutdown if OV occurs on the associated regulator. -

Page 39: Main Interrupts Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 39. Regulators tab 6.6.3.7 Main interrupts tab The main interrupts tab shown in Figure 40 allows the monitoring of the regulators, the wake inputs, and the communication events or status. It allows the reading, writing, and polling of overvoltage/undervoltage, overtemperature, and overcurrent flags. -

Page 40: Fail-Safe Interrupts Tab

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board 6.6.3.8 Fail-safe interrupts tab The fail-safe interrupts tab shown in Figure 41 allows the monitoring of the overvoltage/undervoltage fail-safe monitoring status and the watchdog. It allows the reading, writing, and polling of overvoltage/undervoltage flags. -

Page 41: Using An Evaluation Board

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Figure 42. AMUX measurements 7 Using an evaluation board Before starting the process, consult your development board scheme and user manual to configure your required use case. Learn about OTP before operating with the device. The device has a high level of flexibility due to the parameter configuration available in the OTP. -

Page 42: Device Modes

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Device Mirror OTP Fuse configuration register configuration GUI/ S1 - Config S1 - Config Device interface Primary CONFIG S1bis - Config Images CONFIG aaa-044291 Figure 43. OTP block diagram At device starts-up, the content of the valid (last programmed) sector is loaded into mirror registers. The mirror register content is accessible from the NXP GUI, using specific I C commands. - Page 43 Close (OTP mode ON) 2. Connect the Windows PC USB port to the KITPF5030FRDMEVM board using the provided USB 2.0 cable. 3. If external power supplies are used, set the power supplies to 3.3 V and 5.0 V, and current limit to 1.0 A.

-

Page 44: Working In Otp Emulation Mode

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board At this step, if the product is in OTP mode entry configuration, all regulators are OFF. The user can power up with an OTP configuration or configure the mirror registers before powering up. Power-up sequence starts as soon as one of these four actions occurs: •... -

Page 45: References

• Clicking ACCESS > WatchDog > "Watchdog Management" > "FS0B Release script". Remember to chose appropriated "Watchdog Type" before. • Clicking SCRIPT (editor) > Generator > "FS0B_RELEASE_XX_WATCHDOG", then click "RUN". 8 References KITPF5030FRDMEVM — detailed information on this board, including documentation, downloads, and software and tools www.nxp.com/KITPF5030FRDMEVM PF5030 — detailed information on PF5030 http://www.nxp.com/PF5030... -

Page 46: Legal Information

NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, Evaluation products — This product is provided on an “as is” and “with all punitive, special or consequential damages (including - without limitation - faults”... - Page 47 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board NXP — wordmark and logo are trademarks of NXP B.V. 9.3 Trademarks Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. UM11853 All information provided in this document is subject to legal disclaimers.

- Page 48 UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Tables Tab. 1. Evaluation board featured components Tab. 12. Evaluation board test points description ..14 location .............. 9 Tab. 13. Evaluation board jumpers description ..... 15 Tab. 2. VIN_5V and VIN_3V3 connector (J1) ....10 Tab.

-

Page 49: Table Of Contents

UM11853 NXP Semiconductors KITPF5030FRDMEVM evaluation board Contents Introduction ............4 6.6.3.5 Main tab ............38 Finding resources and information on the 6.6.3.6 Regulators tab ..........38 NXP website ............4 6.6.3.7 Main interrupts tab ...........39 Getting ready ............4 6.6.3.8 Fail-safe interrupts tab ........40 Kit contents ............4...

Need help?

Do you have a question about the KITPF5030FRDMEVM and is the answer not in the manual?

Questions and answers