Summary of Contents for AMD Vega 10

- Page 1 "Vega 10" Databook Technical Reference Manual - AMD Confidential Part Number: 56006_1.00...

- Page 2 Terms and limitations applicable to the purchase or use of AMD’s products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

- Page 3 Revision numbers 2.xx are documents with complete information. Full Release Revision numbers 3.xx are for production. Revision History Rev 1.00 (May 17, 2017) • Preliminary release. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 4 Revision History "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 5: Table Of Contents

....................© 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 6 .................."Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 7 ......................... 7.1.1 "Vega 10" Physical Dimensions .

- Page 8 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 9 Figure 2–1 "Vega 10" Display Top-level Data-flow Diagram ....... .

- Page 10 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 11 Table 3–21 AMD PowerXpress Interface ........

- Page 12 Table A–2 Pins Sorted by Signal Name ..........127 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 13: Chapter 1 Introduction

Please review any errata and advisories as they identify amendments to the specifications in this databook. Contact your local AMD support person for the software support schedules of GPU features. 1.1 Part Identification 1.1.1 Packaging Types and Device IDs The vendor ID is 0×1002. -

Page 14: Branding Format

Introduction 1.1.2 Branding Format Figure 1–1 "Vega 10" Branding Note: The date code where YY is the assembly start year and WW is the assembly start week. For engineering samples, ES is found after the date code. Country of origin XXXXXX (The assembly site; such as USA, SINGAPORE, TAIWAN, and CHINA). -

Page 15: Chapter 2 Functional Overview

Functional Overview This section describes the major subsystems and interfaces of "Vega 10". To go to a topic of interest, use the following list of linked cross-references: • Memory Interface (p. 3) • Acceleration Features (p. 5) • Display System (p. 6) •... -

Page 16: Memory Aperture Size

MEM_AP_SIZE [2:0] straps in Pin-based Straps (p. 37) for more information. "Vega 10" requires dedicated ROM for video BIOS. Therefore, memory aperture size is set by ROM straps. The memory aperture defines the address range that the CPU can access. The... -

Page 17: Acceleration Features

• Custom filter anti-aliasing with up to 12-samples per pixel. • An adaptive anti-aliasing mode. • Lossless color compression (up to 16:1). © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 18: Display System

The display system supports accelerated display modes on up to six independent display controllers. The full features of the display system are outlined in the following sections. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 19: Display Features

Functional Overview 2.3.1 Display Features Figure 2–1 "Vega 10" Display Top-level Data-flow Diagram • Up to six independent display controllers that support up to true 36-bpp (bits per pixel) throughout the display pipe. • Support for each display output type up to the following display timings: •... -

Page 20: Dvi/Hdmi™/Displayport/Embedded Displayport Features

• Supports AMD FreeSync™ technology on HDMI using AMD's vendor specific extension: • Fully HDMI compliant • Requires at least one display that is capable of AMD HDMI FreeSync™ technology • Maximum pixel rates for 24-bpp outputs are: • DVI—165 MP/s (megapixels per second) for single-link DVI •... -

Page 21: Table 2-2 Hdmi Features

* Applies to direct connections where GPU and HDMI connectors are on the same PCB with maximum trace lengths of 127 mm or 5 inches, otherwise re-driver is needed. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 22: Displayport (Dp) And Embedded Displayport (Edp) Features

DisplayPort interface (provided the DisplayPort link bandwidth is not exceeded) • Supports AMD FreeSync™ technology, which dynamically synchronizes the refresh rate of a display with the frame rate of the GPU: • Based on DisplayPort Adaptive-Sync technology •... -

Page 23: Table 2-3 Maximum Pixel Rates For 4, 2, Or 1 Lane(S) At 8.1-Ghz Link Rate

• Supports protected content on eDP via ASSR and HDCP • Panel Self Refresh (PSR) support as per eDP 1.4 specification for optimal power reduction when in static screen condition • AMD FreeSync™ is used as a power-savings feature in eDP applications © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. -

Page 24: Integrated Hd-Audio Controller (Azalia) And Codec

Function level reset • Compatible Microsoft® UAA driver support for basic audio • For advanced functionality (as follows), an AMD or a third party driver is required • LPCM: • Speaker formats: 2.0, 2.1, 3.0, 4.0, 5.1, 6.1, and 7.1 •... -

Page 25: Video Acceleration Features

∘ Implementation is based on the ISO/IEC 10918-1 specification ∘ Supports Baseline (DCT based, interleaved only) ∘ Supports up to 8K × 8K resolution (TBD) ∘ JFIF input format © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 26: Video Codec Engine (Vce) Features

• Maximum resolution supported is 4096 × 2176 • H.264 Scalable Video Coding (SVC) temporal video encoding. • Constant bit rate and variable bit rate rate controls. • Supports SR-IOV virtualization "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 27: Pci Express® Bus Support Features

• DPM includes intelligent firmware control to operate the different domains at the ideal operating point based on activity running in the system. • "Vega 10" supports DPM on most clock domains including engine, memory, data fabric, multimedia, etc. • Improved DPM response for performance and/or performance per watt optimization based on the type of workload. -

Page 28: Spread-Spectrum Support

Temperature information can be provided through software (ACPI control methods) or directly through the SMBus hardware interface. 2.10 Thermal Diode The thermal diode in "Vega 10" is a grounded collector PNP BJT. The thermal diode has two pins for its interface—DPLUS and DMINUS (see Table 3–17 (p. -

Page 29: Logo Compliance

2.12 Test Capability Features "Vega 10" has a variety of test modes and capabilities that provide a high-fault coverage and low-DPM (defect per million) ratio. It provides the following features which are implemented in the SOC: •... -

Page 30: Export Control Classification

Functional Overview 2.14 Export Control Classification For information on the export control classification of this product, please contact dl.exportcontrol@amd.com. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 31: Chapter 3 Signal Descriptions

Signal Descriptions This section describes the signals of "Vega 10". The following conventions are used: • All active low signals are shown with the suffix “B”, such as CASA0B. • “PD” denotes a permanent internal pull down. “PD-register” denotes an internal pull down which is register controlled, and by default is turned off. -

Page 32: Pin Assignments

Signal Descriptions • SMBus Interface (p. 34) • PLL Interface (p. 35) • AMD PowerXpress Interface (p. 36) • Power and Ground Descriptions and Operating Conditions (p. 36) • Configuration Straps (p. 37) 3.1 Pin Assignments Table 3–1 Pin Assignments (Left Half) -

Page 33: Pci Express® Bus Interface

3.2 PCI Express® Bus Interface For more information on signal definitions and electrical requirements, refer to the PCI Express® Card Electromechanical 3.0 Specification and PCI Express Base 3.0 Specification. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 34: Memory Interface (Hbm)

Note: • "Vega 10" supports ×16 lane reversal, where the receivers on lanes 0 to 15 of the graphics endpoint are mapped to the transmitter on lanes 15 down to 0 of the root complex. If ×16 lane reversal is employed, both the receive and transmit lanes must be reversed. -

Page 35: Display Configuration Overview

Signal Descriptions 3.4 Display Configuration Overview "Vega 10" has six display links, A to F. Table 3–5 Display Configuration Overview for Links A, B, C, D, E, and F Pin Name Possible Display Configurations Single-link TX[5:3]P/M_DPA[0:2]P/N DisplayPort/ TXCAP/M_DPA3P/N TMDS Single-link... -

Page 36: Displayport

Analog calibration. DP_ZVSS Connect to GND through a 200-Ω (1%) resistor. Note: For native dual-link DVI support, contact AMD. 3.6 DisplayPort Note: If this interface is not used, all signal outputs can be unconnected. AUX_ZVSS, DP_ZVDD_08, and DP_ZVSS should always be connected. -

Page 37: Table 3-7 Displayport Interface

Connect to VSS through a 150-Ω (1%) resistor. Analog calibration. DP_ZVDD_08 Connect to VDD_080 through a 200-Ω (1%) resistor. Analog calibration. DP_ZVSS Connect to GND through a 200-Ω (1%) resistor. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 38: Hardware I2 C Interface

GPIO_7_ROMSCK PD-reset (VDDAN_33) General purpose I/O or open-drain output. BIOS-ROM chip select. GPIO_10_ROMCSB PU-reset Used to enable the ROM for ROM read and program (VDDAN_33) operations. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 39: General Purpose I/O Interface

Also serves as pin strap. Table 3–24 (p. 38) for pin strap definition. GPIO_11 PD-reset General purpose I/O and pin strap. 3.3V Table 3–24 (p. 38) for pin strap definition. (VDDAN_33) © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 40 For GPIOs that serve as pin straps, any external circuits using them must not conflict with the logic level required by the strap after power up until PCIe reset gets de-asserted. Configuration Straps (p. 37) for more information on pin strap configurations. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 41: Amd Svi2 Master Interface

(VOTFC). Note: On "Vega 10", the boot voltage of the SVI2 regulator is 0.9 V controlled by the GPU; overwriting of boot-VID on the PCB is not allowed. If the second domain of the SVI2 regulator is used to power a GPU rail (e.g., VDDCR_HBM/VDDIO_MEM) that cannot work with 0.9 V,... -

Page 42: Global Swap Lock On Multiple Gpus

3.3 V an external 10-kΩ pull-up resistor. GPU genlock is needed, either via a genlock system or by feeding all GPUs with the same reference clock. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 43: Display Identification Interface

Outputs are open drain and 3.3-V tolerant; NOT 5-V tolerant. Level shifter from 5 V to 3.3 V is required on the PCB. HPD1 Hot-plug detect signal from the display device to the GPU. GENERICC_HPD2 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 44: Test/Jtag Interface

GENERICF_HPD5 GENERICG_HPD6 3.14 Test/JTAG Interface In order to debug issues, AMD requires access to the JTAG and debug ports unless specified otherwise. Test points can be used on the JTAG signals to minimize the PCB space needed. Note: The JTAG interface on "Vega 10" is 1.8 V. -

Page 45: Debug Port

TEMPIN: A provision to connect to the anode of an external thermal diode TEMPIN (or base and collector of NPN transistor) for the GPU to read the temperature from a spot of interest on the board or platform. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 46: Smbus Interface

GPIO_19. For more details, see Table 3–24 (p. 38). AMD reserves SMBUS slave address 0×4C for testing purpose. Platform must not communicate with GPU, or any device on the same SMBUS as GPU, using slave address 0×4C. The GPU also supports ARP. -

Page 47: Pll Interface

Variation of Vcross over all rising +140 mV CROS clock edges Voltage Swing -0.3 0.76 1 Single-Ended including swing overshoot/undershoot Rise/Fall time V/ns Measured from 150-mV to fall rise 150-mV differential © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 48: Amd Powerxpress Interface

3.19 AMD PowerXpress™ Interface Table 3–21 AMD PowerXpress™ Interface Type Description Name On/off regulator control signal for AMD ZeroCore Power feature (BACO mode). High (3.3 V) switches the regulators off (enter BACO mode). PX_EN Low (0 V) switches the regulators on. (Default) -

Page 49: Configuration Straps

3.21 Configuration Straps 3.21.1 Pin-based Straps "Vega 10" uses pin straps (i.e., one pin for one strap). Some of the straps are on 3.3-V GPIOs while others are on dedicated 1.8-V strap pins. Each strap pin has either an internal pull-down resistor which provides a default value of 0, or an internal pull-up resistor which provides a default value of 1, at power up. -

Page 50: Table 3-24 Pin-Based Straps

(Internal Refer to application pull- note order #55739 down) on the special usage. Provide a pull-up resistor option to VDDAN_33 on the PCB for each pin. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. - Page 51 PCB for each pin. down) VDDAN_33 on the Provides an option to PCB for each pin. specify certain board- level specifics to the VBIOS or driver. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

-

Page 52: Rom Configurations

(high), the ROM is read at the addresses listed below and default settings are applied. The ROM based straps are ORed with the pin-based straps. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 53: Table 3-25 Rom-Based Straps

0 - Audio function not present. 1 - Audio function present. Boards with a ROM will require both the ROM and the specific pin straps to be © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 54 (via the SUBCLASS field in the PCI configuration space): 0 – VGA Controller capacity enabled. 1 – The device will not be recognized as the system’s VGA controller. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 55: Chapter 4 Timing Specifications

Timing Specifications This chapter describes bus and memory timing specifications of "Vega 10". To link to a topic of interest, use the following list of linked cross-references: • SMBus Timing (p. 43) • Initialization Sequence and Timing (p. 47) • Serial Flash Read/Write Timing (p. 50) •... - Page 56 The SMBus master sends SMB_WR_DATA[7:0] to the slave. p. The SMBus slave acknowledges the master. q. The SMBus master sends a STOP bit to the slave. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 57: Smbus Read Cycle

2. Issuing a Read Data Command to the slave. a. The SMBus master issues a START bit to the slave. b. The SMBus master issues a 7-bit slave address to the slave. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 58: Smbus Read Thermal Sensor

82 01 04 0f 01 66 5A SMB Issue a Read Data Command (cmd3) (Tell SMBus slave to read out thermal value.) 82 03 83 <value read back> Repeat step 2. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 59: Initialization Sequence And Timing

After link training and the reset sequence are complete, the system is ready for the first transaction, such as a configuration space request. The following figure and table provide an outline of the "Vega 10" reset sequence. © 2017 Advanced Micro Devices, Inc. -

Page 60: Standard Boot-Up Sequence

PERSTB (fundamental reset) is asserted to the device. Select internal-strap values are determined by the configuration of pin straps on a subset of GPIOs on the board. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. - Page 61 Configuration 1. The controller is located on an add-in card, and there is access to a local video BIOS serial flash memory. The ROM state machine of "Vega 10" will read in all the "ROM-based straps" right after PERSTB reset is deasserted. There are a total of 33 DWORDs of "ROM-based straps"...

-

Page 62: Serial Flash Read/Write Timing

ROMSI data setup. ROMSI data hold. ROMSO data valid. Tcsh Last clock sent to the ROMCSb rising edge. SCLK = 100 MHz, XTALIN = 27 MHz, ROM_CNTL.SCK_PRESCALE_CRYSTAL_CLK=0x1 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 63: Lcd Panel Power-Up/Down Timing (Edp Interface)

Software controlled Hardware controlled, Power rail fall time from 90% to 10% up to 10 ms Minimum panel off duration (off time is ≥ T12) Software controlled © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 64: Lcd Panel Backlight Control With Pwm

Timing Specifications 4.5 LCD Panel Backlight Control with PWM Figure 4–6 Backlight PWM Parameters "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 65: Table 4-4 Registers For Setting Backlight Pwm Parameters

PWM frequency fine control. Specifies the period of the backlight PWM signal. This 16-bit DISPOUT.BL_PWM_PERIOD_CNTL.BL_PWM_PERIOD value represents the number of divided down input reference clock ( REF / © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 66 When fractional active duty cycle mode is enabled, the (16 - BL_PWM_PERIOD_CNT) LSBs of this register field represent the fractional component of the active duty cycle. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 67: Table 4-5 Backlight Pwm Parameters

• For 55-Hz FTARGET, EINIT will be less than 0.0006%. • The number of usable steps for the active duty cycle is (BL_PWM_PERIOD + 1), that is from 0% up to 100% active duty cycle. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 68 Timing Specifications "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 69: Chapter 5 Electrical Characteristics

Electrical Characteristics This chapter describes the electrical characteristics of "Vega 10". All voltages are with respect to VSS unless specified otherwise. To link to a topic of interest, use the following list of linked cross-references: • Maximum Voltage (p. 57) •... -

Page 70: Electrical Design Power

SVI2 bus from dedicated GPU pins. On "Vega 10"", the boot voltage of the SVI2 regulator is fixed at 0.9 V by default for both domains controlled by the GPU. Overwriting of the SVI2 boot-VID on the PCB is not allowed. -

Page 71: Transient Behavior

The two rails can be merged on the PCB and supplied by the second domain of the SVI2 regulator. Contact AMD for guidance on how to set the second domain of the SVI2 regulator to meet HBM power up requirements. -

Page 72: Figure 5-1 Load Insertion Legend

Current Step Load (A) di/dt (A/us) Max Undershoot (mV) Max Settling Time (us) 1037 Note: If using AMD provided SDLE for the transient study: Step load is applied in addition to a 300 A steady state load. Figure 5–2 Load Release Legend Table 5–4 Load Release Behavior... -

Page 73: Power-Up/Down Sequence

Electrical Characteristics 5.3 Power-up/down Sequence "Vega 10" has the following requirements with regards to power-supply sequencing to avoid damaging the GPU: • All the GPU supplies, except for VDDAN_33, must fully reach their respective nominal voltages within 20 ms of the start of the ramp-up sequence, though a shorter ramp-up duration is preferred. -

Page 74: Displayport Aux Electrical Specification

Pad differential-output swing. diff AUX_Tx Supported transmit-data rate. — Freq AUX_Rx Supported received frequency. — Freq AUX_Pad PADP/N output duty cycle. Note: Assuming perfect duty cycle on input. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 75: Displayport Main Link Electrical Characteristics

Y pin of the macro. Minimum DC voltage at the PAD pin that will produce a stable high — at the Y pin of the macro. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 76 Measured with an edge rate of 1 µs at the PAD pin. Assuming perfect duty cycle on input. Measured at the maximum operating frequency. Typical simulation corner only. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 77: Chapter 6 Thermal Data

76℃ (liquid cooled) This temperature is measured using an on-die temperature sensor near the integrated thermal diode (see Thermal Diode Characteristics (p. 66)). 0℃ Minimum ambient operating temperature. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 78: Thermal Design Power

Total consumption by GPU and HBM memory. 6.4 Thermal Diode Characteristics For "Vega 10", the ideality factor of the on-die thermal diode varies significantly with temperature and sourcing current. If a design chooses to use the GPU's on-die "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. -

Page 79: Storage Requirements

GPU temperature, the external thermal sensor chip must support and enable beta compensation. 6.5 Storage Requirements Ambient temperature: -40℃ to 70℃ Relative humidity: 0% to 90% © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 80 Thermal Data "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 81: Chapter 7 Mechanical Data

Mechanical Data This chapter contains information on the mechanical data for "Vega 10". To go to a topic of interest, use the following list of linked cross-references: • Physical Dimensions (p. 69) • Pressure Specification (p. 73) • Board Solder Reflow Process Recommendations (p. 73) 7.1 Physical Dimensions... -

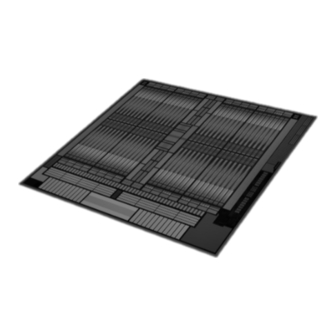

Page 82: Figure 7-1 "Vega 10" Package Outline (Preliminary-Mod-00370 Rev 01)

Mechanical Data Figure 7–1 "Vega 10" Package Outline (Preliminary—MOD—00370 REV 01) "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 83: Figure 7-2 "Vega 10" Package Outline (Preliminary-Mod-00370 Rev 01) Top View

Mechanical Data Figure 7–2 "Vega 10" Package Outline (Preliminary—MOD—00370 REV 01) Top View © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 84: Figure 7-3 "Vega 10" Ball Names (Bottom View)

Mechanical Data Figure 7–3 "Vega 10" Ball Names (Bottom View) "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 85: Pressure Specification

The recommendation is for the stencil aperture of BGA balls to be kept as the same size as the PWB BGA pad design. © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... -

Page 86: Fcbga Reference Reflow Profile For Rohs/Lead-Free Solder

Eutectic solder packages without any reliability validation. • Maximum three reflows are allowed on the same part. "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 87: Table 7-1 Recommended Profiling - Rohs/Lead-Free Solder

Ramp Rate Ramp down < 1℃ / second Peak Maximum 245℃ 235℃ ± 5℃ Temperature at Peak Within 5℃ 240℃ to 245℃ 10 to 30 seconds © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 88 Mechanical Data "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 89: Chapter 8 Boundary Scan Specification

Boundary Scan Specification This chapter contains information on boundary scan specifications as they apply to "Vega 10". To go to a topic of interest, use the following list of linked cross-references: • Introduction (p. 77) • Boundary Scan (p. 77) •... -

Page 90: Jtag Timing Characteristics

Figure 8–1 Timing of the Boundary Scan Signals with Respect to TCK Figure 8–2 Timing of the TAP Ports (TDI, TMS, and TDO) with Respect to TCK "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate. -

Page 91: Appendix A Pin Listings

Appendix A Pin Listings This appendix contains pin listings for "Vega 10" sorted in two ways. To go to the listing of interest, use the following list of linked cross-references: • Pins Sorted by Ball Reference (p. 79) • Pins Sorted by Signal Name (p. 127) A.1 Pins Sorted by Ball Reference... - Page 92 VDDCR_SOC VDDCR_SOC RSVD DFTIO_29 DFTIO_44 DFTIO_31 DFTIO_48 DFTIO_58 DFTIO_68 VDDCR_SOC RSVD DFTIO_86 DFTIO_91 VDDCR_SOC DFTIO_97 DFTIO_107 DFTIO_109 VDDCR_SOC DFTIO_112 DFTIO_120 DFTIO_121 VDDCR_SOC DFTIO_135 DFTIO_136 DFTIO_143 VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 93 DFTIO_211 DFTIO_203 DFTIO_201 DFTIO_202 DFTIO_209 DFTIO_187 VDDCR_SOC DFTIO_17 DFTIO_9 DFTIO_21 DFTIO_22 DFTIO_32 DFTIO_49 DFTIO_52 DFTIO_75 DFTIO_87 RSVD DFTIO_74 DFTIO_82 DFTIO_85 DFTIO_96 DFTIO_102 DFTIO_104 DFTIO_115 DFTIO_119 DFTIO_129 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 94 DFTIO_175 DFTIO_169 DFTIO_222 DFTIO_217 DFTIO_204 DFTIO_182 DFTIO_189 VDDCR_SOC DFTIO_18 DFTIO_27 DFTIO_13 DFTIO_33 DFTIO_39 DFTIO_36 DFTIO_47 DFTIO_70 RSVD DFTIO_65 DFTIO_77 VDDCR_SOC DFTIO_92 DFTIO_101 DFTIO_105 VDDCR_SOC DFTIO_108 DFTIO_110 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 95 VDDCR_SOC DFTIO_162 DFTIO_179 DFTIO_190 VDDCR_SOC DFTIO_149 DFTIO_181 DFTIO_164 DFTIO_172 DFTIO_192 DFTIO_180 DFTIO_186 VDDCR_SOC DFTIO_5 DFTIO_2 DFTIO_12 DFTIO_16 DFTIO_34 DFTIO_64 DFTIO_56 DFTIO_55 DFTIO_62 DFTIO_79 DFTIO_84 DFTIO_94 DFTIO_111 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 96 DFTIO_157 DFTIO_148 DFTIO_163 DFTIO_173 DFTIO_208 DFTIO_214 DFTIO_221 DFTIO_219 DFTIO_216 DFTIO_228 DFTIO_194 DFTIO_199 DFTIO_188 TXCFP_DPF3P TXCFM_DPF3N DDC1DATA DDC1CLK DFTIO_25 DFTIO_53 DFTIO_38 DFTIO_46 DFTIO_50 DFTIO_61 VDDCR_SOC DFTIO_89 DFTIO_95 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 97 DFTIO_168 DFTIO_183 DFTIO_196 VDDCR_SOC DFTIO_185 DFTIO_220 DFTIO_206 VDDCR_SOC DFTIO_254 DFTIO_243 DFTIO_235 DFTIO_200 DFTIO_229 DFTIO_195 DFTIO_215 VDDCR_SOC TX0P_DPF2P TX0M_DPF2N AUX1P AUX1N HPD1 DFTIO_28 DFTIO_42 DFTIO_57 DFTIO_45 DFTIO_63 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 98 DFTIO_81 DFTIO_114 DFTIO_93 DFTIO_123 DFTIO_144 DFTIO_130 DFTIO_171 DFTIO_156 DFTIO_212 DFTIO_252 DFTIO_234 DFTIO_227 DFTIO_257 DFTIO_245 DFTIO_244 DFTIO_223 DFTIO_224 DFTIO_205 VDDCR_SOC TX1P_DPF1P TX1M_DPF1N VDDAN_33 VDDAN_33 DFTIO_20 DFTIO_43 DFTIO_30 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 99 DFTIO_113 VDDCR_SOC DFTIO_178 DFTIO_191 DFTIO_198 VDDCR_SOC DFTIO_290 DFTIO_281 DFTIO_238 VDDCR_SOC DFTIO_218 DFTIO_207 DFTIO_269 VDDCR_SOC DFTIO_272 DFTIO_249 DFTIO_226 VDDCR_SOC DFTIO_225 VDDCR_SOC TX2P_DPF0P TX2M_DPF0N DDC2DATA DDC2CLK DFTIO_0 DFTIO_26 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 100 VDDCR_SOC DFTIO_125 DFTIO_150 DFTIO_160 VDDCR_SOC DFTIO_124 DFTIO_140 DFTIO_184 VDDCR_SOC DFTIO_197 DFTIO_213 DFTIO_232 VDDCR_SOC DFTIO_247 DFTIO_193 DFTIO_255 DFTIO_264 DFTIO_256 DFTIO_259 DFTIO_242 DFTIO_230 DFTIO_231 VDDCR_SOC AUX2P AUX2N GENERICC_HPD2 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 101 DFTIO_23 DFTIO_14 DFTIO_19 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC DFTIO_265 DFTIO_286 VDDCR_SOC DFTIO_246 DFTIO_239 DFTIO_241 VDDCR_SOC DFTIO_233 VDDCR_SOC TXCEP_DPE3P TXCEM_DPE3N © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 102 DFTIO_7 DFTIO_3 DFTIO_24 DFTIO_1 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC DFTIO_280 DFTIO_289 DFTIO_276 VDDCR_SOC DFTIO_248 DFTIO_240 DFTIO_237 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 103 TX3P_DPE2P TX3M_DPE2N VDDAN_18 VDDAN_18 DFTIO_11 DFTIO_6 DFTIO_4 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC DFTIO_275 DFTIO_310 VDDCR_SOC DFTIO_282 DFTIO_261 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 104 Ball Reference Signal Name DFTIO_253 VDDCR_SOC DFTIO_236 VDDCR_SOC TX4P_DPE1P TX4M_DPE1N VDDAN_18 VDDAN_18 RSVD DFTIO_8 DFTIO_10 RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC DFTIO_320 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 105 Ball Reference Signal Name DFTIO_300 DFTIO_287 DFTIO_260 DFTIO_250 DFTIO_251 VDDCR_SOC TX5P_DPE0P TX5M_DPE0N AUX_ZVSS GENERICD_HPD3 RSVD DFTIO_15 RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 106 DFTIO_324 DFTIO_301 DFTIO_288 DFTIO_267 DFTIO_258 VDDCR_SOC TXCDP_DPD3P TXCDM_DPD3N DDCAUX3P DDCAUX3N GENLK_CLK GENLK_VSYNC RSVD RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 107 VDDCR_SOC VDDCR_SOC DFTIO_315 DFTIO_270 DFTIO_309 VDDCR_SOC DFTIO_284 DFTIO_262 DFTIO_263 VDDCR_SOC TX0P_DPD2P TX0M_DPD2N SWAPLOCKA SWAPLOCKB GPIO_0 GPIO_SVD0 RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 108 VDDCR_SOC TEST6 DFTIO_322 VDDCR_SOC DFTIO_303 DFTIO_277 DFTIO_268 VDDCR_SOC DFTIO_285 VDDCR_SOC TX1P_DPD1P TX1M_DPD1N RSVD RSVD GPIO_1 GPIO_SVT0 RSVD RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 109 Pin Listings Ball Reference Signal Name DFTIO_278 DFTIO_279 DFTIO_308 DFTIO_271 DFTIO_298 DFTIO_296 VDDCR_SOC TX2P_DPD0P TX2M_DPD0N GENERICE_HPD4 GPIO_9_ROMSO GPIO_2 GPIO_SVC0 INTCRACKMONGLL VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 110 Pin Listings Ball Reference Signal Name VDDCR_SOC VDDCR_SOC INTCRACKMONGUL DFTIO_283 DFTIO_299 DFTIO_273 DFTIO_274 DFTIO_266 VDDCR_SOC TXCCP_DPC3P TXCCM_DPC3N DDCAUX4P DDCAUX4N GPIO_7_ROMSCK GPIO_8_ROMSI RSVD RSVD VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 111 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC DFTIO_291 DFTIO_292 DFTIO_293 VDDCR_SOC DFTIO_304 DFTIO_306 DFTIO_297 VDDCR_SOC TX3P_DPC2P TX3M_DPC2N VDD_18 VDD_18 GPIO_10_ROMCSB RSVD INTCRACKMONGLR VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 112 VDDCR_SOC VDDCR_SOC INTCRACKMONGUR DFTIO_294 VDDCR_SOC DFTIO_316 DFTIO_323 DFTIO_305 VDDCR_SOC DFTIO_302 VDDCR_SOC TX4P_DPC1P TX4M_DPC1N RSVD VDD_18 RSVD TRST_L AA10 RSVD AA11 RSVD AA12 AA13 VDDCR_SOC AA14 VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 113 AA34 AA35 AA36 AA37 AA38 DFTIO_329 AA39 DFTIO_318 AA40 DFTIO_321 AA41 AA42 DFTIO_312 AA43 DFTIO_313 AA44 DFTIO_307 AA45 VDDCR_SOC TX5P_DPC0P TX5M_DPC0N VDD_18 VDD_18 AB10 RSVD AB11 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 114 AB31 AB32 AB33 AB34 AB35 AB36 AB37 DFTIO_332 AB38 DFTIO_335 AB39 AB40 DFTIO_317 AB41 DFTIO_314 AB42 DFTIO_325 AB43 AB44 DFTIO_311 AB45 VDDCR_SOC TXCBP_DPB3P TXCBM_DPB3N GENERICF_HPD5 VDD_18 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 115 VDDCR_SOC AC35 VDDCR_SOC AC36 VDDCR_SOC AC37 VDDCR_SOC AC38 DFTIO_334 AC39 DFTIO_326 AC40 DFTIO_319 AC41 VDDCR_SOC AC42 DFTIO_333 AC43 DFTIO_330 AC44 DFTIO_328 AC45 VDDCR_SOC TX0P_DPB2P TX0M_DPB2N DDCAUX5P © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 116 AD34 VDDCR_SOC AD35 VDDCR_SOC AD36 VDDCR_SOC AD37 RSVD AD38 RSVD AD39 VDDCR_SOC AD40 RSVD AD41 DFTIO_327 AD42 DFTIO_331 AD43 VDDCR_SOC AD44 RSVD AD45 VDDCR_SOC TX1P_DPB1P TX1M_DPB1N "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 117 AE25 AE26 AE27 AE28 AE29 AE30 AE31 AE32 AE33 AE34 AE35 AE36 AE37 AE38 RSVD AE39 RSVD AE40 RSVD AE41 AE42 RSVD AE43 RSVD AE44 RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 118 AF20 AF21 AF22 AF23 AF24 AF25 AF26 AF27 AF28 AF29 AF30 AF31 AF32 AF33 AF34 AF35 AF36 AF37 RSVD AF38 RSVD AF39 AF40 RSVD AF41 RSVD "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 119 AG26 VDDCR_SOC AG27 VDDCR_SOC AG28 VDDCR_SOC AG29 VDDCR_SOC AG30 VDDCR_SOC AG31 VDDCR_SOC AG32 VDDCR_SOC AG33 VDDCR_SOC AG34 VDDCR_SOC AG35 VDDCR_SOC AG36 VDDCR_SOC AG37 VDDCR_SOC AG38 RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 120 AH23 VDDCR_SOC AH24 VDDCR_SOC AH25 VDDCR_SOC AH26 VDDCR_SOC AH27 VDDCR_SOC AH28 VDDCR_SOC AH29 VDDCR_SOC AH30 VDDCR_SOC AH31 VDDCR_SOC AH32 VDDCR_SOC AH33 VDDCR_SOC AH34 VDDCR_SOC AH35 VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 121 HBMA_DAP_32 AJ18 HBMA_DAP_28 AJ19 AJ20 HBMA_DAP_12 AJ21 HBMA_DAP_7 AJ22 AJ23 HBMA_DAP_17 AJ24 HBMA_DAP_8 AJ25 AJ26 HBMA_DAP_6 AJ27 HBMA_DAP_0 AJ28 AJ29 HBMB_DAP_47 AJ30 HBMB_DAP_41 AJ31 AJ32 HBMB_DAP_30 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 122 AK15 HBMA_DAP_46 AK16 FB_VDDCI_MEM AK17 HBMA_DAP_38 AK18 AK19 HBMA_DAP_23 AK20 HBMA_DAP_21 AK21 AK22 HBMA_DAP_14 AK23 HBMA_DAP_19 AK24 AK25 HBMA_DAP_9 AK26 HBMA_DAP_1 AK27 AK28 HBMB_DAP_59 AK29 HBMB_DAP_55 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 123 AL13 AL14 HBMA_DAP_58 AL15 RSVD AL16 AL17 VDDCI_MEM AL18 HBMA_DAP_26 AL19 HBMA_DAP_41 AL20 VDDCI_MEM AL21 HBMA_DAP_13 AL22 HBMA_DAP_11 AL23 VDDCI_MEM AL24 HBMA_DAP_20 AL25 HBMA_DAP_16 AL26 VDDCI_MEM © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 124 GPIO_13 VDD_080 DBREQ_L AM10 AM11 AM12 AM13 AM14 RSVD AM15 MTESTA AM16 AM17 HBMA_DAP_39 AM18 HBMA_DAP_40 AM19 VDDCI_MEM AM20 HBMA_DAP_27 AM21 HBMA_DAP_22 AM22 VDDCI_MEM AM23 HBMA_DAP_35 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 125 VDDCR_SOC RSVD RSVD RSVD RSVD RSVD RSVD RSVD AN10 AN11 RSVD AN12 RSVD AN13 AN14 RSVD AN15 HBMA_DAP_52 AN16 AN17 HBMA_DAP_51 AN18 AN19 HBMA_DAP_50 AN20 HBMA_DAP_34 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 126 AN43 VDDCR_SOC AN44 VDDCR_SOC AN45 VDDCR_SOC OSC_GAIN0 OSC_GAIN1 OSC_GAIN2 RSVD RSVD RSVD VDD_080 RSVD AP10 RSVD AP11 AP12 AP13 AP14 HBMA_DAP_53 AP15 HBMA_DAP_56 AP16 VDDIO_MEM AP17 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 127 AP40 DFTIO_374 AP41 DFTIO_375 AP42 VDDCR_SOC AP43 VDDCR_SOC AP44 VDDCR_SOC AP45 VDDCR_SOC BP_0 BP_1 GPIO_15 GPIO_16 GPIO_17 RSVD AR10 RSVD AR11 RSVD AR12 AR13 AR14 HBMA_DAP_57 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 128 AR38 RSVD AR39 DFTIO_364 AR40 DFTIO_365 AR41 VDDCR_SOC AR42 VDDCR_SOC AR43 VDDCR_SOC AR44 VDDCR_SOC AR45 DFTIO_341 BP_3 BP_2 GPIO_18 GPIO_19 GPIO_20 VDD_080 RSVD AT10 RSVD AT11 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 129 RSVD AT37 TEMPINRETURN AT38 AT39 VDDCR_SOC AT40 VDDCR_SOC AT41 VDDCR_SOC AT42 VDDCR_SOC AT43 DFTIO_355 AT44 DFTIO_340 AT45 DFTIO_338 RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 130 AU34 HBMB_DAP_12 AU35 AU36 INTCRACKMONDB AU37 TEMPIN AU38 VDDCR_SOC AU39 VDDCR_SOC AU40 VDDCR_SOC AU41 VDDCR_SOC AU42 DFTIO_357 AU43 DFTIO_358 AU44 DFTIO_376 AU45 RSVD RSVD RSVD VDD_080 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 131 HBMB_DAP_34 AV33 HBMB_DAP_19 AV34 AV35 HBMB_DAP_15 AV36 RSVD AV37 AV38 RSVD AV39 RSVD AV40 DFTIO_344 AV41 DFTIO_366 AV42 DFTIO_367 AV43 AV44 DFTIO_356 AV45 RSVD RSVD RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 132 HBMB_DAP_35 AW32 HBMB_DAP_29 AW33 VDDIO_MEM AW34 HBMB_DAP_20 AW35 HBMB_DAP_4 AW36 VDDIO_MEM AW37 VDDCR_HBM AW38 RSVD AW39 RSVD AW40 DFTIO_352 AW41 AW42 DFTIO_347 AW43 DFTIO_345 AW44 DFTIO_349 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 133 FB_VSS_B AY29 FB_VDDIO_MEM_GPU AY30 RSVD AY31 RSVD AY32 VDDIO_MEM AY33 RSVD AY34 RSVD AY35 VDDIO_MEM AY36 RSVD AY37 RSVD AY38 VDDIO_MEM AY39 AY40 DFTIO_359 AY41 DFTIO_351 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 134 BA25 RSVD BA26 RSVD BA27 BA28 FB_VDDIO_MEM_HBM BA29 FB_VDDCR_HBM BA30 RSVD BA31 BA32 RSVD BA33 VDDCR_HBM BA34 BA35 RSVD BA36 RSVD BA37 BA38 RSVD BA39 RSVD "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 135 BB23 BB24 RSVD BB25 RSVD BB26 RSVD BB27 RSVD BB28 BB29 BB30 BB31 RSVD BB32 RSVD BB33 VDDIO_MEM BB34 DPLUS BB35 VDDIO_MEM BB36 VDDIO_MEM BB37 RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 136 BC20 PCIE_RX15P BC21 PCIE_RX15N BC22 BC23 RSVD BC24 RSVD BC25 BC26 RSVD BC27 RSVD BC28 RSVD BC29 PROCHOT_L BC30 BC31 RSVD BC32 BC33 RSVD BC34 DMINUS "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 137 PCIE_RX11P BD17 PCIE_RX11N BD18 BD19 PCIE_RX14P BD20 PCIE_RX14N BD21 BD22 RSVD BD23 BD24 RSVD BD25 BD26 BD27 RSVD BD28 RSVD BD29 FANOUT BD30 DDCVGACLK BD31 ALERT_L © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 138 BE14 BE15 PCIE_RX10P BE16 PCIE_RX10N BE17 BE18 PCIE_RX13P BE19 PCIE_RX13N BE20 BE21 BE22 REFCLKP BE23 REFCLKN BE24 RSVD BE25 BE26 BE27 BE28 BE29 FANIN BE30 DDCVGADATA "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

-

Page 139: Pins Sorted By Signal Name

ALERT_L BD31 ANALOGIO AUX1N AUX1P AUX2N AUX2P AUX_ZVSS BL_ENABLE AU14 BL_PWM_DIM AV16 BP_0 BP_1 BP_2 BP_3 CLKREQB BE31 DBREQ_L DDC1CLK DDC1DATA DDC2CLK DDC2DATA DDCAUX3N DDCAUX3P DDCAUX4N © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00... - Page 140 DFTIO_9 DFTIO_10 DFTIO_11 DFTIO_12 DFTIO_13 DFTIO_14 DFTIO_15 DFTIO_16 DFTIO_17 DFTIO_18 DFTIO_19 DFTIO_20 DFTIO_21 DFTIO_22 DFTIO_23 DFTIO_24 DFTIO_25 DFTIO_26 DFTIO_27 DFTIO_28 DFTIO_29 DFTIO_30 DFTIO_31 DFTIO_32 DFTIO_33 DFTIO_34 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 141 DFTIO_51 DFTIO_52 DFTIO_53 DFTIO_54 DFTIO_55 DFTIO_56 DFTIO_57 DFTIO_58 DFTIO_59 DFTIO_60 DFTIO_61 DFTIO_62 DFTIO_63 DFTIO_64 DFTIO_65 DFTIO_66 DFTIO_67 DFTIO_68 DFTIO_69 DFTIO_70 DFTIO_71 DFTIO_72 DFTIO_73 DFTIO_74 DFTIO_75 DFTIO_76 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 142 DFTIO_93 DFTIO_94 DFTIO_95 DFTIO_96 DFTIO_97 DFTIO_98 DFTIO_99 DFTIO_100 DFTIO_101 DFTIO_102 DFTIO_103 DFTIO_104 DFTIO_105 DFTIO_106 DFTIO_107 DFTIO_108 DFTIO_109 DFTIO_110 DFTIO_111 DFTIO_112 DFTIO_113 DFTIO_114 DFTIO_115 DFTIO_116 DFTIO_117 DFTIO_118 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 143 DFTIO_135 DFTIO_136 DFTIO_137 DFTIO_138 DFTIO_139 DFTIO_140 DFTIO_141 DFTIO_142 DFTIO_143 DFTIO_144 DFTIO_145 DFTIO_146 DFTIO_147 DFTIO_148 DFTIO_149 DFTIO_150 DFTIO_151 DFTIO_152 DFTIO_153 DFTIO_154 DFTIO_155 DFTIO_156 DFTIO_157 DFTIO_158 DFTIO_159 DFTIO_160 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 144 DFTIO_177 DFTIO_178 DFTIO_179 DFTIO_180 DFTIO_181 DFTIO_182 DFTIO_183 DFTIO_184 DFTIO_185 DFTIO_186 DFTIO_187 DFTIO_188 DFTIO_189 DFTIO_190 DFTIO_191 DFTIO_192 DFTIO_193 DFTIO_194 DFTIO_195 DFTIO_196 DFTIO_197 DFTIO_198 DFTIO_199 DFTIO_200 DFTIO_201 DFTIO_202 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 145 DFTIO_219 DFTIO_220 DFTIO_221 DFTIO_222 DFTIO_223 DFTIO_224 DFTIO_225 DFTIO_226 DFTIO_227 DFTIO_228 DFTIO_229 DFTIO_230 DFTIO_231 DFTIO_232 DFTIO_233 DFTIO_234 DFTIO_235 DFTIO_236 DFTIO_237 DFTIO_238 DFTIO_239 DFTIO_240 DFTIO_241 DFTIO_242 DFTIO_243 DFTIO_244 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 146 DFTIO_261 DFTIO_262 DFTIO_263 DFTIO_264 DFTIO_265 DFTIO_266 DFTIO_267 DFTIO_268 DFTIO_269 DFTIO_270 DFTIO_271 DFTIO_272 DFTIO_273 DFTIO_274 DFTIO_275 DFTIO_276 DFTIO_277 DFTIO_278 DFTIO_279 DFTIO_280 DFTIO_281 DFTIO_282 DFTIO_283 DFTIO_284 DFTIO_285 DFTIO_286 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 147 DFTIO_313 AA43 DFTIO_314 AB41 DFTIO_315 DFTIO_316 DFTIO_317 AB40 DFTIO_318 AA39 DFTIO_319 AC40 DFTIO_320 DFTIO_321 AA40 DFTIO_322 DFTIO_323 DFTIO_324 DFTIO_325 AB42 DFTIO_326 AC39 DFTIO_327 AD41 DFTIO_328 AC44 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 148 DFTIO_358 AU43 DFTIO_359 AY40 DFTIO_360 AK42 DFTIO_361 BA42 DFTIO_362 AK44 DFTIO_363 AN39 DFTIO_364 AR39 DFTIO_365 AR40 DFTIO_366 AV41 DFTIO_367 AV42 DFTIO_368 AN40 DFTIO_369 AL42 DFTIO_370 AH37 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 149 FB_VDDCR_SOC AH17 FB_VDDIO_MEM_GPU AY29 FB_VDDIO_MEM_HBM BA28 FB_VSS_A AJ16 FB_VSS_B AY28 GENERICA GENERICB AV14 GENERICC_HPD2 GENERICD_HPD3 GENERICE_HPD4 GENERICF_HPD5 GENERICG_HPD6 GENLK_CLK GENLK_VSYNC GPIO_0 GPIO_1 GPIO_2 GPIO_3 GPIO_4 GPIO_5 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 150 HBMA_DAP_11 AL22 HBMA_DAP_12 AJ20 HBMA_DAP_13 AL21 HBMA_DAP_14 AK22 HBMA_DAP_15 AN22 HBMA_DAP_16 AL25 HBMA_DAP_17 AJ23 HBMA_DAP_18 AN25 HBMA_DAP_19 AK23 HBMA_DAP_20 AL24 HBMA_DAP_21 AK20 HBMA_DAP_22 AM21 HBMA_DAP_23 AK19 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 151 HBMA_DAP_53 AP14 HBMA_DAP_54 AR18 HBMA_DAP_55 AT14 HBMA_DAP_56 AP15 HBMA_DAP_57 AR14 HBMA_DAP_58 AL14 HBMA_DAP_59 AK14 HBMB_DAP_0 AL37 HBMB_DAP_1 AJ36 HBMB_DAP_2 AP36 HBMB_DAP_3 AM36 HBMB_DAP_4 AW35 HBMB_DAP_5 AP37 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 152 HBMB_DAP_35 AW31 HBMB_DAP_36 AU31 HBMB_DAP_37 AP31 HBMB_DAP_38 AN31 HBMB_DAP_39 AL31 HBMB_DAP_40 AV30 HBMB_DAP_41 AJ30 HBMB_DAP_42 AR30 HBMB_DAP_43 AT31 HBMB_DAP_44 AK31 HBMB_DAP_45 AM30 HBMB_DAP_46 AU30 HBMB_DAP_47 AJ29 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 153 MTESTA AM15 MTESTB AN37 OSC_GAIN0 OSC_GAIN1 OSC_GAIN2 PCIE_REFCLKN PCIE_REFCLKP PCIE_RX0N PCIE_RX0P PCIE_RX1N PCIE_RX1P PCIE_RX2N PCIE_RX2P PCIE_RX3N PCIE_RX3P PCIE_RX4N BE10 PCIE_RX4P PCIE_RX5N BD11 PCIE_RX5P BD10 PCIE_RX6N BC12 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 154 PCIE_TX5N AY12 PCIE_TX5P AY11 PCIE_TX6N BB13 PCIE_TX6P BB12 PCIE_TX7N BA14 PCIE_TX7P BA13 PCIE_TX8N AY15 PCIE_TX8P AY14 PCIE_TX9N BB16 PCIE_TX9P BB15 PCIE_TX10N BA17 PCIE_TX10P BA16 PCIE_TX11N AY18 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 155 BC29 PUMPIN BE33 PUMPOUT BD33 PX_EN AU16 REFCLKN BE23 REFCLKP BE22 RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 156 AF42 RSVD AF44 RSVD AG38 RSVD AG39 RSVD AG40 RSVD AG42 RSVD AG43 RSVD AG44 RSVD AH38 RSVD AH40 RSVD AH41 RSVD AH42 RSVD AH44 RSVD "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 157 RSVD AN12 RSVD AN14 RSVD AN38 RSVD RSVD RSVD RSVD RSVD AP10 RSVD AP38 RSVD RSVD AR10 RSVD AR11 RSVD AR37 RSVD AR38 RSVD RSVD AT10 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 158 AV38 RSVD AV39 RSVD AV45 RSVD RSVD RSVD RSVD AW10 RSVD AW12 RSVD AW13 RSVD AW15 RSVD AW16 RSVD AW23 RSVD AW24 RSVD AW26 RSVD AW27 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 159 BB38 RSVD BB40 RSVD BB41 RSVD BB43 RSVD RSVD BC23 RSVD BC24 RSVD BC26 RSVD BC27 RSVD BC28 RSVD BC31 RSVD BC33 RSVD BC36 RSVD BC37 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 160 BE38 RSVD BE40 AN10 AM10 SMBCLK SMBDAT SWAPLOCKA SWAPLOCKB TEMPIN AU37 TEMPINRETURN AT37 TEST6 TESTEN TEST_PG AJ11 TEST_PG_BACO AV15 TRST_L TS_A AL10 TX0M_DPB2N TX0M_DPD2N TX0M_DPF2N TX0P_DPB2P "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 161 TX3M_DPE2N TX3P_DPA2P TX3P_DPC2P TX3P_DPE2P TX4M_DPA1N TX4M_DPC1N TX4M_DPE1N TX4P_DPA1P TX4P_DPC1P TX4P_DPE1P TX5M_DPA0N TX5M_DPC0N TX5M_DPE0N TX5P_DPA0P TX5P_DPC0P TX5P_DPE0P TXCAM_DPA3N TXCAP_DPA3P TXCBM_DPB3N TXCBP_DPB3P TXCCM_DPC3N TXCCP_DPC3P TXCDM_DPD3N TXCDP_DPD3P TXCEM_DPE3N TXCEP_DPE3P © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 162 VDDCR_HBM AP18 VDDCR_HBM AP19 VDDCR_HBM AP21 VDDCR_HBM AP22 VDDCR_HBM AP24 VDDCR_HBM AP25 VDDCR_HBM AP27 VDDCR_HBM AP28 VDDCR_HBM AP33 VDDCR_HBM AR34 VDDCR_HBM AT16 VDDCR_HBM AU18 VDDCR_HBM AU21 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 163 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 164 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 165 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 166 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 167 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 168 VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC VDDCR_SOC "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 169 VDDCR_SOC AC28 VDDCR_SOC AC29 VDDCR_SOC AC30 VDDCR_SOC AC31 VDDCR_SOC AC32 VDDCR_SOC AC33 VDDCR_SOC AC34 VDDCR_SOC AC35 VDDCR_SOC AC36 VDDCR_SOC AC37 VDDCR_SOC AC41 VDDCR_SOC AC45 VDDCR_SOC AD13 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 170 VDDCR_SOC AF45 VDDCR_SOC AG17 VDDCR_SOC AG18 VDDCR_SOC AG19 VDDCR_SOC AG20 VDDCR_SOC AG21 VDDCR_SOC AG22 VDDCR_SOC AG23 VDDCR_SOC AG24 VDDCR_SOC AG25 VDDCR_SOC AG26 VDDCR_SOC AG27 VDDCR_SOC AG28 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 171 VDDCR_SOC AH36 VDDCR_SOC AH39 VDDCR_SOC AH43 VDDCR_SOC AH45 VDDCR_SOC AJ45 VDDCR_SOC AK45 VDDCR_SOC AL41 VDDCR_SOC AL45 VDDCR_SOC AM39 VDDCR_SOC AM43 VDDCR_SOC AM44 VDDCR_SOC AM45 VDDCR_SOC AN43 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 172 VDDIO_MEM AT27 VDDIO_MEM AT30 VDDIO_MEM AT33 VDDIO_MEM AU19 VDDIO_MEM AU24 VDDIO_MEM AV24 VDDIO_MEM AV26 VDDIO_MEM AV27 VDDIO_MEM AW30 VDDIO_MEM AW33 VDDIO_MEM AW36 VDDIO_MEM AY24 VDDIO_MEM AY32 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 173 VDD_18 VDD_18 VDD_18 VDD_18 VDD_18 VDD_18 VDD_080 VDD_080 VDD_080 VDD_080 VDD_080 VDD_080 VDD_080 AV10 VDD_080 VDD_080 VDD_080 VDD_080_EFUSE VDD_080_EFUSE BD26 BE26 BE27 VREFEXTA AR15 VREFEXTB AR36 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 174 Pin Listings Signal Name Ball Reference "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 175 Pin Listings Signal Name Ball Reference © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 176 Pin Listings Signal Name Ball Reference "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 177 Pin Listings Signal Name Ball Reference © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 178 Pin Listings Signal Name Ball Reference "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 179 Pin Listings Signal Name Ball Reference AA12 AA15 AA16 AA19 AA20 AA23 AA24 AA25 AA26 AA27 AA28 AA29 AA30 AA31 AA32 AA33 AA34 AA35 AA36 AA37 AA41 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 180 AB24 AB25 AB26 AB27 AB28 AB29 AB30 AB31 AB32 AB33 AB34 AB35 AB36 AB39 AB43 AC12 AC15 AC16 AC19 AC20 AD11 AD12 AD15 AD16 AD19 AD20 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 181 AE28 AE29 AE30 AE31 AE32 AE33 AE34 AE35 AE36 AE37 AE41 AF11 AF12 AF13 AF14 AF15 AF16 AF19 AF20 AF21 AF22 AF23 AF24 AF25 AF26 AF27 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 182 AF34 AF35 AF36 AF39 AF43 AG12 AG13 AG14 AG15 AG16 AH11 AH12 AH13 AH14 AH15 AH16 AJ12 AJ13 AJ19 AJ22 AJ25 AJ28 AJ31 AJ34 AJ37 AJ41 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 183 AK27 AK30 AK33 AK36 AK37 AK39 AK43 AL12 AL13 AL16 AM11 AM12 AM13 AM16 AN13 AN16 AN18 AN21 AN24 AN27 AN30 AN33 AN36 AN41 AP11 AP12 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 184 AP35 AR12 AR13 AR16 AT11 AT13 AT15 AT38 AU10 AU12 AU13 AU17 AU20 AU23 AU26 AU29 AU32 AU35 AU45 AV11 AV25 AV28 AV31 AV34 AV37 AV43 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 185 AW21 AW22 AW41 AW45 AY10 AY13 AY16 AY19 AY22 AY39 AY43 BA12 BA15 BA18 BA21 BA22 BA27 BA31 BA34 BA37 BA41 BB11 BB14 BB17 BB20 BB23 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 186 BC13 BC16 BC19 BC22 BC25 BC30 BC32 BC35 BC38 BC41 BC44 BC45 BD12 BD15 BD18 BD21 BD23 BD25 BD34 BD37 BD40 BD43 BD44 BD45 BE11 BE14 "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

- Page 187 Pin Listings Signal Name Ball Reference BE17 BE20 BE21 BE25 BE28 BE34 BE37 BE39 BE42 BE43 BE44 WAKEB XTALIN XTALOUT XTRIG6 XTRIG7 © 2017 Advanced Micro Devices, Inc. "Vega 10" Databook AMD Confidential - Do not duplicate. 56006_1.00...

- Page 188 Pin Listings "Vega 10" Databook © 2017 Advanced Micro Devices, Inc. 56006_1.00 AMD Confidential - Do not duplicate.

Need help?

Do you have a question about the Vega 10 and is the answer not in the manual?

Questions and answers