Summary of Contents for AMD AMD RS690M

- Page 1 AMD RS690M Databook Technical Reference Manual Rev. 3.06 P/N: 41978_rs690m_ds © 2008 Advanced Micro Devices, Inc...

- Page 2 AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur.

-

Page 3: Table Of Contents

2.1 Host Interface ..................................2-2 2.2 Side-port Memory Interface (RS690T Only)........................2-3 2.2.1 DDR2 Memory Interface............................2-3 2.3 LVDS Interface ...................................2-6 2.3.1 LVDS Data Mapping............................2-6 2.3.2 LVDS Spread Spectrum ............................2-8 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary Table of Contents-1... - Page 4 ..........................4-2 4.5 LVDS Timing..................................4-2 4.6 OSCIN Timing ................................... 4-2 4.7 Power Rail Power Up Sequence............................4-4 4.8 LCD Panel Power Up/Down Timing ..........................4-5 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Table of Contents-2 Proprietary...

- Page 5 A.4 RS690T Pin List Sorted by Pin Name..........................1-14 Appendix B: AMD RS690E B.1 Introduction ..................................2-1 B.2 Feature Differences between the RS690T and RS690E....................2-1 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary Table of Contents-3...

- Page 6 B.3 DVI-I Support..................................2-3 HDMI....................................2-4 HDCP....................................2-4 B.6 RS690E Display Options..............................2-4 B.7 The LVTM Interface in TMDS Mode ..........................2-5 Appendix C: Revision History 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Table of Contents-4 Proprietary...

- Page 7 Figure B-4: Pins for Analog Output on the DVI-I Connector ......................2-3 Figure B-5: RS690E Display Options ..............................2-5 Figure B-6: DC Characteristics of the LVTM Interface in TMDS Mode ..................2-7 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. List of Figures-1 Proprietary...

- Page 8 This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. List of Figures-2 Proprietary...

- Page 9 Table 6-1: ACPI States Supported by the RS690M ........................6-1 Table 6-2: ACPI Signal Definitions ..............................6-1 Table 6-3: Standard PCI Configuration Space Header Type 0 ....................... 6-2 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. List of Tables-1 Proprietary...

- Page 10 Table 7-5: Truth Table for the VOH/VOL Tree Outputs ....................... 7-6 Table 7-6: RS690M VOH/VOL Tree ............................. 7-7 Table 7-7: RS690T VOH/VOL Tree .............................. 7-8 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. List of Tables-2 Proprietary...

-

Page 11: Chapter 1: Overview

9.0 compliant 2D/3D graphics core and a system controller in a single chip. It supports the AMD Athlon™ 64, Athlon 64 FX, Athlon 64 X2, AMD Sempron™, and AMD Turion™ 64 processors, including both AM2 and S1 socket CPUs. All CPUs are supported on both high performance and value platforms. -

Page 12: Rs690Mc

RS690MC Software Compatibility The graphics driver for the RS690M is fully compatible with all other ATI Radeon class graphics controllers from AMD. A single driver can support multiple graphics configurations across AMD's product lines, including the ATI Radeon family and the AMD chipset family. In addition, this driver compatibility allows the RS690M to benefit immediately from ®... -

Page 13: Pci Express® Interface

• One x4 link. 1.5.5 A-Link Express II Interface • One x4 A-Link Express II interface (PCI Express 1.1 compliant) for connection to an AMD Southbridge, providing more bandwidth than the older A-Link Express interface. 1.5.6 2D Acceleration Features •... -

Page 14: Acceleration Features

Supports top quality DVD with low CPU usage. • Hardware-based adaptive de-interlacing filter and scaler provide high quality full-screen and full-speed video playback. Minimizes the aliasing artifacts along edges usually caused by a conventional deinterlacer/scaler. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 15: Multiple Display Features

2456x1536 @60Hz (pixel clock at 320MHz) for 16:10 format TV Out • An integrated TV encoder from AMD’s Xilleon products, with an on-chip DAC (shared with the CRT analog output) (Note: Simultaneous output for TV and CRT is not supported). •... -

Page 16: 1.5.10 Integrated Lvds

• Supports industry standard EIA-861B video modes including 480p, 720p, and 1080i. For a full list of currently supported modes, contact your AMD CSS representative. Maximum resolutions supported by various modes are: • Single-link DVI: 1600x1200 @60Hz with pixel clock at 162 MHz and standard timings; 1920x1200 @60Hz with pixel clock at 154MHz and reduced blanking timings. -

Page 17: 1.5.13 Pc Design Guide Compliance

• End user diagnostics • Drivers meet Microsoft's rigorous WHQL criteria and are suitable for systems with the "Designed for Windows" logos. • Comprehensive OS and API support. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 18: Branding Diagrams

Branding Diagrams • Hot-key support (Windows ACPI 1.0b or AMD Event Handler Utility where appropriate). • Extensive power management support. • Rotation mode support in software. • Dual CRTC, simultaneous view, extended desktop support (Windows XP and Windows Vista) •... -

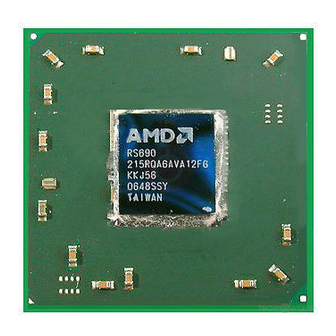

Page 19: Branding Diagrams For Asic Revision A12 And After

Note: The branding diagrams below do not necessarily contain the latest ASCI revision numbers for the IGPs. Unless specified otherwise, no information in this databook is specific to the ASIC revision numbers given in the diagrams. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 20: Figure 1-2 Rs690M Branding Diagram For Asic Revision A12 And After

WW - Assembly Start Week XX - Assembly Location V - Substrate Vendor Code “o” indicates pin A1. Figure 1-3 RS690MC Branding Diagram for ASIC Revision A12 and After 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 1-10 Proprietary... -

Page 21: Part Number Legend

Package BOM Substrate ASIC Revision Revision 215 – Desktop K – High Temp 216 – Mobile G – Lead Free Figure 1-5 The RS690-Family ASIC Part Number Legend © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 1-11... -

Page 22: Conventions And Notations

(i.e., “CPU_D[7:0]”). A similar short-hand notation is used to indicate bit occupation in a register. For example, NB_COMMAND[15:10] refers to the bit positions 10 through 15 of the NB_COMMAND register. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 1-12... -

Page 23: Register Field

Hot Plug Detect iDCT inverse Discrete Cosine Transform IDDQ Direct Drain Quiescent Current Integrated Graphics Processor. A single device that integrates a graphics processor and a system controller. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 1-13... - Page 24 Chrominance (also CrCb). Corresponds to the color of a pixel. UXGA Ultra Extended Graphics Array Vertical Blank Interval VESA Video Electronics Standards Association Video Graphics Adapter Voltage Regulation Module 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 1-14 Proprietary...

-

Page 25: Chapter 2: Functional Descriptions

Register Interface Setup iDCT Engine Engine Engine TMDS, enabling DVI/HDMI (Multiplexed on PCI-E Gfx lanes) External Displays Overlay (RS690T Only) TV-Out LVDS Figure 2-1 RS690M Internal Block Diagram © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 26: Host Interface

Host Interface Host Interface The RS690M is optimized to interface with the Athlon 64/Athlon 64 FX/Athlon X2/AMD Sempron/AMD Turion 64 processors, including both AM2 and S1 socket CPUs. This section presents an overview of the HyperTransport™ interface. For a detailed description of the interface, please refer to the HyperTransport I/O Link Specification from the HyperTransport Consortium. -

Page 27: Side-Port Memory Interface (Rs690T Only)

Because the memory controller supplies only one chip select signal, only DDR2 devices with one chip select are supported. A wide range of DDR2 timing parameters, configurations, and loadings are programmable via the RS690T memory controller configuration registers © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 28: Table 2-1 Supported Ddr2 Components

DDR2 memories. Table 2-2 DDR2 Memory Row and Column Addressing Address A13 A12 A11 A10 A9 16Mbits x16 devices Column 32Mbits x8 devices Column 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... - Page 29 Side-port Memory Interface (RS690T Only) Address A13 A12 A11 A10 A9 32Mbits x16 devices Column 64Mbits x8 devices Column 64Mbits x16 devices Column Note: PC = precharge flag © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

-

Page 30: Lvds Interface

UP2C3 UP2C2 UP2C1 TXOUT_U2-/+ UP3C7 UP3C6 UP3C5 UP3C4 UP3C3 UP3C2 UP3C1 TXOUT_U3-/+ UP4C7 UP4C6 UP4C5 UP4C4 UP4C3 UP4C2 UP4C1 Figure 2-5 Single/Dual Channel 24-bit LVDS Data Transmission Ordering 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 31: Table 2-3 Lvds 24-Bit Tft Single Pixel Per Clock (Single Channel) Signal Mapping

LP1C5 LP1C6 LP1C7 LP2C1 LP2C2 LP2C3 LP2C4 LP2C5 LP2C6 LP2C7 LP3C1 LP3C2 LP3C3 LP3C4 LP3C5 HSYNC LP3C6 VSYNC LP3C7 ENABLE LP4C1 LP4C2 LP4C3 LP4C4 LP4C5 LP4C6 LP4C7 Reserved © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 32: Lvds Spread Spectrum

LVDS signals. The amount of spread (center spread of up to +/-2.5% and down spread of up to 5%) and the modulation frequency (in the range of 20-50kHz) are programmable through the LVDS registers. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. -

Page 33: Dvi/Hdmi (Not Applicable To The Rs690Mc)

The signal mapping for the transmission is shown in Table 2-5, “Single-Link Signal Mapping for DVI/HDMI,” on page 2-10 , and Table 2-6, “Dual-Link Signal Mapping for DVI,” on page 2-11 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... - Page 34 Phase 2 Phase 3 Phase 4 Phase 5 Phase 6 Phase 7 Phase 8 Phase 9 Phase 10 Note: H/VSYNC are transmitted on TX0M/P(Blue) channel during blank. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 2-10 Proprietary...

- Page 35 - H/VSYNC are transmitted on TX0M/P(Blue) channel during blank. - For DVI dual-link mode, the first active data pixel is defined as pixel#0 (an even pixel), as opposed to the DVI specifications. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 2-11...

-

Page 36: Support For Hdmi Packet Types

For bit rate, field repeat, frame type by software. * Note: These packet types are supported using generic packet types. A maximum of two of them can be supported simultaneously. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 2-12... -

Page 37: Vga Dac Characteristics

On the RS690M platform, an external clock chip provides the reference clock to the CPU (for generating the CPU internal clocks) and a reference clock to the RS690M (for generating the HyperTransport, PCI Express, and A-Link Express II clocks). For more information about supported clock chips, please consult your AMD CSS representative. © 2008 Advanced Micro Devices, Inc. - Page 38 External Clock Chip This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 2-14 Proprietary...

-

Page 39: Chapter 3: Pin Descriptions And Strap Options

“Power Management Pins” on page 3-13 “Miscellaneous Pins” on page 3-13 “Power Pins” on page 3-14 “Ground Pins” on page 3-15 “Debug Port Signals” on page 3-16 “Strapping Options” on page 3-18 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 40: Pin Assignment

Clock Interface CRT and TV Interface External graphics Interface LVDS Interface General Purpose External Device Interface Power Management Interface Powers Grounds Others Figure 3-1 RS690M Pin Assignment (Left) 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 41: Figure 3-2 Rs690M Pin Assignment (Right)

Clock Interface CRT and TV Interface External graphics Interface LVDS Interface General Purpose External Device Interface Power Management Interface Powers Grounds Others Figure 3-2 RS690M Pin Assignment (Right) © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 42: Rs690T Pin Assignment

Side-port Memory CRT and TV Interface External graphics Interface LVDS Interface General Purpose External Device Interface Power Management Interface Powers Grounds Others Figure 3-3 RS690T Pin Assignment (Left) 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 43: Figure 3-4 Rs690T Pin Assignment (Right)

Side-port Memory CRT and TV Interface External graphics Interface LVDS Interface General Purpose External Device Interface Power Management Interface Powers Grounds Others Figure 3-4 RS690T Pin Assignment (Right) © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 44: Interface Block Diagram

VDDA_12_PKG LVDDR18D PLLVDD18 Power AVSSN PLLVDD12 AVSSQ VDD_18 AVSSDI VDDA_12 VDD_CORE HTPVSS Grounds LPVSS VDD_HT LVSSR VDDR PLLVSS VDDR3 VDD_PLL VSSA VSS_PLL Figure 3-5 RS690M Interface Block Diagram 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 45: Figure 3-6 Rs690T Interface Block Diagram

MEM_CKP, MEM_CKN Memory MEM_CS# MEM_DQ[15:0] AVSSN MEM_DM[1:0] MEM_DQS[1:0]P, MEM_DQS[1:0]N AVSSQ AVSSDI MEM_ODT HTPVSS MEM_COMPP, MEM_COMPN Grounds LPVSS MEM_VREF LVSSR PLLVSS VSSA VSS_PLL Figure 3-6 RS690T Interface Block Diagram © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 46: Cpu Hypertransport™ Interface

(refer to the reference schematics for the proper resistor values). Reference voltage. It supplies the threshold value for MEM_VREF Other – None distinguishing between “1” and “0” on a memory signal. Typical value is 0.5*VDD_MEM. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 47: Pci Express® Interfaces

VDD_PCIE VSS_PCIE external resistor of an appropriate value. TX Impedance Calibration. Connect to GND on the motherboard with an external PCE_CALRP Other VDD_PCIE VSS_PCIE resistor of an appropriate value. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 48: Clock Interface

AVSS 50kΩ DACSDA VDDR3 programmable: C Data for display (to video monitor) PU/PD/none 50kΩ DACSCL VDDR3 programmable: C Clock for display (to video monitor) PU/PD/none 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 3-10 Proprietary... -

Page 49: Lvds Interface (24 Bits)

LVDS mode. LVDDR33 LVDS lower clock channel (+). This channel is used as the TXCLK_LP LVSSR None LVDDR18D transmitting channel in single-channel LVDS mode. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 3-11... -

Page 50: Tmds Interface Multiplexed On The Pci Express® Graphics Lanes

TX0P - 1st Link Blue+ GFX_TX2N TX0M- 1st Link Blue - GFX_TX3P TXCP - Clock+ GFX_TX3N TXCM - Clock- GFX_TX4P TX5P- 2nd Link Red+ GFX_TX4N TX5M - 2nd Link Red- 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 3-12 Proprietary... -

Page 51: Power Management Pins

When high, puts the RS690M in test mode and disables the TESTMODE VDDR3 – RS690M from operating normally. THERMALDIODE_P, Diode connections to external SMBus microcontroller for – – – THERMALDIODE_N monitoring IC thermal characteristics. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 3-13... -

Page 52: Power Pins

AD24, AE22, AE23, AE24, AE25 VDD_MEM 1.8V AA9, AB9, AC7, AC8, AD6, Isolated power for side-port memory and debug I/Os (RS690T only) AD7, AD8, AE6, AE7, AE8 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 3-14 Proprietary... -

Page 53: Ground Pins

Dedicated digital ground for the DAC (1.8V) IOPLLVSS Ground for system PLLs (RS690T only) LPVSS LVDS PLL macro ground pin LVSSR A14, A16, C15, C16, C19, LVDS interface ground pin D12, F14, F15 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 3-15... -

Page 54: Debug Port Signals

Adding stubs to side-port memory signals for the purpose is not recommended. Other signals in the table should be brought out to test points on the motherboard. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. - Page 55 Debug [programmable*] DFT_GPIO5 Debug [programmable*] LVDS_BLON Debug [programmable*] LVDS_BLEN Debug [programmable*] LVDS_DIGON Debug [programmable*] TMDS_HPD Debug [programmable*] *Note: The port is programmable into any of Debug0 to Debug15. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 3-17...

-

Page 56: Strapping Options

• Setting through an external debug port, if implemented (contact your AMD CSS representative for details). All of the straps below are defined active low. They are pulled up internally by default, so that no external pull-ups are required to select “1”s for those straps. - Page 57 Configuration E. If the pin straps are used, the GPPSB configuration will then be determined according to this table and cannot be changed after the system has been powered up. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary 3-19...

- Page 58 Strapping Options This page intentionally left blank. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 3-20 Proprietary...

-

Page 59: Chapter 4: Timing Specifications

DQ valid window. This delay ensures adequate setup and hold time to capture the memory data. This DLL delay is programmable through the following registers: MCA_DLL_SLAVE_RD_0. MCA_DLL_ADJ_DQSR_0 <NBMCIND : 0xE0[7:0]> MCA_DLL_SLAVE_RD_1. MCA_DLL_ADJ_DQSR_1 <NBMCIND : 0xE1[7:0]> © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 60: Write Cycle Dq/Dqs Delay

Table 4-4 Timing Requirements for the OSCIN Pad Symbol Parameter Typical Unit Note µs REFCLK Period 0.037 – REFCLK Frequency – REFCLK Rise Time – – REFCLK Fall Time – – 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... - Page 61 1 Time intervals measured at 50% threshold point. 2 FIP is the reciprocal of TIP. 3 FRQD is the tolerance of the frequency input for proper generation of the expected PLL frequencies. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

-

Page 62: Power Rail Power Up Sequence

Figure 4-1 above only shows the power up sequence for the power rails that the RS690M connects to. For a power up sequence for the whole RS690M platform, please refer to the RS690/RS485-Series IGP Motherboard Design Guide . 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. -

Page 63: Lcd Panel Power Up/Down Timing

M = LVTMA_PWRSEQ_REF_DIV.LVTMA_PWRSEQ_REF_DIV (1- 255) N1 = LVTMA_PWRSEQ_DELAY1.LVTMA_PWRUP_DELAY1 (0 - 15) N2 = LVTMA_PWRSEQ_DELAY1.LVTMA_PWRUP_DELAY2 (0 - 15) N3 = LVTMA_PWRSEQ_DELAY1.LVTMA_PWRDN_DELAY1 (0 - 15) N4 = LVTMA_PWRSEQ_DELAY1.LVTMA_PWRDN_DELAY2 (0 - 15) © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... - Page 64 LCD Panel Power Up/Down Timing This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

-

Page 65: Electrical Characteristics

IOPLVDD18 (RS690T Only) 1.71 1.89 1.8V power for memory I/O PLLs Power for HyperTransport HTPVDD 1.71 1.89 interface PLL Note: Numbers in this table are to be qualified. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 66: Dc Characteristics

Table 5-5 DC Characteristics for the OSCIN Pad (14.3181818MHz) Symbol Description Minimum Typical Maximum Comments Input Low Voltage – 0.6V – Input High Voltage 2.5V 2.6V – – VIMAX Maximum Input Voltage – – 3.3V – 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 67: Table 5-6 Dc Characteristics For The Ddr2 Interface

1 AVCC stands for the termination supply voltage of the receiver, which is 3.3V +/- 5%. 2 Figure 5-1 below illustrates some of the DC characteristics of the TMDS interface. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 68: Figure 5-1 Dc Characteristics Of The Tmds Interface

2 Measured under typical conditions, at minimum Differential Clock Frequency and maximum LVDS PLL VOC frequency. 3 Measured under typical conditions, based on typical leakage values. 4 Figure 5-2 below illustrates the DC characteristics of the LVDS interface. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 69: Rs690M Thermal Characteristics

RS690M Thermal Limits Table 5-9 RS690M Thermal Limits Parameter Minimum Nominal Maximum Unit Note ° Operating Case Temperature — Absolute Rated Junction ° — — Temperature ° Storage Temperature — © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 70: Thermal Diode Characteristics

AMD’s reference heat sink solution for the RS690M. Refer to Chapter 7 in the Thermal Design and Analysis Guidelines for the RS690 Product Family for heatsink and thermal design guidelines. -

Page 71: Package Information

0.30 0.40 0.50 0.84 0.87 0.90 φb 0.40 0.50 0.60 20.80 21.00 21.20 7.33 20.80 21.00 21.20 6.93 19.20 19.20 0.80* 0.15 * Note: Only minimum pitch shown. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 72: Pressure Specification

Ensure that any distortion (bow or twist) of the board after SMT and cooling device assembly is within industry guidelines (IPC/EIA J-STD-001). For measurement method, refer to the industry approved technique described in the manual IPC-TM-650, section 2.4.22. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 73: Board Solder Reflow Process Recommendations

ASIC package, for which a maximum size of 400µm is recommended (see Figure below). This recommendation is based on AMD’s sample land pattern design for the RS690M, which is available from your AMD CSS representative. -

Page 74: Figure 5-6 Rohs/Lead-Free Solder (Sac305/405 Tin-Silver-Copper) Reflow Profile

60 – 80 sec typical 60 – 80 sec typical Pre–heating Zone 120 - 240 sec max Heating Time Heating Time Figure 5-6 RoHS/Lead-Free Solder (SAC305/405 Tin-Silver-Copper) Reflow Profile 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 5-10 Proprietary... -

Page 75: Chapter 6: Power Management And Acpi

Output to the Southbridge to allow LDTSTOP# assertion. Northbridge LDTSTOP# HyperTransport Technology Stop: Enables and disables links during Southbridge system state transitions. POWERON# Power on Power switch RESET# Global Reset Southbridge © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 76: Power Management For The Graphics Controller

Specifically, if bit 4 is set, the CAP_PTR register is implemented to give offset to the first item in the Capabilities link list. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 77: Register Block Definition

Read accesses to the reserved or the unimplemented registers must be completed normally and a data value of 0000h should be returned. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 78: Capability Identifier: Cap_Id (Offset = 0)

The definition of these registers (including layout, size, and bit definitions) is specific to each capability. The PCI Power Management Register Block is defined in Figure 6-1, ‘Linked List for Capabilities,” below. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 79: Next Item Pointer

XX1XXb - PME# can be asserted from D2. bit(14) X0XXXb - PME# cannot be asserted from D3hot. bit(15) 0XXXXb - PME# cannot be asserted from D3cold. Read Only RS690M supports D2. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... - Page 80 Read Only Reserved Read Only Reserved 001b Read Only A value of 001b indicates that this function complies with Revision 1.0 of the PCI Power Management Interface Specification. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

-

Page 81: Chapter 7: Testability

I/O Reset OSCIN I/O Test Clock XOR Tree 7.3.1 Brief Description of an XOR Tree Figure 7-1 An example of a generic XOR tree is shown in the below. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 82: Description Of The Xor Tree For The Rs690M

When differential signal pairs are listed as single entries on the XOR tree, opposite input values should be applied to the two signals in each pair (e.g., for entry no. 13 on the tree, when “1” is applied to HT_RXCAD15P, “0” should be applied to HT_RXCAD15N). 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 83: Table 7-3 Rs690M Xor Tree

HT_RXCAD4N/P V25/V24 AE15 HT_RXCAD3N/P AA24/AA25 AC13 HT_RXCAD2N/P AA23/AB23 AE13 HT_RXCAD1N/P AB25/AB24 AD13 HT_RXCAD0N/P AC25/AC24 HT_RXCTLN/P P25/P24 HT_RXCLK1N/P W22/W21 HT_RXCLK0N/P W25/Y24 GPP_RX3N/P AA9/AB9 GPP_RX2N/P AA7/Y7 GPP_RX1N/P AE20/AD20 GPP_RX0N/P AE16/AD16 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 84: Table 7-4 Rs690T Xor Tree

HT_RXCAD0N/P AC25/AC24 MEM_DQ1 AE13 HT_RXCTLN/P P25/P24 MEM_DQ0 AD13 HT_RXCLK1N/P W22/W21 MEM_DM1 AD19 HT_RXCLK0N/P W25/Y24 MEM_DM0 AC16 GPP_RX3N/P R5/R4 MEM_A13 AA11 GPP_RX2N/P P5/P4 MEM_A12 GPP_RX1N/P U5/U4 MEM_A11 GPP_RX0N/P R8/R7 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 85: Voh/Vol Test

The VOH/VOL logic gives signal output on I/Os when test patterns are applied through the TEST_ODD and TEST_EVEN inputs. Sample of a generic VOH/VOL tree is shown in the Figure 7-2 below. © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 86: Voh/Vol Tree Activation

4. Set DACSDA to 0. 5. Load JTAG instruction register with the instruction 0110 0011. 6. Load JTAG instruction register with the instruction 0010 0111. 7. Set POWERGOOD to 1. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... -

Page 87: Voh/Vol Pin List

EVEN GFX_TX11P/N W1/W2 DACSCL GFX_TX10P/N V3/W3 EVEN DACVSYNC EVEN GFX_TX9P/N V2/V1 DACHSYNC GFX_TX8P/N T2/U1 EVEN LVDS_BLON EVEN GFX_TX7P/N R1/R2 LVDS_BLEN GFX_TX6P/N P3/R3 EVEN LVDS_DIGON EVEN GFX_TX5P/N P2/P1 DFT_GPIO5 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 88: Table 7-7 Rs690T Voh/Vol Tree

SB_TX0P/N AC1/AC2 EVEN HT_TXCAD3P/N G25/H24 GPP_TX3P/N V2/V1 HT_TXCAD2P/N F25/F24 EVEN GPP_TX2P/N U2/U1 EVEN HT_TXCAD1P/N E23/F23 GPP_TX1P/N W1/W2 HT_TXCAD0P/N E24/E25 EVEN GPP_TX0P/N V3/W3 EVEN DACSCL GFX_TX7P/N R1/R2 DACVSYNC EVEN 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... - Page 89 AC13 MEM_DQ4 AC15 EVEN MEM_DQ1 AE13 MEM_DQ3 AD14 EVEN MEM_DQ0 AD13 MEM_DM1 AD19 EVEN MEM_DM0 AC16 MEM_A13 AA11 EVEN MEM_A12 MEM_A11 EVEN MEM_A10 AE10 MEM_A9 EVEN MEM_A8 AA12 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

- Page 90 VOH/VOL Test This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. 7-10 Proprietary...

-

Page 91: Appendix A Pin Listings

“RS690M Pin List Sorted by Pin Name” on page A-6 “RS690T Pin List Sorted by Ball Reference” on page A-10 “RS690T Pin List Sorted by Pin Name” on page A-14 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... -

Page 92: Rs690M Pin List Sorted By Ball Reference

SB_TX1P AE25 VDD_HT VSSA VSSA GFX_TX15P GPP_RX2N VSSA GFX_TX15N GPP_RX3N AD10 SB_TX0N GPP_TX2N GFX_TX14P AD11 PCE_CALRP VSSA AB11 SB_RX3N AD12 VDDR SB_TX3N AB12 SB_RX1P AD13 DEBUG0 SB_TX2N AB14 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... - Page 93 TXCLK_UP TXOUT_U1P VDDA_12 AVSSN TXOUT_U1N VDDA_12 GFX_TX0N LVSSR VDD_PLL TVCLKIN HT_TXCAD3N VSSA VSSA AVDD LVDS_BLEN GFX_TX0P HTTSTCLK LVSSR VDD_CORE HT_RXCALN LVSSR HT_TXCALP VDD_18 TESTMODE GREEN VDD_18 GFX_CLKP VDD_CORE © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

- Page 94 HT_TXCAD14P VDD_CORE GFX_RX4N HT_TXCAD14N VDD_CORE VSSA GFX_TX5P VDD_CORE GFX_RX3N HT_RXCAD12P GFX_RX3P HT_TXCAD15P HT_RXCAD12N VDDA_12 HT_TXCAD15N VSSA VDDA_12_PKG HT_TXCTLN HT_RXCTLP HT_RXCAD13N VDD_CORE HT_RXCTLN HT_RXCAD13P GFX_TX6P HT_RXCAD5N VDD_CORE GFX_RX8P HT_RXCAD6N 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

- Page 95 GFX_TX10P GFX_RX14P GFX_TX11P SB_RX2P SB_RX2N SB_RX0P SB_RX0N VDD_HT HT_RXCAD11P GFX_TX11N HT_RXCAD11N HT_RXCLK1P HT_RXCLK1N HT_RXCLK0N GFX_TX10N GFX_RX12P GFX_RX12N VSSA VDDA_12 GFX_RX14N VSSA VSSA VSSA VSSA VSSA VDD_HT HT_RXCAD8N GFX_TX12P © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

-

Page 96: Rs690M Pin List Sorted By Pin Name

HT_RXCAD12P GFX_RX0N GFX_TX15P HT_RXCAD13N GFX_RX0P GFX_TX1N HT_RXCAD13P GFX_RX10N GFX_TX1P HT_RXCAD14N GFX_RX10P GFX_TX2N HT_RXCAD14P GFX_RX11N GFX_TX2P HT_RXCAD15N GFX_RX11P GFX_TX3N HT_RXCAD15P GFX_RX12N GFX_TX3P HT_RXCAD1N AB25 GFX_RX12P GFX_TX4N HT_RXCAD1P AB24 GFX_RX13N 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary... - Page 97 HT_TXCAD15P LVSSR TXOUT_L0P HT_TXCAD1N LVSSR TXOUT_L1N HT_TXCAD1P LVSSR TXOUT_L1P HT_TXCAD2N LVSSR TXOUT_L2N HT_TXCAD2P LVSSR TXOUT_L2P HT_TXCAD3N AA14 TXOUT_L3N HT_TXCAD3P AB14 TXOUT_L3P HT_TXCAD4N OSCIN TXOUT_U0N HT_TXCAD4P PCE_CALRN AE11 TXOUT_U0P © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

- Page 98 AE12 VDD_CORE VDDR3 VDD_CORE VDDR3 VDD_CORE VDD_CORE VDD_HT AA17 AC14 VDD_HT AB17 AC15 VDD_HT AB19 AC16 VDD_HT AC18 AC22 VDD_HT AC19 AC23 VDD_HT AC20 AD25 VDD_HT AD21 AE14 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

- Page 99 VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA AE10 VSSA VSSA VSSA VSSA VSSA © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary...

-

Page 100: Rs690T Pin List Sorted By Ball Reference

AE17 MEM_DQS0P AA23 HT_RXCAD2N VDDA_12 AE18 AA24 HT_RXCAD3N AE19 MEM_DQ11 AA25 HT_RXCAD3P VDDA_12 VDDA_12 VSSA VSSA AE20 MEM_DQ13 VSSA VDD_MEM AE21 MEM_DQ15 VDD_MEM VDD_MEM AE22 VDD_HT SB_TX1P 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. A-10 Proprietary... - Page 101 DFT_GPIO4 DFT_GPIO1 HT_TXCAD10N VDD_CORE VDD_CORE HT_TXCAD10P VDDA_12 GFX_CLKN SYSRESET# VDDR3 POWERGOOD LVDS_DIGON HT_TXCAD3P LVDDR33 LPVSS VSSA LVDDR33 TXCLK_LP GFX_RX0N TMDS_HPD TXOUT_L3N GFX_RX0P LVSSR VSSA LVSSR VDDA_12 VDDA_12 © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary A-11...

- Page 102 GFX_TX1P VSSA VDD_CORE HT_TXCAD4N GFX_RX6P HT_TXCAD5N GFX_RX6N VDD_CORE HT_TXCAD5P VSSA GFX_TX2P GFX_RX5N HT_RXCAD15N GFX_TX3P GFX_RX5P HT_RXCAD15P VDD_CORE VDDA_12 GFX_TX7N GFX_TX4N VDD_CORE VDD_CORE HT_RXCAD14P HT_RXCAD14N VDD_CORE VDD_CORE VDD_CORE 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. A-12 Proprietary...

- Page 103 MEM_A11 HT_RXCAD5N MEM_CAS# HT_RXCAD6N IOPLLVSS HT_RXCAD6P HT_RXCAD8N VSSA SB_TX3P GPP_RX1P GPP_RX1N VSSA HT_RXCLK0P VDDA_12 GPP_TX3N SB_TX3N SB_RX2P MEM_CS# SB_RX2N VSSA MEM_CKN MEM_ODT GPP_TX3P HT_RXCAD5P HT_RXCAD4P HT_RXCAD4N GPP_TX0P © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary A-13...

-

Page 104: Rs690T Pin List Sorted By Pin Name

HT_TXCAD0N GFX_RX3P HT_RXCAD0N AC25 HT_TXCAD0P GFX_RX4N HT_RXCAD0P AC24 HT_TXCAD10N GFX_RX4P HT_RXCAD10N AB22 HT_TXCAD10P GFX_RX5N HT_RXCAD10P AC21 HT_TXCAD11N GFX_RX5P HT_RXCAD11N HT_TXCAD11P GFX_RX6N HT_RXCAD11P HT_TXCAD12N GFX_RX6P HT_RXCAD12N HT_TXCAD12P GFX_RX7N 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. A-14 Proprietary... - Page 105 SB_CLKP I2C_CLK MEM_CKP SB_RX0N I2C_DATA MEM_COMPN SB_RX0P IOPLLVDD12 AB17 MEM_COMPP SB_RX1N IOPLLVDD18 AA17 MEM_CS# SB_RX1P IOPLLVSS MEM_DM0 AC16 SB_RX2N LDTSTOP# MEM_DM1 AD19 SB_RX2P LPVDD MEM_DQ0 AD13 SB_RX3N © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary A-15...

- Page 106 TXOUT_U2P VDD_HT_PKG AC22 TXOUT_U3N VDD_MEM AC23 TXOUT_U3P VDD_MEM AD25 VDD_18 VDD_MEM AE14 VDD_18 VDD_MEM AE18 VDD_CORE VDD_MEM VDD_CORE VDD_MEM VDD_CORE VDD_MEM VDD_CORE VDD_MEM VDD_CORE VDD_MEM VDD_CORE VDD_MEM 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. A-16 Proprietary...

- Page 107 VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA VSSA © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary A-17...

- Page 108 This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. A-18 Proprietary...

-

Page 109: Appendix Bamd Rs690E

AMD RS690E Introduction The RS690T and RS690E are two members of the same AMD RS690-series Northbridge and chipset family. The RS690E and RS690T have exactly the same package, pin-out, and fabrication process. All peripheral functions and features are the same as well, except for the differences explained in Section B.2... -

Page 110: Figure B-2 Rs690T And Rs690E Analog Display Output Signals

BIOS to configure the enhanced LVDS/TMDS (LVTM) interface to drive out either LVDS or TMDS/DVI signals. The video BIOS is available from AMD. The minimum version number for the LVDS output is 10.55.0.15 and for the TMDS/DVI output is 10.55.0.31. Contact your AMD CSS representative for the latest video BIOS. -

Page 111: Dvi-I Support

VGA Signals Figure B-4 Pins for Analog Output on the DVI-I Connector For the single-link DVI output portion of the DVI-I connector, AMD recommends using the RS690E’s LVTM interface to provide the DVI output and routing these digital signals (see Figure B-3, “RS690E LVTM Interface”... -

Page 112: Hdmi

Creating a DVI-I configuration using the DAC signals (RED, GREEN, BLUE, DACHSYNC, etc.) plus the TMDS output multiplexed on the PCI-E graphics links is supposed to work as well, but the configuration is not recommended since it cannot be validated using any of AMD's current internal reference boards. HDMI The RS690E has an integrated controller that allows support for a single-link HDMI (video and audio) transmission on the LVTM interface. -

Page 113: The Lvtm Interface In Tmds Mode

Termination Functional Description Domain Domain Name LVDDR33 TXOUT_L0N TX0M VSSLT None TMDS data channel 0 (-) LVDDR18D LVDDR33 TXOUT_L0P TX0P VSSLT None TMDS data channel 0 (+) LVDDR18D © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... - Page 114 2.4.1, “DVI/HDMI Data Transmission Order and Signal Mapping,” on page 2- 9 for the data ordering and signal mapping for the TMDS/DVI signal output from the LVTM interface on the RS690E. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

-

Page 115: Figure B-6 Dc Characteristics Of The Lvtm Interface In Tmds Mode

4 Figure B-6 below illustrates some of the DC Characteristics of the LVTM interface in TMDS mode. Single-ended Waveforms VHmax VHmin VLmax VLmin Differential Waveform 2VSW Figure B-6 DC Characteristics of the LVTM Interface in TMDS Mode © 2008 Advanced Micro Devices, Inc. 41978 AMD RS690M Databook 3.06 Proprietary... - Page 116 This page is left blank intentionally. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

-

Page 117: Appendix C Revision History

Updated Table 3-17, “Strap Definitions for the RS690M”: Added descriptions for two Reserved straps for the RS690M. • Added Section 4.1, “CPU HyperTransport™ Bus Timing”: Referred designers to AMD specifications. • Updated Section 4.6, “OSCIN Timing”: Removed high and low time requirements. - Page 118 Updated Table 5-4, “DC Characteristics for the HTREFCLK Pad (66.66MHz)”: Revised VIH minimum to 1.4V. Rev 3.00 (Jan 2007) • Changed general document styles and legal statements to reflect AMD identity. • Raised revision number to 3.00, following the AMD scheme.

- Page 119 Updated the solder reflow profile (Section 5.3.3.2, “Reflow Profile”). Rev 3.05 (Oct 2007) • Added information on the RS690E (Appendix B, “AMD RS690E”). Rev 3.06 (Feb 2008) • Clarified on the maximum resolutions supported by different display interfaces (Section 1.5.9, “Multiple Display Features”...

- Page 120 This page intentionally left blank. 41978 AMD RS690M Databook 3.06 © 2008 Advanced Micro Devices, Inc. Proprietary...

Need help?

Do you have a question about the AMD RS690M and is the answer not in the manual?

Questions and answers