Table of Contents

Advertisement

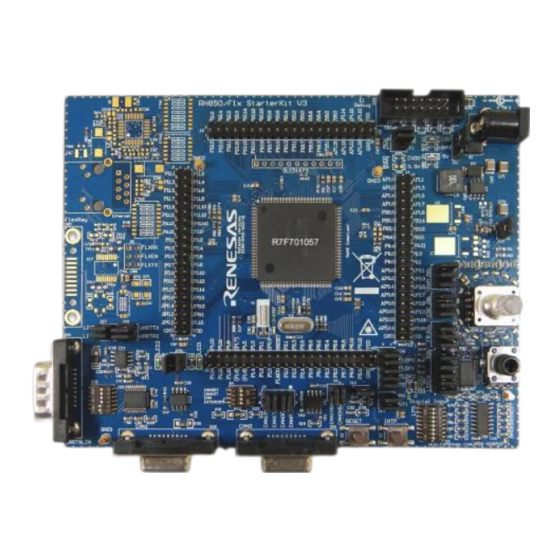

RH850/F1Kx, RH850/F1K Series

Hardware Design Guide

Introduction

This application note is intended to provide RH850/F1Kx, RH850/F1K series specific information and

recommendations on the device usage. It should be used in conjunction with the corresponding RH850/F1Kx,

RH850/F1K series user manual (includes the electrical characteristics).

Target Device

RH850/F1Kx Series

RH850/F1KM Group

•

o

RH850/F1KM-S1

RH850/F1KM-S4

o

•

RH850/F1KH Group

o

RH850/F1KH-D8

RH850/F1K Series

•

RH850/F1K Group

o

Disclaimer:

Renesas Electronics does not warrant the information included in this document. You are fully responsible for

incorporation of these circuits, software, and information in the design of your equipment and system. Renesas

Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these

circuits, software, or information.

R01AN3841ED0110 Rev. 1.10

August 8, 2019

100pin

80pin

64pin

48pin

272pin

233pin

176pin

144pin

100pin

324pin

233pin

176pin

176pin

144pin

100pin

APPLICATION NOTE

R01AN3841ED0110

Rev. 1.10

August 8, 2019

Page 1 of 108

Advertisement

Table of Contents

Subscribe to Our Youtube Channel

Summary of Contents for Renesas RH850/F1Kx Series

- Page 1 Disclaimer: Renesas Electronics does not warrant the information included in this document. You are fully responsible for incorporation of these circuits, software, and information in the design of your equipment and system. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

-

Page 2: Table Of Contents

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table of Contents Power Supply ........................8 Power Supply Overview of RH850/F1KM-S1 ................8 1.1.1 Power Supply Pin Overview of RH850/F1KM-S1 ............... 8 1.1.2 Power Supply Pin Configuration of RH850/F1KM-S1 ............9 1.1.3 Power Supply Pin Architecture of RH850/F1KM-S1 ............9 1.1.4 Power Supply Timing of RH850/F1KM-S1 ................ - Page 3 Recommended Connection of Unused Pins for RH850/F1KH-D8 ........81 4.4.5 Recommended Connection of Unused Pins for RH850/F1K .......... 83 Injected Current ......................... 85 SENT Interface (RH850/F1Kx Series only) ..............86 AD-Converter ........................87 Conversion time ........................87 External Multiplexer Wait Time ....................88 Equivalent Input Circuit ......................

- Page 4 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table of Figures Figure 1: RH850/F1KM-S1 Power supply architecture ..................9 Figure 2: Recommended REGVCC power configuration for RH850/F1KM-S1 ..........12 Figure 3: The voltage range which has to be kept voltage slope for RH850/F1KM-S1 ........12 Figure 4: RH850/F1KM-S1 Power up/down timing ..................

- Page 5 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Figure 39: LPD (4 pins) connection ......................... 95 Figure 40: Nexus, LPD (4 pins) and LPD (1 pin) connection ................96 Figure 41: PG-FPx flash programming interface connection ................98 Figure 42: E1/E2 flash programming interface connection ................99 Figure 43: Combined debug and flash programming interface connections ..........

- Page 6 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table of Tables Table 1: RH850/F1KM-S1 Power supply pin overview ..................8 Table 2: RH850/F1KM-S1 Overview of power supply architecture cases ............10 Table 3: RH850/F1KM-S1 Power supply architecture with single supply 5V ..........10 Table 4: RH850/F1KM-S1 Power supply architecture with mixed supply 5V &...

- Page 7 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 39: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V ........38 Table 40: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V ........39 Table 41: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V ........40 Table 42: RH850/F1KH-D8 Power supply architecture with single supply 3.3V ..........

-

Page 8: Power Supply

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Power Supply The internal circuits are separated into two independent power domains, the Always-On area (AWO area) and the Isolated area (ISO area). The power supply of the Always-On area (AWO area) is always on in all operating modes and stand-by modes. -

Page 9: Power Supply Pin Configuration Of Rh850/F1Km-S1

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.1.2 Power Supply Pin Configuration of RH850/F1KM-S1 The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected. • The EVCC supply pins are internally connected The EVSS pins are internally connected. -

Page 10: Table 2: Rh850/F1Km-S1 Overview Of Power Supply Architecture Cases

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 2: RH850/F1KM-S1 Overview of power supply architecture cases Supply Voltage Case Permission REGVCC EVCC A0VREF Case 1 Operation permitted Case 2 3.3V Operation permitted Case 3 3.3V Operation not permitted Case 4 3.3V Operation not permitted Case 5 3.3V... -

Page 11: Table 5: Rh850/F1Km-S1 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 5: RH850/F1KM-S1 Power supply architecture with mixed supply 5V & 3.3V Case 3 and Case 4 – Mixed Supply 5V & 3.3V Condition REGVCC ≠ EVCC EVCC = 3.3V or 5V A0VREF = don’t care Port Function –... -

Page 12: Power Supply Timing Of Rh850/F1Km-S1

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.1.4 Power Supply Timing of RH850/F1KM-S1 The RH850/F1KM-S1 has a recommended power supply timing. The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. -

Page 13: Figure 4: Rh850/F1Km-S1 Power Up/Down Timing

RH850/F1Kx, RH850/F1K Series Hardware Design Guide a) When RESET terminal is used REGVCC/EVCC VPOC (min) Min. 0 us Max . 0.5/t VS ms A0VREF 3.0V Min. 0 us Min. 0 us RESET DPOR DRPD Figure 4: RH850/F1KM-S1 Power up/down timing b) When RESET terminal is not used REGVCC/EVCC VPOC (min) -

Page 14: Power Supply Overview Of Rh850/F1Km-Xx

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Power Supply Overview of RH850/F1KM-XX Reserved for future use R01AN3841ED0110 Rev. 1.10 Page 14 of 108 August 8, 2019... -

Page 15: Power Supply Overview Of Rh850/F1Km-S4

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Power Supply Overview of RH850/F1KM-S4 1.3.1 Power Supply Pin Overview of RH850/F1KM-S4 The devices of the RH850/F1KM-S4 have the following power supply pins: • Power supply voltage REGVCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain. -

Page 16: Power Supply Pin Configuration Of Rh850/F1Km-S4

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.3.2 Power Supply Pin Configuration of RH850/F1KM-S4 The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected. • The EVCC supply pins are internally connected The BVCC supply pins are internally connected. -

Page 17: Table 9: Rh850/F1Km-S4 Overview Of Power Supply Architecture Cases

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 9: RH850/F1KM-S4 Overview of power supply architecture cases Voltage Case Permission REGVCC EVCC BVCC A0VREF A1VREF Case 1 Operation permitted Case 2 3.3V Operation permitted Case 3 3.3V Operation permitted Case 4 3.3V 3.3V Operation permitted Case 5... -

Page 18: Table 11: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 11: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 2 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 5V A0VREF = 5V A1VREF = 3.3V Port Function –... -

Page 19: Table 13: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 13: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 4 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 5V A0VREF = 3.3V A1VREF = 3.3V Port Function –... -

Page 20: Table 14: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 14: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 5 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 3.3V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 21: Table 15: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 15: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 6 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 3.3V A0VREF = 5V A1VREF = 3.3V Port Function –... -

Page 22: Table 16: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 16: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 7 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 3.3V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 23: Table 17: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 17: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 8 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V BVCC = 3.3V A0VREF = 3.3V A1VREF = 3.3V Port Function –... -

Page 24: Table 20: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 20: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 12 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 25: Table 21: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 21: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 13 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 5V A1VREF = 3.3V Port Function –... -

Page 26: Table 22: Rh850/F1Km-S4 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 22: RH850/F1KM-S4 Power supply architecture with mixed supply 5V & 3.3V Case 14 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 27: Power Supply Timing Of Rh850/F1Km-S4

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.3.4 Power Supply Timing of RH850/F1KM-S4 The RH850/F1KM-S4 has a recommended power supply timing. The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. -

Page 28: Figure 9: Rh850/F1Km-S4 Power Up/Down Timing

RH850/F1Kx, RH850/F1K Series Hardware Design Guide a) When RESET terminal is used REGVCC/EVCC VPOC(min) Min. 0 us Max . 0.5/t VS ms Min. 0 us Min. 0 us BVCC 3.0V Min. 0 us Max . 0.5/t VS ms Min. 0 us Min. -

Page 29: Power Supply Overview Of Rh850/F1Kh-D8

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Power Supply Overview of RH850/F1KH-D8 1.4.1 Power Supply Pin Overview of RH850/F1KH-D8 The devices of the RH850/F1KH-D8 have the following power supply pins: • Power supply voltage REG0VCC and REG1VCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain. -

Page 30: Power Supply Pin Configuration Of Rh850/F1Kh-D8

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.4.2 Power Supply Pin Configuration of RH850/F1KH-D8 The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected. • The EVCC supply pins are internally connected The BVCC supply pins are internally connected. -

Page 31: Table 25: Rh850/F1Kh-D8 Overview Of Power Supply Architecture Cases

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 25: RH850/F1KH-D8 Overview of power supply architecture cases Voltage Case Permission REG0VCC REG1VCC EVCC BVCC A0VREF A1VREF Operation not Case 1 permitted Case 2 3.3V Operation permitted Case 3 3.3V 3.3V Operation permitted Case 4 3.3V 3.3V... -

Page 32: Table 27: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 27: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 2 – Mixed Supply 5V & 3.3V Condition REG0VCC = 5V REG1VCC = 3.3V EVCC = 5V BVCC = 5V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 33: Table 29: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 29: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 4 – Mixed Supply 5V & 3.3V Condition REG0VCC = 5V REG1VCC = 3.3V EVCC = 5V BVCC = 5V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 34: Table 31: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 31: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 6 – Mixed Supply 5V & 3.3V Condition REG0VCC = 5V REG1VCC = 3.3V EVCC = 5V BVCC = 3.3V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 35: Table 33: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 33: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 8 – Mixed Supply 5V & 3.3V Condition REG0VCC = 5V REG1VCC = 3.3V EVCC = 5V BVCC = 3.3V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 36: Table 34: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 34: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 9 – Mixed Supply 5V & 3.3V Condition REG0VCC = 5V REG1VCC = 3.3V EVCC = 5V BVCC = 3.3V A0VREF = 3.3V A1VREF = 3.3V Port Function –... -

Page 37: Table 37: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 37: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 12 – Mixed Supply 5V & 3.3V Condition REG0VCC = 3.3V REG1VCC = 3.3V EVCC = 5V BVCC = don’t care A0VREF = don’t care A1VREF = don’t care Port Function... -

Page 38: Table 39: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 39: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 14 – Mixed Supply 5V & 3.3V Condition REG0VCC = 3.3V REG1VCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 39: Table 40: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 40: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 15 – Mixed Supply 5V & 3.3V Condition REG0VCC = 3.3V REG1VCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 5V A1VREF = 3.3V Port Function –... -

Page 40: Table 41: Rh850/F1Kh-D8 Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 41: RH850/F1KH-D8 Power supply architecture with mixed supply 5V & 3.3V Case 16 – Mixed Supply 5V & 3.3V Condition REG0VCC = 3.3V REG1VCC = 3.3V EVCC = 3.3V BVCC = 3.3V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 41: Power Supply Timing Of Rh850/F1Kh-D8

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.4.4 Power Supply Timing of RH850/F1KH-D8 The RH850/F1KH-D8 has a recommended power supply timing. The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. -

Page 42: Figure 14: Rh850/F1Kh-D8 Power Up/Down Timing

RH850/F1Kx, RH850/F1K Series Hardware Design Guide a) When RESET terminal is used REG0VCC/EVCC VPOC(min) Note1 Note2 DPOR DRPD Min. 0 us Min. 0us REG1VCC VPOC(min) Min. 0 us Max . 0.5/t VS ms Min. 0 us Min. 0 us BVCC 3.0V Min. -

Page 43: Figure 15: Rh850/F1Kh-D8 Power Up/Down Timing

RH850/F1Kx, RH850/F1K Series Hardware Design Guide b) When RESET terminal is not used REG0VCC/EVCC VPOC (min) Min. 0 us Max. 500 us Min. 0 us Max. 1 us REG1VCC VPOC(min) Min. 0 us Max. 500 us Min. -1 us Max. 0.5/t VS ms BVCC 3.0V Min. -

Page 44: Power Supply Overview Of Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Power Supply Overview of RH850/F1K 1.5.1 Power Supply Pin Overview of RH850/F1K The devices of the RH850/F1K have the following power supply pins: • Power supply voltage REGVCC for the on-chip voltage regulators. The output voltage of the voltage regulators is supplied to the digital circuits in each power domain. -

Page 45: Power Supply Pin Configuration Of Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.5.2 Power Supply Pin Configuration of RH850/F1K The following shows power supply pin configuration. Do not open any power and GND terminals even if those are internally connected. The EVCC supply pins are internally connected •... -

Page 46: Table 44: Rh850/F1K Overview Of Power Supply Architecture Cases

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 44: RH850/F1K Overview of power supply architecture cases Voltage Permission Case REGVCC EVCC A0VREF A1VREF Case 1 Operation permitted Case 2 3.3V Operation permitted Case 3 3.3V Operation permitted Case 4 3.3V 3.3V Operation permitted Case 5 3.3V... -

Page 47: Table 47: Rh850/F1K Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 47: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V Case 3 – Mixed Supply 5V & 3.3V Condition REGVCC = 5V EVCC = 5V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 48: Table 50: Rh850/F1K Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 50: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V Case 7 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V A0VREF = 5V A1VREF = 5V Port Function –... -

Page 49: Table 51: Rh850/F1K Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 51: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V Case 8 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V A0VREF = 5V A1VREF = 3.3V Port Function –... -

Page 50: Table 52: Rh850/F1K Power Supply Architecture With Mixed Supply 5V & 3.3V

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 52: RH850/F1K Power supply architecture with mixed supply 5V & 3.3V Case 9 – Mixed Supply 5V & 3.3V Condition REGVCC = 3.3V EVCC = 3.3V A0VREF = 3.3V A1VREF = 5V Port Function –... -

Page 51: Power Supply Timing Of Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 1.5.4 Power Supply Timing of RH850/F1K The RH850/F1K has a recommended power supply timing. The voltage slope of the different power supply pins is defined with min. 0.02V/ms and max. 500V/ms. Satisfy the spec of voltage slope by using power IC with enable control or by using power IC which starts output over VPOC. -

Page 52: Figure 19: Rh850/F1K Power Up/Down Timing

RH850/F1Kx, RH850/F1K Series Hardware Design Guide c) When RESET terminal is used REGVCC/EVCC VPOC(min) Min. 0 us Max. 0.5/tVS ms Min. 0 us Min. 0 us A0VREF 3.0V Min. 0 us Max. 0.5/tVS ms Min. 0 us Min. 0 us A1VREF 3.0V RESET... -

Page 53: Principle Capacitor Placement At Regvcc Of Rh850/F1Kx, Rh850/F1K Series

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Principle Capacitor Placement at REGVCC of RH850/F1Kx, RH850/F1K Series It should be considered to add an additional capacitor to the REGVCC pin and to use a close component placement to the supply pin in order to optimize the EMI noise behavior especially during the program and erase operation. The following recommendations shall be considered for the capacitor placement of the additional capacitor for EMI optimization especially during the program and erase operation at the REGVCC pin: •... -

Page 54: Minimum External Components

Hardware Design Guide Minimum External Components The RH850/F1Kx series requires a certain number of external connections and components for a proper operation in normal operating mode. The components are shown in different categories depending on the device operation and the use case. -

Page 55: Table 54: Minimum External Components Of Rh850/F1Km-S1 (100Pin)

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 54: Minimum external components of RH850/F1KM-S1 (100pin) Component Value Category Min. Typ. Max. Note1 Note1 Typical 1kΩ Note 3 10kΩ Note 3 Required 86kΩ Note 6 Required 10kΩ Note 5 Typical 1kΩ Note 8 10kΩ... - Page 56 RH850/F1Kx, RH850/F1K Series Hardware Design Guide The definition of components categories is as follows: Required component • Component that must be implemented as part of the device specification. • Recommended component Component that is not required by the device specification, but is provided in order to secure the device operating conditions.

-

Page 57: Minimum External Components Of Rh850/F1Km-Xx

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Minimum External Components of RH850/F1KM-XX Reserved for future use R01AN3841ED0110 Rev. 1.10 Page 57 of 108 August 8, 2019... -

Page 58: Minimum External Components Of Rh850/F1Km-S4

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Minimum External Components of RH850/F1KM-S4 REGVCC EVCC REGVCC AWOVCL EVCC EVCC EVCC EVCC ISOVCL Port Port IP0_0 EVCC RESET Core FLMD0 Logic Logic Flash P10_8/FLMD1 DCUTRST DCUTDI Debug DCUTDO DCUCLK DCURDY DCUTMS ADCA0 Port EVTO BVCC BVCC... -

Page 59: Table 55: Minimum External Components For Rh850/F1Km-S4 (272Pin)

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 55: Minimum external components for RH850/F1KM-S4 (272pin) Component Value Category Min. Typ. Max. Note1 Note1 Typical Note1 Typical Note 1 Typical 1kΩ Note 3 10kΩ Note 3 Required 86kΩ Note 6 Required 10kΩ Note 5 Typical 1kΩ... - Page 60 RH850/F1Kx, RH850/F1K Series Hardware Design Guide The definition of components categories is as follows: Required component • Component that must be implemented as part of the device specification. • Recommended component Component that is not required by the device specification, but is provided in order to secure the device operating conditions.

-

Page 61: Minimum External Components Of Rh850/F1Kh-D8

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Minimum External Components of RH850/F1KH-D8 REG0VCC EVCC REG1VCC REG0VCC AWOVCL EVCC EVCC EVCC EVCC REG1VCC ISOVCL Port Port IP0_0 EVCC RESET Core FLMD0 Logic Logic Flash P10_8/FLMD1 DCUTRST DCUTDI Debug DCUTDO DCUCLK DCURDY DCUTMS ADCA0 Port EVTO... -

Page 62: Table 56: Minimum External Components For Rh850/F1Kh-D8 (324Pin)

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 56: Minimum external components for RH850/F1KH-D8 (324pin) Component Value Category Min. Typ. Max. Note1 Note1 Typical Note1 Typical Note 1 Typical 1kΩ Note 3 10kΩ Note 3 Required 86kΩ Note 6 Required 10kΩ Note 5 Typical 1kΩ... - Page 63 RH850/F1Kx, RH850/F1K Series Hardware Design Guide The definition of components categories is as follows: Required component • Component that must be implemented as part of the device specification. • Recommended component Component that is not required by the device specification, but is provided in order to secure the device operating conditions.

-

Page 64: Minimum External Components Of Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Minimum External Components of RH850/F1K REGVCC EVCC REGVCC AWOVCL EVCC EVCC EVCC EVCC ISOVCL Port Port IP0_0 EVCC RESET Core FLMD0 Logic Logic Flash P10_8/FLMD1 DCUTRST DCUTDI Debug DCUTDO DCUCLK DCURDY DCUTMS ADCA0 EVTO A0VREF Figure 25: Minimum external components of RH850/F1K in normal operating mode Note: The debug interface connections shown covers Nexus, LPD (1 pin) and LPD (4 pins). -

Page 65: Table 57: Minimum External Components For Rh850/F1K (176Pin)

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Table 57: Minimum external components for RH850/F1K (176pin) Component Value Category Min. Typ. Max. Note1 Note1 Typical Note1 Typical Note 1 Typical 1kΩ Note 3 10kΩ Note 3 Required 86kΩ Note 6 Required 10kΩ Note 5 Typical 1kΩ... - Page 66 RH850/F1Kx, RH850/F1K Series Hardware Design Guide The definition of components categories is as follows: Required component • Component that must be implemented as part of the device specification. • Recommended component Component that is not required by the device specification, but is provided in order to secure the device operating conditions.

-

Page 67: Oscillator

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Oscillator Recommended Oscillator Circuit 3.1.1 Main Oscillator A crystal or ceramic resonator can be connected to the main clock input pins as shown below. internal internal external external MOSC MOSC Figure 26: Recommended main oscillator circuit General guidance values of the main oscillator circuit: Table 58: Guidance values of the main oscillator circuit Component... -

Page 68: Sub Oscillator

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 3.1.2 Sub Oscillator A crystal resonator can be connected to the sub clock input pins as shown below. IP0_0 internal external SOSC Figure 27: Recommended sub oscillator circuit General guidance values of the sub oscillator circuit: Table 59: Guidance values of the sub oscillator circuit Component Value... -

Page 69: Recommended Oscillator Layout

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Oscillator Layout General guidance for PCB layout: • Keep the wiring length as short as possible Do not cross the wiring with other signal lines • Do not route this circuit close to a signal line with high fluctuating current flow •... -

Page 70: Device Pins

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Device Pins 4.1.1 Direct Clock Supply to X1 A clock waveform from an external clock source can be used as clock supply to the X1 pin of the microcontroller. The device has to be configured by software (register MOSCM) appropriately for the direct clock input. In this case, set the MOSCM bit of the MOSCM register to 1 before clock input to X1 pin is applied. -

Page 71: Reset

RH850/F1Kx, RH850/F1K Series Hardware Design Guide RESET 4.2.1 Minimum RESET Circuit The RH850/F1Kx, RH850/F1K series has an on-chip Power-on Clear (POC) circuit. Therefore, a specific external RESET circuit is not required and the minimum requirement of the RESET circuit is a resistor to EVCC for start-up of the device. -

Page 72: Reset Input Characteristics

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.2.2 RESET Input Characteristics The RESET is passed through an internal analog noise filter to prevent erroneous resets due to spikes. The following figure shows the timing when an external reset is performed. It explains the effect of the noise elimination. -

Page 73: General Purpose I/O

RH850/F1Kx, RH850/F1K Series Hardware Design Guide General Purpose I/O 4.3.1 RESET State of General Purpose I/P During RESET state, all general-purpose I/O pins are in input mode with high-Z behavior except the pins JP0_4/ DCUTRST and P8_6/ RESETOUT . 4.3.2 JP0_4/ DCUTRST During power-on or when RESET is at low level the pin JP0_4 should not be driven externally to high-level. -

Page 74: Analog Filter Function

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.3.4 Analog Filter Function Depending on the alternative port functionality selected, some input signals of the device pins are passed through an analog filter - respectively analog delay stage - to remove noise and glitches from the input signal. The detection level of the filtered input signal depends on the high-level/low-level input voltage of the port input buffer and its supported electrical characteristics. -

Page 75: Port And Pin Behavior During Low Power Mode

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.3.5 Port and Pin Behavior during Low Power Mode During the low power modes, different states apply for the ports and pins of the RH850/F1Kx, RH850/F1K series. The states depend on the chosen low-power mode and may not have the same behavior for pins used as GPIO and used as alternative functions. -

Page 76: Recommended Connection Of Unused Pins

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Connection of Unused Pins 4.4.1 Recommended Connection of Unused Pins for RH850/F1KM-S1 Table 62: Recommended connection of unused pins for RH850/F1KM-S1 Recommended Connection of Unused Pin A0VREF Connect to EVCC A0VSS Connect to EVSS RESET Connect to EVCC via a resistor Connect to AWOVSS via a resistor... - Page 77 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Connection of Unused Pin JP0 (excluding JP0_4) – General-purpose I/O Input state Mode - Leave open (PIBCn_m = 0 and PMCn_m = 0) - Connect to EVCC or EVSS via resistor (PIBCn_m = 1 and PMCn_m = 1) Output state - Leave open JP0_4 –...

-

Page 78: Recommended Connection Of Unused Pins For Rh850/F1Km-Xx

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.4.2 Recommended Connection of Unused Pins for RH850/F1KM-XX Reserved for future use R01AN3841ED0110 Rev. 1.10 Page 78 of 108 August 8, 2019... -

Page 79: Recommended Connection Of Unused Pins For Rh850/F1Km-S4

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.4.3 Recommended Connection of Unused Pins for RH850/F1KM-S4 Table 63: Recommended connection of unused pins for RH850/F1KM-S4 Recommended Connection of Unused Pin [144pin, 176pin, 233pin and 272pin] A0VREF, A1VREF Note1 Connect to EVCC or BVCC [100pin] Connect to EVCC A0VSS, A1VSS... - Page 80 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Connection of Unused Pin P10_1 Input state - Leave open (PIBCn_m = 0 and PMCn_m = 0) P10_2 - Connect to EVSS via resistor (PIBCn_m = 1 and P10_6 PMCn_m = 1) P10_8 Output state - Leave open Input state...

-

Page 81: Recommended Connection Of Unused Pins For Rh850/F1Kh-D8

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.4.4 Recommended Connection of Unused Pins for RH850/F1KH-D8 Table 64: Recommended connection of unused pins for RH850/F1KH-D8 Recommended Connection of Unused Pin A0VREF, A1VREF Connect to EVCC or BVCC A0VSS, A1VSS Connect to EVSS or BVSS RESET Connect to EVCC or BVCC via a resistor Connect to AWOVSS via a resistor... - Page 82 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Connection of Unused Pin Input state - Leave open (PIBCn_m = 0) - Connect to A0VREF or A0VSS via resistor (PIBCn_m = 1) Output state - Leave open Input state - Leave open (PIBCn_m = 0) - Connect to A1VREF or A1VSS via resistor (PIBCn_m = 1) Output state...

-

Page 83: Recommended Connection Of Unused Pins For Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 4.4.5 Recommended Connection of Unused Pins for RH850/F1K Table 65: Recommended connection of unused pins for RH850/F1K Recommended Connection of Unused Pin A0VREF, A1VREF Note1 Connect to EVCC A0VSS, A1VSS Connect to EVSS Note1 Connect to EVCC via a resistor RESET Connect to AWOVSS via a resistor... - Page 84 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Recommended Connection of Unused Pin Input state - Leave open (PIBCn_m = 0) - Connect to A0VREF or A0VSS via resistor (PIBCn_m = 1) Output state - Leave open Input state - Leave open (PIBCn_m = 0) - Connect to A1VREF or A1VSS via resistor (PIBCn_m = 1) Output state...

-

Page 85: Injected Current

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Injected Current The RH850/F1Kx, RH850/F1K series has different electrical characteristics for the injected current depending on the pin group and device pins of the different package variants. When a current is applied to the protection diodes of the device, the current that exceeds the limit of the microcontroller will increase or decrease the supply voltage or GND level of the device. -

Page 86: Sent Interface (Rh850/F1Kx Series Only)

When the SPC extension is used an external transistor is required in order to pull-down the RX line to initiate a SENT message transmission. In the RH850/F1Kx series this is realized by controlling an external transistor connected to the RSENTnSPCO pin. The polarity of the RSENTnSPCO pin can be configured by software (by RSENTnCC.SOPC bit). -

Page 87: Ad-Converter

RH850/F1Kx, RH850/F1K Series Hardware Design Guide AD-Converter Conversion time The ADC conversion time consists of a number of timing parameters, which are summed-up to get the conversion timing depending on the application. Total conversion time (single channel) SG setup MPX setup Sampling Conversion SG end... -

Page 88: External Multiplexer Wait Time

RH850/F1Kx, RH850/F1K Series Hardware Design Guide External Multiplexer Wait Time The analog input stabilization time can be defined for each physical channel of the ADC by register settings (registers ADCAnMPXSTBTSELR0 to 4, ADCAnMPXSTBTR0 to 7) when an external analog multiplexer is used. For details, please refer to Section 38, A/D Converter (ADCA) of the RH850/F1KH, RH850/F1KM Hardware User’s Manual or Section 31, A/D Converter (ADCA) of the RH850/F1K Hardware User’s Manual. -

Page 89: External Circuit On Adc Input

RH850/F1Kx, RH850/F1K Series Hardware Design Guide External Circuit on ADC Input To preserve the accuracy of the A/D-converter, it is recommended that analog input pins have a low impedance. Therefore, placing a capacitor at the analog input pin can provide an effective result. This capacitor contributes to noise filtering on the analog input pin. -

Page 90: Formulas For Sampling Error

RH850/F1Kx, RH850/F1K Series Hardware Design Guide As guide line for the calculation of the external capacitor at the analog input pin the formula based on the internal equivalent capacitance and the ADC resolution of the corresponding AD-converter channel can be used. In this case, sampling error based on charge-sharing between Ce and CIN will be roughly 1 LSB at the start timing of sampling. -

Page 91: Figure 37: Schematic For Sampling Error 2 Formula

RH850/F1Kx, RH850/F1K Series Hardware Design Guide b) Errors (Sampling error 2) which depend on conversion cycles with charge sharing A formula for errors in sampled values due to the external circuit of the A/D converter is given below. These errors will depend on the input circuit and conversion cycle. -

Page 92: Device Operation Modes

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Device Operation Modes The RH850/F1Kx series and RH850/F1K series support the following operation modes that are used for normal operation, debugging, flash programming and test by using boundary scan. Table 68: Device operation mode overview... -

Page 93: Development Tool Interface

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Development Tool Interface The description of the development tool interface in this chapter assumes that the normal operating mode of the MCU is used. When the user boot mode shall be used the configuration of the pins FLMD0, P10_8/FLMD1, P10_1/MODE0, P10_2/MODE1 and P10_6/MODE2 has to be set accordingly. - Page 94 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Notes: The maximum sink current of the RESET terminal of the E1/E2 emulator is 2mA. The external pull-up circuit of the RESET pin has to be considered based on the applications requirement. When an external RESET component is used, the pull-up resistor value has to be selected appropriately.

-

Page 95: Figure 39: Lpd (4 Pins) Connection

RH850/F1Kx, RH850/F1K Series Hardware Design Guide E1/E2 Emulator RH850/F1Kx, RH850/F1K (14pin Connector) EVCC TVDD EVSS TDI/LPDIO JP0_0 (DCUTDI/LPDIO, LPDI) TDO/LPDO JP0_1 (DCUTDO/LPDO) TCK/LPDCLK JP0_2 (DCUTCK/LPDCLK) JP0_4 (DCUTRST) RDY/LPDCLKOUT JP0_5 (DCURDY/LPDCLKOUT) FLMD0 FPMD0 Note 2 FPMD1 P10_8 (FLMD1) Min. 10k to 100kΩ 1k to 10kΩ... -

Page 96: Figure 40: Nexus, Lpd (4 Pins) And Lpd (1 Pin) Connection

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Emulator RH850/F1Kx, RH850/F1K (14pin Connector) TVDD EVCC EVSS Note 2 Note 3 1k to 10kΩ TDI/LPDIO JP0_0 (DCUTDI/LPDIO, LPDI) TDO/LPDO JP0_1 (DCUTDO/LPDO) TCK/LPDCLK JP0_2 (DCUTCK/LPDCLK) JP0_3 (DCUTMS) TRST JP0_4 (DCUTRST) RDY/LPDCLKOUT JP0_5 (DCURDY/LPDCLKOUT) Note 5 EVTO JP0_6 (EVTO) FPMD0... -

Page 97: Table 70: Debug Interface Signal Connection

RH850/F1Kx, RH850/F1K Series Hardware Design Guide When the Nexus debug mode is used, the ports of the JP0 port group are automatically switched to the debug interface mode. • JP0_0: DCUTDI input JP0_1: DCUTDO output • JP0_2: DCUTCK input • JP0_3: DCUTMS input •... -

Page 98: Flash Programming Interface

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Flash Programming Interface For the programming environment PG-FPx, the following connections are supported: • Single-wire asynchronous flash programming interface Two-wire asynchronous flash programming interface • Synchronous flash programming interface • For the programming environment combination of E1/E2 emulator and RFP, the following connections are supported: •... -

Page 99: Flash Programming By E1/E2 Emulator And Rfp

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Note: Design the circuit in the way that the FLMD1 pin must be at the low level during serial programming. During programming, it outputs a low level on FPMD1 to place the device in the serial programming mode. -

Page 100: Table 73: E1/E2 Flash Programming Signal Connection

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Note: Design the circuit in the way that the FLMD1 pin must be at the low level during serial programming. During programming (using the RFP), it outputs a low level on FPMD1 to place the device in the serial programming mode. -

Page 101: Combined Debug And Flash Programming Interface Connection

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Combined Debug and Flash Programming Interface Connection The following figure describes the combined connections for debugging and flash programming, supporting • Low pin debug interface (1 pin) - hereinafter called "LPD (1 pin)" Low pin debug interface (4 pins) - hereinafter called "LPD (4 pins)" •... - Page 102 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Design the circuit in the way that the FLMD1 pin must be at the low level during serial programming. During programming (using the RFP), it outputs a low level on FPMD1 to place the device in the serial programming mode. If necessary, connect FPMD1 and FLMD1.

-

Page 103: Debug Considerations When Hot Plug-In Is Used

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Debug Considerations when Hot Plug-in is used When it is planned to use the hot plug-in function for debugging the following topics should be considered. RESET pin When the hot plug-in will be used it is recommended to consider the installation of a capacitor between the reset signal and GND in order to suppress a noise. -

Page 104: Test Tool Interface

RH850/F1Kx, RH850/F1K Series Hardware Design Guide Test Tool Interface The boundary scan test is compliant with IEEE Standard 1149.1 and certain boundary scan instructions are supported. When the boundary scan mode shall be used, several connections have to be done between boundary scan test tool and the device. -

Page 105: 10. Differences To Rh850/F1L/M/H, Rh850/F1Kx And Rh850/F1K

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 10. Differences to RH850/F1L/M/H, RH850/F1Kx and RH850/F1K This chapter provides an overview about the differences between the RH850/F1KM, RH850/F1KH, RH850/F1x and RH850/F1K. For details about device related differences, please refer to the application note “F1KM Migration Guide” (R01AN2917EDxxxx). -

Page 106: 11. Reference Documents

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 11. Reference Documents Item Document No. Document Title R01UH0684EJxxxx Preliminary User’s Manual Hardware RH850/F1KH, RH850/F1KM (including electrical characteristics) R20UT3985EJxxxx E1/E20 Emulator, E2 Emulator Additional Document for User’s Manual (Notes on Connection of RH850/F1KH and RH850/F1KM) R01AN2917EDxxxx Application Note “F1KM Migration Information”... -

Page 107: 12. Abbreviations

RH850/F1Kx, RH850/F1K Series Hardware Design Guide 12. Abbreviations A/D-converter HSOSC internal High-speed Oscillator HWTRG Hardware Trigger MOSC Main Oscillator Multiplexer Scan Group SOSC Sub Oscillator SWTRG Software Trigger R01AN3841ED0110 Rev. 1.10 Page 107 of 108 August 8, 2019... - Page 108 RH850/F1Kx, RH850/F1K Series Hardware Design Guide Website and Support Renesas Electronics Website http://www.renesas.com/ Inquiries http://www.renesas.com/contact/ All trademarks and registered trademarks are the property of their respective owners. R01AN3841ED0110 Rev. 1.10 Page 108 of 108 August 8, 2019...

- Page 109 Initial version 0.90 2017-07-11 Typing error correction Description of RH850/F1KH-D8 added to related chapters Change of some chapter titles due to Renesas internal rules Added description about electromagnetic interference and susceptibility 4.3.5 Changed “HALT Mode” to “HALT State” Reference of RH850 SENT application note added...

- Page 110 Changed capacitor value • • Modified contents of the table and notes Modified the power source of Flash • Added information of gain setting in the caution 4.3.5 Modified the contents of the table Added detailed information about injected current Modified the number of clocks on the figure of ADC conversion time Removed RIN and CIN values for ADC equivalent circuit, and...

- Page 111 General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

Need help?

Do you have a question about the RH850/F1Kx Series and is the answer not in the manual?

Questions and answers