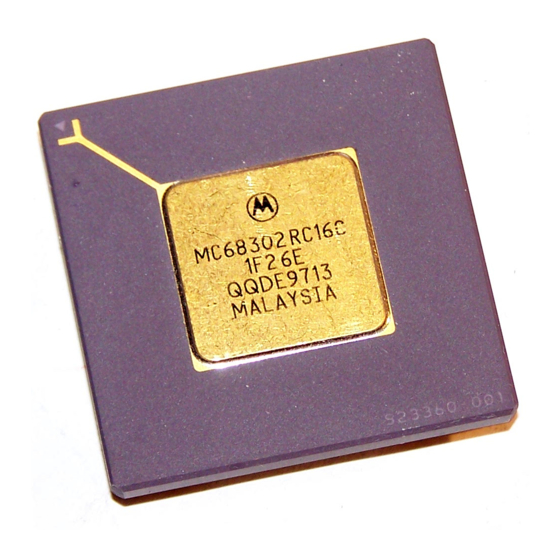

Motorola MC68302 Manuals

Manuals and User Guides for Motorola MC68302. We have 2 Motorola MC68302 manuals available for free PDF download: User Manual

Motorola MC68302 User Manual (480 pages)

Integrated Multiprotocol Processor

Brand: Motorola

|

Category: Computer Hardware

|

Size: 1.86 MB

Table of Contents

-

-

Features25

-

-

-

DMA Control52

-

Key Features52

-

Done58

-

Reset65

-

Bus Error65

-

Halt65

-

Overview66

-

Port a79

-

Port B81

-

Pb7-Pb081

-

Pb11-Pb882

-

Timers85

-

System Control100

-

Low-Power Mode111

-

Freeze Control115

-

Hardware Setup116

-

Initialization118

-

-

-

Main Controller121

-

SDMA Channels123

-

Command Set125

-

IDL Interface131

-

GCI Interface134

-

PCM Highway Mode136

-

SCC Features144

-

UART Controller163

-

UART Memory Map166

-

UART Command Set169

-

Send Break173

-

Wakeup Timer173

-

HDLC Controller186

-

HDLC Memory Map189

-

HDLC Command Set190

-

DDCMP Memory Map223

-

-

Controller235

-

-

Event Register241

-

Mask Register242

-

Overview258

-

SMC Commands260

-

Power Pins266

-

-

-

Clocks268

-

System Control269

-

Bus Control Pins272

-

Timer Pins284

-

Chip-Select Pins286

-

No-Connect Pins287

-

-

-

Maximum Ratings289

-

-

-

Reset Circuit353

-

Memory Interface354

-

Memory Circuit354

-

New Pointers359

-

Final Comments361

-

IDMA Overview373

-

Final Notes380

-

M68000 Core381

-

IDL Bus381

-

D.6.4 IDL Bus381

-

SCP Bus387

-

D.6.10 SCP Bus387

-

Clocking393

-

Arbitration394

-

Final Notes395

-

Other NMSI Modes406

-

BISYNC Mode406

-

Transync Mode408

-

5- or 6-Bit UART417

-

Synchronous UART417

Advertisement

Motorola MC68302 User Manual (290 pages)

Integrated Multi-Protocol Processor

Brand: Motorola

|

Category: Computer Hardware

|

Size: 21.09 MB

Table of Contents

-

Features20

-

Key Features50

-

Done56

-

-

Operation65

-

-

-

Timers81

-

Freeze Control102

-

Main Controller104

-

SDMA Channels104

-

Command Set106

-

IDL Interface108

-

GCI Interface112

-

PCM Highway Mode116

-

-

SCC Features122

-

UART Controller136

-

UART Memory Map138

-

UART Command Set140

-

Send Break143

-

Wakeup Timer144

-

-

HDLC Controller155

-

HDLC Memory Map157

-

HDLC Command Set158

-

DDCMP Controller189

-

DDCMP Memory Map192

-

Controller205

-

Event Register212

-

Mask Register213

-

Overview216

-

Power Pins225

-

Clocks225

-

System Control227

-

Bus Control Pins229

-

Timer Pins240

-

Chip-Select Pins241

-

Maximum Ratings242