Infineon XMC4000 series Microcontroller Manuals

Manuals and User Guides for Infineon XMC4000 series Microcontroller. We have 12 Infineon XMC4000 series Microcontroller manuals available for free PDF download: Reference Manual, Application Manual, Device Manual, Board User's Manual, User Manual

Infineon XMC4000 series Reference Manual (2689 pages)

ARM Cortex-M4

32-bit processor core

Brand: Infineon

|

Category: Microcontrollers

|

Size: 18 MB

Table of Contents

-

-

Introduction48

-

Introduction49

-

Overview49

-

Overview60

-

Features61

-

Stacks63

-

Data Types76

-

Memory Model79

-

Vector Table89

-

Fault Types96

-

Lockup98

-

MPU Mismatch109

-

Enabling the FPU113

-

PPB Registers113

-

Table 2-6 Table114

-

SCS Registers117

-

Table 2-8 Table130

-

NVIC Registers146

-

MPU Registers152

-

FPU Registers160

-

Bus System170

-

Bus Interfaces170

-

Bus Matrix170

-

Overview173

-

Features173

-

Block Diagram174

-

Debug Behavior195

-

Registers196

-

DLR Registers196

-

Table 2-10 Table196

-

Table 2-12 Table196

-

ERU Registers201

-

Interconnects206

-

ERU1 Connections207

-

ERU0 Connections207

-

Table 2-14 Table209

-

Table 2-16 Table210

-

Table 2-18 Table211

-

Overview217

-

Features217

-

Block Diagram219

-

Terminology220

-

FIFO Usage230

-

Scatter/Gather233

-

Basic Transfers237

-

Table 2-20 Table247

-

Registers275

-

Table 2-22 Table276

-

Table 4-1 Table277

-

Table 4-3 Table278

-

Table 5-2 Table309

-

Table 4-7 Table309

-

Table 4-9 Table309

-

Table 4-5 Table309

-

Table 5-6 Table312

-

Overview342

-

Features342

-

Block Diagram343

-

Basic Operation346

-

Debug Behavior350

-

Registers352

-

Table 5-10 Table352

-

Table 6-1 Table352

-

Interconnects365

-

Overview368

-

Features368

-

Memory Regions370

-

Memory Map370

-

Debug Behavior376

-

Registers377

-

Overview381

-

Block Diagram381

-

Boot ROM (BROM)382

-

BROM Addressing382

-

Prefetch Unit382

-

Overview382

-

Operation383

-

Data Buffer383

-

PMU Interface384

-

Overview385

-

Features385

-

Flash Structure387

-

Flash Protection397

-

Margin Checks403

-

Trap Control404

-

Power Supply409

-

Power Reduction409

-

Reset Control411

-

Clock413

-

Registers413

-

PMU Registers413

-

PMU ID Register414

-

Flash Registers417

-

Overview435

-

Features435

-

Block Diagram436

-

Time-Out Mode437

-

Pre-Warning Mode438

-

Debug Behavior441

-

Registers445

-

Interconnects450

-

Overview452

-

Features452

-

Block Diagram452

-

RTC Operation453

-

Debug Behavior456

-

Registers459

-

Interconnects471

-

Features472

-

Overview472

-

Block Diagram473

-

Service Requests477

-

Trap Generation480

-

Trap Sources480

-

Gain Adjustment483

-

Retention Memory484

-

Power Management485

-

System States486

-

Power-On Reset490

-

Power Validation491

-

Hibernate Mode492

-

Reset Control496

-

Block Diagram498

-

Reset Status498

-

Clock Control498

-

Clock Sources500

-

Main PLL508

-

Features508

-

Bypass Mode514

-

Usb Pll518

-

Debug Behavior520

-

Power-Up523

-

Registers532

-

GCU Registers532

-

PCU Registers583

-

HCU Registers589

-

RCU Registers597

-

CCU Registers615

-

Overview642

-

Features642

-

Block Diagram643

-

LED Drive Mode648

-

Touch-Sense Mode651

-

Finger Sensing654

-

Debug Behavior656

-

Software Hints661

-

Registers663

-

Interconnects677

-

Features679

-

Overview679

-

Block Diagram680

-

Card Detection684

-

Debug Behavior688

-

Error Detection688

-

Read Operation692

-

Write Operation692

-

Registers694

-

Table 13-8739

-

Table 13-9744

-

Interconnects767

-

Overview770

-

Features770

-

Block Diagram771

-

Clocking Modes782

-

Standby Mode784

-

Sole Master Mode796

-

Arbiter Mode796

-

No Bus Mode796

-

Participant Mode800

-

Burst Phase (BP)808

-

Signal List811

-

NAND Flash819

-

Signals822

-

Cellular RAM832

-

SDRAM Interface836

-

Features836

-

Signal List836

-

Burst Accesses844

-

Bank Mask846

-

Row Mask847

-

Banks Precharge848

-

Refresh Cycles849

-

Power down Mode859

-

Module Reset862

-

Debug Behavior862

-

Clocks862

-

Power863

-

Registers864

-

Overview893

-

Block Diagram897

-

ETH Core898

-

Transmission898

-

Reception902

-

Transmit Path910

-

Receive Path916

-

DMA Controller918

-

Initialization919

-

Transmission922

-

Reception927

-

Interrupts931

-

DMA Descriptors933

-

PHY Interconnect971

-

Clock Types986

-

Debug999

-

ETH Registers1000

-

Register Description1000

-

Registers Overview1001

-

-

Interconnects1224

-

-

-

Block Diagram1230

-

-

USB Device1232

-

FIFO Architecture1233

-

Programming Overview1235

-

Core Initialization1239

-

Host Connection1241

-

Halting a Channel1243

-

Handling Disconnects1245

-

Handling Interrupts1252

-

Handling Interrupts1255

-

Handling Interrupts1257

-

Handling Interrupts1263

-

Handling Interrupts1265

-

-

Handling Interrupts1271

-

-

-

Handling Interrupts1274

-

-

Handling Interrupts1277

-

Handling Interrupts1279

-

IN Memory Structure1287

-

OUT Memory Structure1290

-

Device Disconnection1301

-

IN Endpoint Disable1308

-

IN Data Transfers1321

-

OUT Data Transfers1322

-

Examples1327

-

SPRAM Requirements1377

-

Isochronous out1384

-

Internal Data Flow1399

-

Debug Behaviour1460

-

Registers1462

-

Register Description1469

-

Interconnects1572

-

-

Operating the USIC1578

-

Output Signals1580

-

Baud Rate Generator1581

-

Mode Control1588

-

Digital Filter1597

-

Capture Mode Timer1600

-

Time Quanta Counter1601

-

FIFO Buffer Bypass1622

-

-

Frame Format1627

-

-

Idle Time1628

-

Start Bit Detection1629

-

Operating the ASC1630

-

Baud Rate Generation1631

-

-

Noise Detection1632

-

Hardware LIN Support1644

-

Shift Clock Signals1649

-

Slave Select Signals1651

-

Operating the SSC1653

-

Disabling SSC Mode1654

-

Transfer Mode1656

-

-

Baud Rate Generation1660

-

-

MSLS Generation1661

-

End-Of-Frame Control1665

-

-

End-Of-Frame Control1668

-

-

Symbols1681

-

Frame Format1682

-

Operating the IIC1683

-

Transmission Chain1684

-

Receiver Handling1688

-

Symbol Timing1689

-

Start Symbol1690

-

Stop Symbol1691

-

Data Flow Handling1692

-

Protocol Overview1707

-

Transfer Delay1708

-

Operating the IIS1709

-

Parity Mode1712

-

Baud Rate Generation1715

-

WA Generation1716

-

-

Registers1725

-

Address Map1728

-

Input Stage Register1743

-

-

Interconnects1798

-

-

Overview1824

-

Block Diagram1826

-

-

CAN Basics1827

-

CAN Frame Formats1828

-

Remote Frames1830

-

Error Frames1832

-

The Nominal Bit Time1833

-

Port Input Control1838

-

CAN Node Control1839

-

Bit Timing Unit1840

-

Bitstream Processor1841

-

Error Handling Unit1842

-

CAN Frame Counter1843

-

List Command Panel1847

-

Bit Timing Analysis1851

-

Pending Messages1859

-

Frame Transmission1864

-

Receive FIFO1870

-

Transmit FIFO1871

-

Gateway Mode1872

-

-

Debug Behavior1877

-

-

Register Description1881

-

CAN Node Registers1896

-

Interconnects1942

-

Conversion Timing1972

-

Alias Feature1973

-

Conversion Modes1974

-

Data Alignment1982

-

Wait-For-Read Mode1983

-

Result FIFO Buffer1984

-

Data Modification1986

-

Equidistant Sampling1996

-

Safety Features1997

-

-

Registers2004

-

System Registers2009

-

General Registers2012

-

Result Registers2047

-

-

Interconnects2079

-

-

Input Data Selection2098

-

External Modulator2099

-

Main Filter Chain2100

-

Integrator Stage2101

-

Auxiliary Filter2102

-

Resolver Support2105

-

Time-Stamp Support2109

-

-

System Registers2111

-

-

General Registers2113

-

Input Path Control2114

-

Filter Configuration2118

-

-

Interconnects2130

-

-

-

Block Diagram2134

-

-

Operating Modes2135

-

Data Output Stage2137

-

Data Processing Mode2141

-

Ramp Generation Mode2144

-

Registers2147

-

Register Description2148

-

DAC Data Registers2156

-

-

Interconnects2160

-

-

Digital Connections2161

-

-

Features2165

-

Block Diagram2167

-

Input Selector2171

-

Connection Matrix2173

-

-

-

Counting Modes2176

-

Edge Aligned Mode2182

-

Center Aligned Mode2183

-

Single Shot Mode2184

-

Active/Passive Rules2185

-

-

External Start/Stop2186

-

External Load2191

-

External Capture2192

-

External Modulation2198

-

TRAP Function2200

-

Status Bit Override2202

-

-

Timer Concatenation2206

-

PWM Dithering2211

-

Prescaler2216

-

-

CCU4 Usage2219

-

Prescaler Usage2221

-

-

PWM Dither2223

-

Capture Mode Usage2226

-

Debug Behavior2234

-

-

Module Reset2235

-

Power2236

-

Registers2238

-

Global Registers2244

-

-

-

Interconnects2294

-

-

CCU41 Pins2299

-

CCU42 Pins2304

-

CCU43 Pins2309

-

-

Features2316

-

Block Diagram2319

-

-

Input Selector2323

-

Connection Matrix2325

-

Start/Stop Control2327

-

Counting Modes2328

-

Edge Aligned Mode2334

-

Center Aligned Mode2335

-

Single Shot Mode2336

-

Active/Passive Rules2337

-

External Load2355

-

External Capture2356

-

External Modulation2361

-

Trap Function2363

-

Status Bit Override2366

-

Timer Concatenation2372

-

-

PWM Dithering2381

-

-

Prescaler2385

-

CCU8 Usage2388

-

Prescaler Usage2390

-

PWM Dither2393

-

Capture Mode Usage2395

-

Parity Checker Usage2400

-

Debug Behavior2406

-

Clocks2407

-

Power2408

-

-

System Dependencies2409

-

Registers2410

-

-

Global Registers2418

-

-

Interconnects2481

-

-

CCU81 Pins2489

-

-

Features2499

-

-

Block Diagram2500

-

Function Selector2503

-

Hall Sensor Control2504

-

Index Control2514

-

Using the POSIF2516

-

-

Debug Behavior2529

-

-

Power2531

-

System Dependencies2532

-

Registers2533

-

Global Registers2535

-

-

-

Interrupt Registers2551

-

Interconnects2558

-

-

POSIF0 Pins2559

-

POSIF1 Pins2563

-

Features2570

-

Definition of Terms2571

-

-

Output Operation2573

-

Analog Ports2576

-

Port Output Register2592

-

Port Input Register2594

-

Package Pin Summary2598

-

Port I/O Functions2605

-

Table 14-1 Table2606

-

Table 14-3 Table2607

-

Table 14-5 Table2608

-

Table 14-7 Table2610

-

Startup Modes2613

-

Startup Modes2615

-

Boot Mode Selection2617

-

Normal Boot Mode2618

-

Boot from PSRAM2623

-

CAN BSL Mode2630

-

-

Debug Behavior2637

-

-

-

Clocking2641

-

Timestamping2655

-

ROM Table2656

Advertisement

Infineon XMC4000 series Application Manual (93 pages)

Brand: Infineon

|

Category: Microcontrollers

|

Size: 8 MB

Table of Contents

-

-

Sensing14

-

Modulation14

-

-

Interleave34

Infineon XMC4000 series Application Manual (54 pages)

Industrial Applications

Brand: Infineon

|

Category: Microcontrollers

|

Size: 1 MB

Table of Contents

-

-

Introduction16

-

-

-

Introduction28

-

Flash Clock31

-

Trap Control34

-

Advertisement

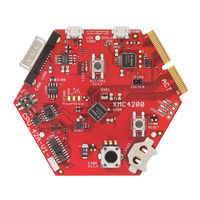

Infineon XMC4000 series Board User's Manual (35 pages)

Hexagon Application Kit, CPU Board

Brand: Infineon

|

Category: Microcontrollers

|

Size: 1 MB

Table of Contents

-

-

Reset12

-

Boot Option13

-

Sdram20

-

Usb20

-

Rtc22

Infineon XMC4000 series Device Manual (38 pages)

For Industrial Applications

Brand: Infineon

|

Category: Microcontrollers

|

Size: 1 MB

Table of Contents

Infineon XMC4000 series User Manual (30 pages)

Brand: Infineon

|

Category: Motherboard

|

Size: 4 MB

Table of Contents

-

Power Supply11

-

Reset17

-

Ethernet18

-

Boot Option19

-

Schematics19

Infineon XMC4000 series Board User's Manual (28 pages)

Brand: Infineon

|

Category: Motherboard

|

Size: 5 MB

Table of Contents

-

-

Power Supply11

-

Reset17

-

Boot Option18

-

-

Schematics18

-

Infineon XMC4000 series User Manual (17 pages)

POSIF in Triple-Hall Mode, Triple-Hall Commutation Control for BLDC Motors

Brand: Infineon

|

Category: Microcontrollers

|

Size: 2 MB

Table of Contents

-

-

-

-

Timer Setup14

Infineon XMC4000 series User Manual (14 pages)

CCU8 and Output State Override, Output State Override on External Events

Brand: Infineon

|

Category: Microcontrollers

|

Size: 0 MB

Table of Contents

Infineon XMC4000 series User Manual (14 pages)

CCU8 and Cross Interconnections Top-Level Interconnect Control

Brand: Infineon

|

Category: Microcontrollers

|

Size: 0 MB

Table of Contents

Infineon XMC4000 series User Manual (11 pages)

CCU8 and Capture Mode Features

Brand: Infineon

|

Category: Microcontrollers

|

Size: 0 MB

Table of Contents

Infineon XMC4000 series Application Manual (10 pages)

For Industrial Applications

Brand: Infineon

|

Category: Microcontrollers

|

Size: 0 MB