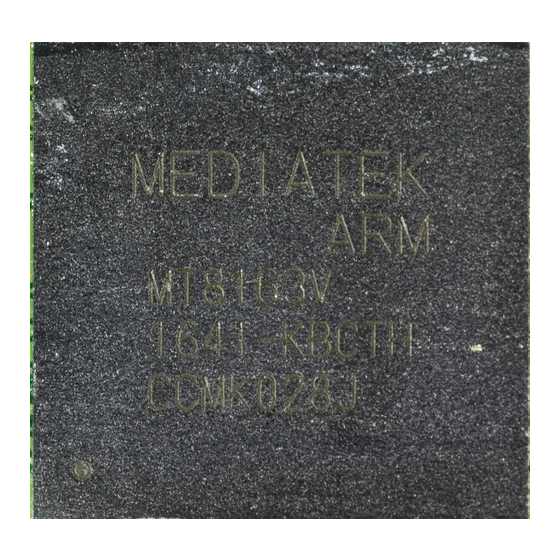

ARM Cortex-A53 MPCore Manuals

Manuals and User Guides for ARM Cortex-A53 MPCore. We have 1 ARM Cortex-A53 MPCore manual available for free PDF download: Technical Reference Manual

Advertisement

Advertisement