Table of Contents

Advertisement

Quick Links

1.0

INTRODUCTION

This document provides a hardware design checklist for the Microchip VSC8211 product family. It is meant to help cus-

tomers achieve first-pass design success. These checklist items should be followed when utilizing the VSC8211 in a

new design. A summary of these items is provided in

on these subjects can be found in the corresponding sections:

•

Section 2.0, "General Considerations"

•

Section 3.0, "Power"

•

Section 4.0, "Twisted Pair Media Interface (CAT5)"

•

Section 5.0, "SGMII/SerDes MAC Interface"

•

Section 6.0, "Parallel MAC Interface"

•

Section 7.0, "Device Clocks"

•

Section 8.0, "Hardware Configuration Using CMODE Pins"

•

Section 9.0, "Digital Interface"

•

Section 10.0, "Miscellaneous"

2.0

GENERAL CONSIDERATIONS

2.1

Required References

The VSC8211 implementor should have the following documents on hand:

• VSC8211 Single-Port 10/100/1000BASE-T, 1000BASE-X, and 100BASE-FX PHY Data Sheet

• Device documents on the VSC8211 product page at

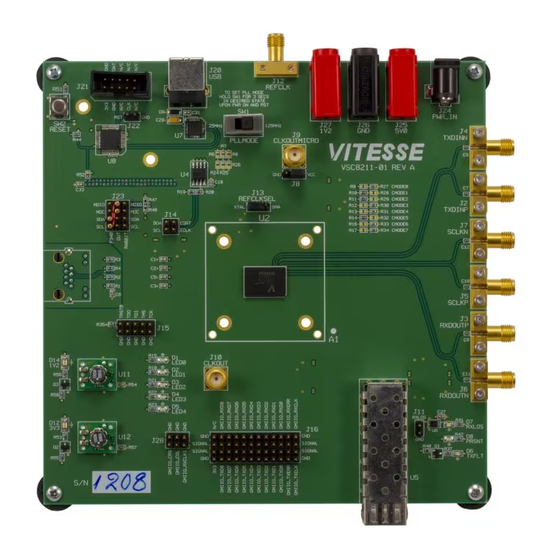

• VSC8211EV EVB schematics and PCB information in the VSC8211 Evaluation Board User Guide as well as

VSC8211 PCB design and layout guidelines at www.microchip.com.

2.2

Pin Check

• Check the pinout of the part against the data sheet. Ensure that all pins match the data sheet and are configured

as inputs, outputs, or bidirectional for error checking.

2.3

Ground

• A single ground reference as a system ground is used for all ground pins. Use one continuous ground plane to

ensure a low-impedance ground path and a continuous ground reference for all signals.

• A chassis ground is necessary between the magnetics and RJ45 connector at line side for better EMI and ESD.

2022 Microchip Technology Inc. and its subsidiaries

Hardware Design Checklist

Section 11.0, "Hardware Checklist

www.microchip.com

VSC8211

Summary". Detailed information

DS00004531A-page 1

Advertisement

Table of Contents

Summary of Contents for Microchip Technology VSC8211

- Page 1 Hardware Design Checklist INTRODUCTION This document provides a hardware design checklist for the Microchip VSC8211 product family. It is meant to help cus- tomers achieve first-pass design success. These checklist items should be followed when utilizing the VSC8211 in a new design.

- Page 2 VSC8211 POWER Table 3-1 shows the power supply pins for the VSC8211. TABLE 3-1: POWER SUPPLY PINS 117 LBGA Voltage Pin Name Descriptions Associated Functional Pins Ball Digital I/O Power Pins VDDIOMAC C6, C3, D3 3.3V or Power for the parallel RXLOS/SIGDET, RXD7:0], RXDV, RXER, 2.5V...

-

Page 3: Current And Power Requirements

VDDIO at 3.3 V, RGMII-CAT5, 10BASE-T, FD, 1518 Byte Random Data Packet, 100% Utilization, SFP Mode Off VDD33A VDDIOMAC, VDDIOMICRO, VDDIOCTRL VDD12 VDD12A VDDIO at 2.5 V, RGMII-CAT5, 10BASE-T, FD, 1518 Byte Random Data Packet, 100% Utilization, SFP Mode Off VDD33A VDDIOMAC, VDDIOMICRO, VDDIOCTRL 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 3... - Page 4 VDDIO at 2.5 V, SerDes-CAT5, 1000BASE-T, FD, 1518 Byte Random Data Packet, 100% Utilization, SFP Mode Off VDD33A VDDIOMAC, VDDIOMICRO, VDDIOCTRL VDD12 VDD12A VDDIO at 3.3 V, SerDes-CAT5, 1000BASE-T, FD, 1518 Byte Random Data Packet, 100% Utilization, SFP Mode On VDD33A VDDIOMAC, VDDIOMICRO, VDDIOCTRL VDD12 VDD12A DS00004531A-page 4 2022 Microchip Technology Inc.and its subsidiaries...

- Page 5 Power Supply Planes • The VSC8211 requires two power rails of 3.3V and 1.2V or three power rails of VDDIO 2.5V, 3.3V, and 1.2V. The fil- tered analog 1.2V and 3.3V supplies should not be shorted to any other digital supply at the package or PCB level.

- Page 6 • Make sure that enough bulk capacitors (1 µF to 22 µF) are incorporated in each power rail of the power supply. • If the VSC8211 device is on the top layer of the printed circuit board (PCB), the best location for local decoupling capacitors is on the bottom or underside of the PCB, directly under the device.

- Page 7 TWISTED PAIR MEDIA INTERFACE (CAT5) 10/100/1000 Mbps Interface Connection The VSC8211 has one GPHY that supports 10/100/1000Base-T Ethernet Gigabit port. Details on the pin numbers for this GPHY are described as follows: • TXVNA (J12): This pin is the transmit/receive negative connection from Pair A of the internal GPHY. This pin con- nects to the 10/100/1000 magnetics.

- Page 8 Chassis GND 10/100/1000 Magnetics and RJ45 Connector Connection • The center tap connection on the VSC8211 side for Pair A channel only connects a 0.1 µF capacitor to GND. No bias is needed. • The center tap connection on the VSC8211 side for Pair B channel only connects a 0.1 µF capacitor to GND. No bias is needed.

-

Page 9: Pcb Layout Considerations

For best performance, short the grounds together with a ferrite bead or a capacitor. Users are required to place the capacitor or ferrite bead far away from the VSC8211 device or other sensitive devices in the PCB layout placement for better ESD. - Page 10 VSC8211 SGMII/SERDES MAC INTERFACE SGMII/SerDes MAC Pins and Connection • The VSC8211 device supports one SGMII (Serial Gigabit Media Independent Interface) MAC or one SerDes MACs. • Refer to Table 5-1 for pin number details. For SGMII/SerDes interface connections, see...

- Page 11 VSC8211 SerDes MAC Interface to SFP • When connected to a SerDes MAC-compliant to 1000BASE-X, the VSC8211 device provides data throughput at a rate of 1000 Mbps only. 10 Mbps and 100 Mbps rates are not supported. • For additional pin in SerDes MAC interface to SFP fiber transceiver module, see Table 5-2.

- Page 12 • Guard vias should be placed no greater than one-quarter wavelength apart around the differential pair tracks. • If the SGMII/SerDes port is unused, both the RDx pair and TDx pair pins can be left floating (no-connect). DS00004531A-page 12 2022 Microchip Technology Inc.and its subsidiaries...

- Page 13 VSC8211 PARALLEL MAC INTERFACE The VSC8211 parallel MAC interface supports GMII, RGMII, MII as well as TBI and RTBI interfaces. For detailed GMII/ RGMII/MII pin descriptions and system design connections, refer to Section 6.1, "GMII/RGMII/MII Interface Pins". For detailed TBI/RTBI pin descriptions and system design connections, refer to Section 6.2, "TBI/RTBI Interface...

- Page 14 6.1.1 GMII INTERFACE • The VSC8211 GMII interface supports 1000 Mbps only. GMII is used as an interface to a GMII-compatible MAC. The devices are compliant with the GMII interface specification when VDDIOMAC is operating at 3.3 V. The devices can also support the GMII interface at 2.5V.

- Page 15 50Ω RXER RXER • VSC8211 GMII drive pins do not require external series termination resistors because they include internal 50Ω series termination resistors. • Other-end GMII interface drive pins need external series termination resistor R if there are not enough internal 50Ω...

- Page 16 1000 Mbps. The RGMII interface contains two distinct groups of signals—one for transmission and one for receiv- ing. • The VSC8211 device supports RGMII that is used as an interface to an RGMII-compatible MAC. The devices are compliant with the RGMII interface specification 2.0. The devices can also support the RGMII interface at 3.3V or 2.5 V.

- Page 17 TIMING CONSIDERATIONS FOR DESIGN WITH RGMII INTERFACE • The VSC8211 supports RGMII V2.0 specifications. The RGMII interfaces need to meet a minimum of 1.0 ns and a maximum of 2.6 ns of data to input clock delay/skew in RGMII V2.0 specification by setting the Ingress Clock Delay and the Egress Clock Delay.

- Page 18 RGMII V2.0 for both VSC8211 and other-end RGMII data to clock input/output delay/skew. TBI/RTBI Interface Pins The VSC8211 supports TBI and RTBI interfaces. The TBI and RTBI support all three speeds—10 Mbps, 100 Mbps, and 1000 Mbps—and can be used to interface to other end devices with TBI and RTBI interfaces. See...

- Page 19 PHY bit stream. PMARXCLK1 is 180 out-of-phase with PMARX- CLK0. This clock may be stretched during code-group alignment and is not shortened. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 19...

- Page 20 TBI interface specification when VDDIOMAC is operating at 3.3 V. The devices can also support the TBI interface at 2.5 V. • The TBI interface contains two distinct groups of signals—one for transmission and one for receiving. The VSC8211 TBI and GMAC TBI connections are shown in Figure 6-4. Refer to...

- Page 21 The RTBI interface contains two distinct groups of signals—one for transmission and one for receiving. • The VSC8211 device supports RTBI that is used as an interface to a RTBI-compatible MAC. The devices are com- pliant with the RTBI interface specification 2.0. The devices can also support the RTBI interface at 3.3V or 2.5V.

- Page 22 TIMING CONSIDERATIONS FOR DESIGN WITH RTBI INTERFACE • The VSC8211 supports RTBI V2.0 specifications. The RTBI interfaces need to meet the minimum 1.0 ns and max- imum 2.6 ns of data to input clock delay/skew in RGMII/RTBI V2.0 specification. This can be achieved by setting the Ingress Clock Delay and the Egress Clock Delay.

- Page 23 23 bits [11:8] to other values to meet the minimum 1.0 ns and the maximum 2.6 ns specifi- cation in RGMII/RTBI V2.0 for both VSC8211 and other-end RTBI data to clock input/output delay/skew. 2022 Microchip Technology Inc. and its subsidiaries...

- Page 24 Exact resistor values are application-dependent and must be analyzed in-system. • VSC8211 GMII/RGMII/MII and TBI/RTBI drive pins do not need external series termination resistors because they have internal 50Ω series termination resistors. • Other-end GMII/RGMII/MII and TBI/RTBI interface drive pins need external series termination resistor R if there are not enough internal 50Ω...

- Page 25 For more information on this topic, refer to the article titled, Calculating Crystal Load Capacitor at microchip- support.force.com. The PLLMODE pin should be left floating (or pulled low) when using 25 MHz clock frequency. See Figure 7-1 for details. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 25...

- Page 26 OSCDIS pin should have an external pull-down resistor for using an oscillator. FIGURE 7-2: 25 MHZ OSCILLATOR CIRCUIT AND CONFIGURATION <+/-100ppm 25MHz 3.3V VSC8211 Oscillator XTAL1/REFCLK Floating for using 25MHz PLLMODE XTAL2 OSCDIS 4.7KΩ Pull-down for Using oscillator DS00004531A-page 26 2022 Microchip Technology Inc.and its subsidiaries...

- Page 27 The OSCDIS pin should have an external pull-down resistor for using an oscillator. FIGURE 7-3: 125 MHZ OSCILLATOR CIRCUIT AND CONFIGURATION <+/-100ppm 125MHz 3.3V 3.3V VSC8211 Oscillator 4.7KΩ XTAL1/REFCLK PLLMODE Pull-up for using 125MHz XTAL2 OSCDIS 4.7KΩ Pull-down for Using oscillator 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 27...

- Page 28 — 0101 16.9 — 0110 22.6 — 0111 — 1000 — 2.26 1001 — 4.02 1010 — 5.90 1011 — 8.25 1100 — 12.1 1101 — 16.9 1110 — 22.6 1111 DS00004531A-page 28 2022 Microchip Technology Inc.and its subsidiaries...

- Page 29 Flow Control [1:0]: 00: Asymmetric Pause capable link status only. 0: Disabled 01: Symmetric Pause capable 0: All link function blinks 1: Enabled 10:100BASE-TX FDX capable or flashes when activity is 11:100BASE-TX HDX capable present. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 29...

- Page 30 RTBI to CAT5 Media, Clause 37 auto-negotia- tion auto-sense enabled 1101 Serial MAC to Fiber Media, SCLK enabled 1110 802.3z SerDes to CAT5 Media, Clause 37 enabled 1111 SGMII to CAT5 Media, SCLK disabled DS00004531A-page 30 2022 Microchip Technology Inc.and its subsidiaries...

- Page 31 MII Registers 4 and 9. 10/100/1000BASE-T HDX, 10/100/1000BASE- T FDX Auto-Negotiation CMODE3[0], CMODE4[1] 10/100BASE-T HDX, 10/100/1000BASE-T Advertisement Con- trol [1:0]] 10/100BASE-T HDX, 10/100BASE-T FDX 1000BASE-T FDX 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 31...

-

Page 32: Digital Interface

1.5 kΩto 4.7 kΩ pull-up resistor to VDDIOMICRO at the station manager. The value of the pull-up resistor depends on the MODDEF1 frequency and the capacitive load on the MODDEF2 line. DS00004531A-page 32 2022 Microchip Technology Inc.and its subsidiaries... - Page 33 If the MDINT pin is pulled up to VDDIOMICRO using a 4.7 kΩ to 10 kΩ resistor, it becomes an active-low signal. If the MDINT pin is pulled down using a 4.7 kΩ to 10 kΩ resistor, then it becomes an active-high signal. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 33...

-

Page 34: Eeprom Interface

SDA and SCL pins, respectively, of a serial EEPROM that is compatible with the AT24 series of Microchip EEPROMs. The EEPROM interface on the VSC8211 serves the following purposes: - It provides the PHY with the ability to configure its self-internal registers. -

Page 35: Jtag Interface

TRST pin is floating. If the JTAG port of the PHY is not used on the printed circuit board, then this pin should be pulled down with a 2 kΩpull-down resistor to ground. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 35... - Page 36 Reset • The VSC8211 must be reset at power-up. One option is to hold RESET low for a minimum 2 ms after all power rails are up, control pins are stable, and clocks are active. Another option is to pulse RESET low for a minimum of 2 ms after power-up.

- Page 37 The PHY drives a 125 MHz clock output after the PHY startup sequence has completed. This clock can be disabled by clearing MII Register 18.0. The voltage levels of this clock are determined by the VDDIO power supply. 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 37...

- Page 38 • If no pull-up resistor value is specified, it is recommended to use a 4.7 kΩ resistor. • If no pull-down resistor value is specified, it is recommended to use a 1 kΩ or 4.7 kΩ resistor. DS00004531A-page 38 2022 Microchip Technology Inc.and its subsidiaries...

- Page 39 VSC8211 NOTES: 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 39...

- Page 40 11.0 HARDWARE CHECKLIST SUMMARY TABLE 11-1: HARDWARE DESIGN CHECKLIST Section √ Check Explanation Notes Section 2.0, "General Con- Section 2.1, "Required References" All necessary documents are on hand. siderations" Section 2.2, "Pin Check" The pins match the data sheet. Section 2.3, "Ground" Verify if the digital ground and the analog ground are tied together.

- Page 41 GMII/RGMII/MII interfaces in the design. Section 6.1.1, "GMII Interface" Read this section and refer to Figure 6-1 for the correct GMII connection between VSC8211 and other-end MAC GMII inter- face. Section 6.1.2, "MII Interface" Read this section and refer to Figure 6-2 for the correct MII con- nection between VSC8211 and other-end MAC MII interface.

- Page 42 TABLE 11-1: HARDWARE DESIGN CHECKLIST (CONTINUED) √ Section Check Explanation Notes Section 7.0, "Device Clocks" Section 7.1, "Reference Clock" Refer to Table 7-1 to select the reference clock circuit-related pins in the design. Section 7.2, "25 MHz Crystal Circuit" Refer to Figure 7-1 for 25 MHz crystal clock circuit design and make sure to use the correct strapping for PLLMODE pin and...

- Page 43 TABLE 11-1: HARDWARE DESIGN CHECKLIST (CONTINUED) √ Section Check Explanation Notes Section 10.1, "Reset" Section 10.0, "Miscella- Refer to Table 10-1 for using the correct RESET pin and see if neous" the designed Reset circuit meets the Reset time requirement. Section 10.2, "LED Pins"...

-

Page 44: Revision History

APPENDIX A: REVISION HISTORY TABLE A-1: REVISION HISTORY Revision Level & Date Section/Figure/Entry Correction DS00004531A Initial release (05-05-22) DS00004531A-page 44 2022 Microchip Technology Inc. and its subsidiaries... - Page 45 VSC8211 NOTES: 2022 Microchip Technology Inc. and its subsidiaries DS00004531A-page 45...

-

Page 46: The Microchip Web Site

A listing of sales offices and locations is included in the back of this document. Technical support is available through the web site at: http://microchip.com/support DS00004531A-page 46 2022 Microchip Technology Inc. and its subsidiaries... - Page 47 The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries. GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

-

Page 48: Worldwide Sales And Service

Tel: 46-31-704-60-40 Tel: 631-435-6000 Sweden - Stockholm San Jose, CA Tel: 46-8-5090-4654 Tel: 408-735-9110 UK - Wokingham Tel: 408-436-4270 Tel: 44-118-921-5800 Canada - Toronto Fax: 44-118-921-5820 Tel: 905-695-1980 Fax: 905-695-2078 DS00004531A-page 48 2022 Microchip Technology Inc. and its subsidiaries 09/14/21...

Need help?

Do you have a question about the VSC8211 and is the answer not in the manual?

Questions and answers