ARTERY AT32F435 Series Start Manual

Hide thumbs

Also See for AT32F435 Series:

- Get started manual (25 pages) ,

- Reference manual (708 pages) ,

- Reference manual (714 pages)

Table of Contents

Advertisement

Quick Links

Introduction

This application note mainly introduces:

1. How to configure and modify the clock source code based on the BSP_ V2.x.x provided by Artery.

2. How to use the accessary clock configuration tools to set clock path and parameters to generate

and use the corresponding clock code.

Applicable products:

Part number

2022.12.23

AT32F435/437 CRM Start Guide

AT32F435/437 CRM Start Guide

AT32F435xx

AT32F437xx

1

AN0084

Application Note

Ver 2.0.4

Advertisement

Table of Contents

Summary of Contents for ARTERY AT32F435 Series

- Page 1 This application note mainly introduces: 1. How to configure and modify the clock source code based on the BSP_ V2.x.x provided by Artery. 2. How to use the accessary clock configuration tools to set clock path and parameters to generate and use the corresponding clock code.

-

Page 2: Table Of Contents

AT32F435/437 CRM Start Guide Contents Overview ......................... 6 Clock tree........................ 7 Code configuration and parsing ................8 Functions ........................8 Clock configuration ....................9 3.2.1 CRM Reset ........................9 3.2.2 Set Flash clock division ....................9 3.2.3 Clock source configuration ................... 9 3.2.4 PLL configuration ....................... - Page 3 AT32F435/437 CRM Start Guide Resources ......................20 Software design ...................... 20 Test result ....................... 22 Application case 2: Clock fail detector .............. 23 Introduction......................23 Resources ......................23 Software design ...................... 23 Test result ....................... 25 Application case 3: Calculation of PLL parameters ......... 26 Introduction......................

- Page 4 AT32F435/437 CRM Start Guide List of tables Table 1. Document revision history ....................28 2022.12.23 Ver 2.0.4...

- Page 5 AT32F435/437 CRM Start Guide List of figures Figure 1. Block diagram of clock ......................7 Figure 2. Clock configuration process ....................9 Figure 3. Startup interface ......................... 14 Figure 4. Configuration interface ....................... 15 Figure 5. Menu bar ..........................15 Figure 6.

-

Page 6: Overview

As the necessary condition for the correct and efficient running of chips, proper clock configuration is of great importance. The clock configuration of each AT32 series MCU may be slight different. This application note mainly introduces how to use BSP_V2.x.x provided by Artery to perform clock configuration of the corresponding AT32 MCU series. -

Page 7: Clock Tree

AT32F435/437 CRM Start Guide Clock tree Before configuring the clock, it is necessary to have a comprehensive understanding of the clock tree, with focuses on the clock source, frequency multiplication and system clock. Figure 1. Block diagram of clock Peripheral 12S1/2/3/4 CLK clock enable HEXT... -

Page 8: Code Configuration And Parsing

AT32F435/437 CRM Start Guide Code configuration and parsing This section introduces how to use library function interface to configure the clock. Functions The interface functions for hardware clock configuration in BSP of the corresponding MCU series are encapsulated and can be called. Functions commonly used for clock configuration are listed below. -

Page 9: Clock Configuration

AT32F435/437 CRM Start Guide Clock configuration Figure 2 shows the clock configuration process. Figure 2. Clock configuration process CRM Reset Set Flash Clock Division Clock Source Enable PLL Configuration Set Bus Frequency Division Switch System Clock Update Core Frequency 3.2.1 CRM Reset According to the configuration process, perform CRM reset firstly, which switches system clock to HICK, and write the default value to other system clock configuration registers. -

Page 10: Pll Configuration

AT32F435/437 CRM Start Guide Enable HEXT clock source and wait until HEXT clock becomes stable. The implementation code is as follows: crm_clock_source_enable(CRM_CLOCK_SOURCE_HEXT, TRUE); /* Enable HEXT clock source */ while(crm_hext_stable_wait() == ERROR) /* Wait until HEXT clock becomes stable */ ... -

Page 11: Set Bus Frequency Division

AT32F435/437 CRM Start Guide while(crm_flag_get(CRM_PLL_STABLE_FLAG) != SET) /* Wait until PLL stable flag is set 3.2.5 Set bus frequency division The bus frequnency division configuration includes SCLK to AHBCLK, AHBCLK to APB1CLK and AHBCLK to APB2CLK. The implementation code of AHB bus (divided by 1), APB1/APB2 bus (divided by 2) frequency division is as follow: crm_ahb_div_set(CRM_AHB_DIV_1);... -

Page 12: Update Core Frequency

AT32F435/437 CRM Start Guide HEXT When the HEXT is used as system clock source, the system clock frequency depends on the actual external clock frequency (range: 4~25 MHz). The implementation code of setting HEXT as system clock source is as follows: crm_sysclk_switch(CRM_SCLK_HEXT);... - Page 13 AT32F435/437 CRM Start Guide crm_pll_config(CRM_PLL_SOURCE_HEXT, 144, 1, CRM_PLL_FR_4); /* Configure PLL: The HEXT is used as PLL clock source; set multiplication parameters as follows: PLL_MS = 1, PLL_NS = 144 and PLL_FR = 4; PLLCLK = 8 / 1 * 144 / 4 = 288 MHz */ crm_clock_source_enable(CRM_CLOCK_SOURCE_PLL, TRUE);...

-

Page 14: Clock Configuration Tools

AT32F435/437 CRM Start Guide Clock configuration tools The New Clock Configuration is a graphical configuration tool developed by Artery for configuring the clock of AT32 series MCUs, to help users have a better understanding of the clock path, configure the required frequency and generate source files. -

Page 15: Menu Bar

AT32F435/437 CRM Start Guide Figure 4. Configuration interface Menu bar The menu bar is shown below. Figure 5. Menu bar Project Create a new configuration project Open Open an existing configuration project Save Saved the current configuration project Language English Select English as the display language... -

Page 16: Clock Configuration Interface

Users can configure the clock path and parameter and display the current clock frequency in the clock configuration interface. Figure 7 shows the clock configuration for AT32F435 series MCU. The clock configuration interface mainly contains four blocks, as shown below. -

Page 17: Figure 8. Clock Configuration Block

AT32F435/437 CRM Start Guide Figure 8 illustrates the clock configuration block. The configuration process corresponds to MCU clock tree, which may be slightly different for different MCU series. The clock path can be configured by clicking on each checkbox according to the configuration process, as shown below. Figure 8. -

Page 18: Generate Code

AT32F435/437 CRM Start Guide 14. usbdiv: drop-down box, which is used to configure the division factor of PLL to USB when PLL clock is selected as the USB clock source. 15. hick to usb: checkbox, which is used to configure USB clocked by PLL clock or HICK 48 MHz. The USB clock configuration code is controlled by the “to usb”... -

Page 19: Notes

Notes on using the New Clock Configuration tool: The clock configuration source file generated by the New Clock Configuration tool should be used together with BSP_V2.x.x provided by Artery. The clock configuration source file generated for the specific MCU series should be used in the corresponding project only. -

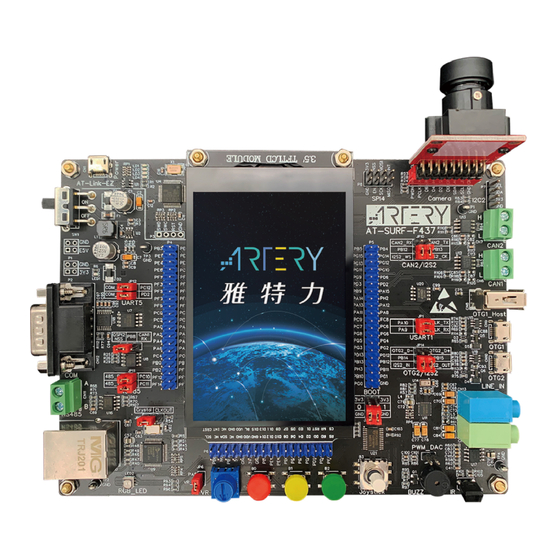

Page 20: Application Case 1: Switch System Clock

AT32F435/437 CRM Start Guide Application case 1: Switch system clock Introduction Switch the system clock when the system is running. Resources Hardware AT-START BOARD of the corresponding MCU series Software project\at_start_f435\examples\crm\sysclk_switch Software design Configuration process Initialize buttons; Configure PLL/4 to be output to CLKOUT; ... - Page 21 AT32F435/437 CRM Start Guide pwc_ldo_output_voltage_set(PWC_LDO_OUTPUT_1V3); /* Set LDO=1.3V */ flash_clock_divider_set(FLASH_CLOCK_DIV_2); /* Set division factor to be 2 when system clock ≤ 240 MHz */ crm_clock_source_enable(CRM_CLOCK_SOURCE_HICK, TRUE); /* Enable HICK clock source */ while(crm_flag_get(CRM_HICK_STABLE_FLAG) != SET) /* Wait until HICK stable flag is set */ crm_pll_config(CRM_PLL_SOURCE_HICK, 64, 1, CRM_PLL_FR_8);...

-

Page 22: Test Result

AT32F435/437 CRM Start Guide crm_clock_source_enable(CRM_CLOCK_SOURCE_HEXT, TRUE); /* Enable HEXT clock source */ while(crm_hext_stable_wait() == ERROR) /* Wait until HEXT clock becomes stable */ crm_pll_config(CRM_PLL_SOURCE_HEXT, 96, 1, CRM_PLL_FR_8); /* Configure PLL: HEXT is selected as the PLL clock source; set multiplication parameters as below: PLL_MS = 1, PLL_NS = 96 and PLL_FR = 8;... -

Page 23: Application Case 2: Clock Fail Detector

AT32F435/437 CRM Start Guide Application case 2: Clock fail detector Introduction The clock fail detector is designed to respond to HEXT clock failure when the HEXT is used as the system clock, directly or indirectly. If a failure is detected on the HEXT clock, a NMI interrupt is generated so that the software can perform rescue operations. - Page 24 AT32F435/437 CRM Start Guide set */ crm_pll_config(CRM_PLL_SOURCE_HICK, 144, 1, CRM_PLL_FR_4); /* Configure PLL: HICK is selected as PLL clock source; set multiplication parameters as below: PLL_MS = 1, PLL_NS = 144 and PLL_FR = 4; PLLCLK = 8 / 1 * 144 / 4 = 288 MHz */ crm_clock_source_enable(CRM_CLOCK_SOURCE_PLL, TRUE);...

-

Page 25: Test Result

AT32F435/437 CRM Start Guide crm_flag_clear(CRM_CLOCK_FAILURE_INT_FLAG); /* Clear clock failure flag */ Test result Unplug or ground the crystal oscillator when the system is running, and a clock failure is generated; generally, HEXT is more stable then HICK. Observe and check the CLKOUT (PA8) output, and slight frequency fluctuation can be found after rescue operations when HICK is used as the system clock source. -

Page 26: Application Case 3: Calculation Of Pll Parameters

AT32F435/437 CRM Start Guide Application case 3: Calculation of PLL parameters Introduction When configuring the system clock, call the library functions to calculate a set of PLL parameters automatically according to the PLL reference clock source and the target clock frequency. Resources Hardware AT-START BOARD of the corresponding MCU series... -

Page 27: Test Result

AT32F435/437 CRM Start Guide void system_clock_config_200mhz(void) uint16_t pll_ns, pll_ms, pll_fr; crm_reset(); /* CRM reset */ crm_periph_clock_enable(CRM_PWC_PERIPH_CLOCK, TRUE); pwc_ldo_output_voltage_set(PWC_LDO_OUTPUT_1V3); /* Set LDO=1.3V */ flash_clock_divider_set(FLASH_CLOCK_DIV_3); /* Set flash clock divided by 3 */ crm_clock_source_enable(CRM_CLOCK_SOURCE_HEXT, TRUE); /* Enable HEXT clock source */ while(crm_hext_stable_wait() == ERROR) /* Wait until HEXT becomes stable */ calculate_status = crm_pll_parameter_calculate(CRM_PLL_SOURCE_HEXT, 200000000, &pll_ms,... -

Page 28: Revision History

AT32F435/437 CRM Start Guide Revision history Table 1. Document revision history Date Version Revision note 2021.8.18 2.0.0 Initial release. 2021.11.24 2.0.1 Updated the screenshot of New Clock Configuration tool. Updated the screenshot of New Clock Configuration tool and description of 2022.06.09 2.0.2 operation procedures. - Page 29 No license, express or implied, to any intellectual property rights is granted under this document. If any part of this document deals with any third party products or services, it shall not be deemed a license grant by ARTERY for the use of such third party products or services, or any intellectual property contained therein, or considered as a warranty regarding the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

Need help?

Do you have a question about the AT32F435 Series and is the answer not in the manual?

Questions and answers