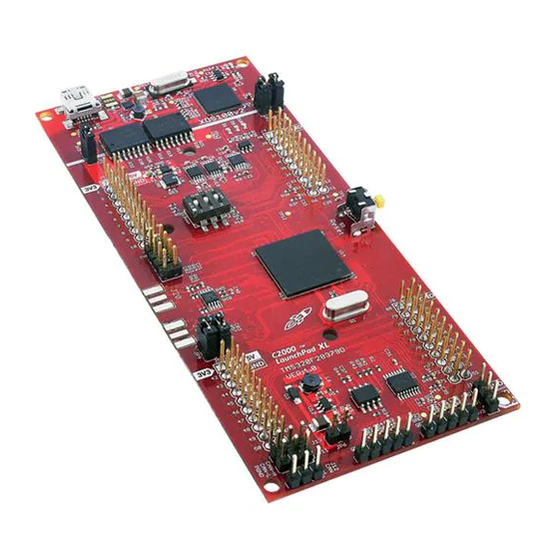

Texas Instruments Delfino TMS320F2837 S Series Manual

Hide thumbs

Also See for Delfino TMS320F2837 S Series:

- Workshop manual and lab manual (324 pages) ,

- Errata sheet (48 pages) ,

- Manual (52 pages)

Advertisement

Quick Links

1 Device Overview

1.1

Features

1

• TMS320C28x 32-Bit CPU

– 200 MHz

– IEEE 754 Single-Precision Floating-Point

– Trigonometric Math Unit (TMU)

– Viterbi/Complex Math Unit (VCU-II)

• Programmable Control Law Accelerator (CLA)

– 200 MHz

– IEEE 754 Single-Precision Floating-Point

Executes Code Independently of Main CPU

• On-Chip Memory

– 512KB or 1MB of Flash (ECC-Protected)

– 132KB or 164KB of RAM (ECC or Parity)

– Dual-Zone Security Supporting Third-Party

Development

• Clock and System Control

– Two Internal Zero-Pin 10-MHz Oscillators

– On-Chip Crystal Oscillator and External Clock

Input

– Windowed Watchdog Timer Module

– Missing Clock Detection Circuitry

• 1.2-V Core, 3.3-V I/O Design

• System Peripherals

– Two External Memory Interfaces (EMIFs) With

ASRAM and SDRAM Support

– 6-Channel Direct Memory Access (DMA)

Controller

– Up to 169 Individually Programmable,

Multiplexed General-Purpose Input/Output

(GPIO) Pins With Input Filtering

– Hardware (HW) Interrupt Controller

– Multiple Low-Power Mode Support With External

Wakeup

– JTAG Emulation Connection

• Communications Peripherals

– USB 2.0 (MAC + PHY)

– Support for 12-Pin 3.3 V-Compatible Universal

Parallel Port (uPP) Interface

– Two Controller Area Network, D_CAN, Modules

(Pin-Bootable)

– Three High-Speed (40-MHz) SPI Ports

(Pin-Bootable)

– Two Multichannel Buffered Serial Ports

(McBSPs)

– Up to Four Serial Communications Interfaces

(SCIs) (Pin-Bootable)

2

– Two I

C Interfaces (Pin-Bootable)

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. ADVANCE INFORMATION for pre-production products; subject to

change without notice.

Sample &

Product

Buy

Folder

TMS320F28377S, TMS320F28376S, TMS320F28375S, TMS320F28374S

TMS320F2837xS Delfino™ Microcontrollers

Tools &

Technical

Documents

Software

SPRS881A – AUGUST 2014 – REVISED JUNE 2015

• Analog Subsystem

– Up to Four Dual-Mode Analog-to-Digital

Converters (ADCs)

•

16-Bit Mode

– 1.1 MSPS Each (up to 4.4-MSPS

System)

– Differential

– Up to 12 External Channels

•

12-Bit Mode

– 3.5 MSPS Each (up to 14-MSPS System)

– Single-Ended

– Up to 24 External Channels

•

Single Sample-and-Hold (S/H) on Each ADC

•

HW Integrated Post-Processing of ADC

Conversions

– Saturating Offset Calibration

– Error From Setpoint Calculation

– High, Low, and Zero-Crossing Compare,

With Interrupt Capability

– Trigger-to-Sample Delay Capture

– Eight Windowed Comparators With 12-Bit

Digital-to-Analog Converter (DAC) References

– Three 12-Bit Buffered DAC Outputs

• Enhanced Control Peripherals

– Up to 24 PWM Channels With Enhanced

Features

– Up to 16 High-Resolution Pulse Width

Modulator (HRPWM) Channels

•

High Resolution on Both A and B Channels

of 8 PWM Modules

•

Dead-Band Support (on Both Standard and

High Resolution)

– Six Enhanced Capture (eCAP) Modules

– Up to Three Enhanced Quadrature Encoder

Pulse (eQEP) Modules

– Eight Sigma-Delta Filter Module (SDFM) Input

Channels, 2 Parallel Filters per Channel

•

Standard SDFM Data Filtering

•

Comparator Filter for Fast Action for Out of

Range

Support &

Community

Advertisement

Summary of Contents for Texas Instruments Delfino TMS320F2837 S Series

- Page 1 Support & Sample & Product Tools & Technical Community Folder Documents Software TMS320F28377S, TMS320F28376S, TMS320F28375S, TMS320F28374S SPRS881A – AUGUST 2014 – REVISED JUNE 2015 TMS320F2837xS Delfino™ Microcontrollers 1 Device Overview Features • TMS320C28x 32-Bit CPU • Analog Subsystem – 200 MHz –...

- Page 2 Smart Metering • Solar Micro Inverters and Converters • Automotive Transportation • Radar • Power Line Communications • Digital Power • Software-Defined Radio Device Overview Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 3 HTQFP (100) 14.0 mm × 14.0 mm (1) For more information on these devices, see Section 8, Mechanical Packaging and Orderable Information. Device Overview Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 4 SD-1/2 McBSP-A/B 1/../6 (16L FIFO) HRPWM-1/../8 (32-mbox) (16L FIFO) (16L FIFO) GPIO MUX, Input X-BAR, Output X-BAR Figure 1-1. Functional Block Diagram Device Overview Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 5 Mechanical Packaging and Orderable Power Consumption Summary ..........Information ....Thermal Resistance Characteristics ................Packaging Information System ........Analog Peripherals Table of Contents Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 6 • Section 5.3: Added "Operation above T = 105°C for extended duration will reduce the lifetime of the device ..." ..........................footnote. Revision History Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 7 (Analog Subsystem Block Diagram (100-Pin PZP)): Updated figure. • Section 5.8.1 (Analog-to-Digital Converter (ADC)): Updated "The ADCs on this device are successive ................approximation (SAR) style ADCs ..." paragraph. Revision History Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 8 16". Changed END ADDRESS from "0x9FFF FFFF" to "0x93FF FFFF". • Table 6-5 (Peripheral Registers Memory Map): STRUCTURE NAME column: Changed "CPU_TIMER_REGS" to ......................"CPUTIMER_REGS". Revision History Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 9 (Getting Started and Next Steps): Added section. • Section 7.2 (Documentation Support): Added the Calculating Useful Lifetimes of Embedded Processors ....................Application Report (SPRABX4). Revision History Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 10 Number of 16-bit or 12-bit ADCs – Number of 12-bit only ADCs – Temperature sensor CMPSS (each CMPSS has two Comparators and two internal DACs) Buffered DAC Device Comparison Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 11 (4) The CAN module uses the popular IP known as D_CAN. This document uses the names “CAN” and “D_CAN” interchangeably to reference this peripheral. (5) "Q" refers to Q100 qualification for automotive applications. Device Comparison Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 12 Figure 4-1. 337-Ball ZWT New Fine Pitch Ball Grid Array (Bottom View) – [Quadrant A] Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 13 Figure 4-2. 337-Ball ZWT New Fine Pitch Ball Grid Array (Bottom View) – [Quadrant B] Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 14 Figure 4-3. 337-Ball ZWT New Fine Pitch Ball Grid Array (Bottom View) – [Quadrant C] Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 15 Figure 4-4. 337-Ball ZWT New Fine Pitch Ball Grid Array (Bottom View) – [Quadrant D] Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 16 Table 4-1 for the complete, muxed signal name. Figure 4-5. 176-Pin PTP PowerPAD Thermally Enhanced Low-Profile Quad Flatpack (Top View) Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 17 EDA CAD/CAE design tools. See the “CAD/CAE symbols” section in each device’s product folder, under the Packaging section. These can also be searched for at http://webench.ti.com/cad/. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 18 ADC-A input 1. There is a 50-kΩ internal pulldown on this pin in both an ADC input or DAC output mode which cannot be disabled. DACOUTB DAC-B output Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 19 ADC-D input 3 – CMPIN8N Comparator 8 negative input ADCIND4 – ADC-D input 4 ADCIND5 – – ADC-D input 5 Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 20 Enhanced PWM5 output A and HRPWM channel CANTXB CAN-B transmit – ADCSOCAO ADC start-of-conversion A EQEP3S Enhanced QEP3 strobe SCITXDA SCI-A transmit data Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 21 SCI-B transmit data MCLKXB McBSP-B transmit clock OUTPUTXBAR3 Output 3 of the output XBAR UPP-D6 Universal parallel port data line 6 Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 22 CAN-B transmit EPWM11A Enhanced PWM11 output A SD1_D3 Sigma-Delta 1 channel 3 data input UPP-D0 Universal parallel port data line 0 Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 23 McBSP-B transmit clock OUTPUTXBAR3 Output 3 of the output XBAR SPICLKB SPI-B clock SD2_D2 Sigma-Delta 2 channel 2 data input Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 24 SCIRXDA SCI-A receive data – EM1CS3 External memory interface 1 chip select 3 SCLB I/OD I2C-B clock open-drain bidirectional port Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 25 0, 4, 8, 12 General-purpose input/output 47 EM1A7 – External memory interface 1 address line 7 SCITXDD SCI-D transmit data Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 26 External memory interface 2 data line 13 EQEP2B Enhanced QEP2 input B SCIRXDB SCI-B receive data SD1_C4 Sigma-Delta 1 channel 4 clock input Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 27 Output 3 of the output XBAR SPISIMOB SPI-B slave in, master out SD2_D3 Sigma-Delta 2 channel 3 data input SPICLKA SPI-A clock Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 28 General-purpose input/output 67 EM1D17 – External memory interface 1 data line 17 EM2D1 External memory interface 2 data line 1 Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 29 0, 4, 8, 12 General-purpose input/output 78 EM1D6 External memory interface 1 data line 6 EQEP2A Enhanced QEP2 input A Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 30 External memory interface 1 address line 17 EM1DQM2 External memory interface 1 Input/output mask for byte 2 SCIRXDC SCI-C receive data Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 31 General-purpose input/output 103 EM2A5 External memory interface 2 address line 5 – – EQEP2I Enhanced QEP2 index SPISTEC SPI-C slave transmit enable Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 32 0, 4, 8, 12 General-purpose input/output 120 EM2WE – – External memory interface 2 write enable USB0PFLT USB external regulator power fault indicator Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 33 0, 4, 8, 12 General-purpose input/output 136 SCIRXDA – – SCI-A receive data SD2_D4 Sigma-Delta 2 channel 4 data input Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 34 Enhanced PWM7 output B and HRPWM channel GPIO159 0, 4, 8, 12 General-purpose input/output 159 – – EPWM8A Enhanced PWM8 output A and HRPWM channel Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 35 EPWM12A Enhanced PWM12 output A GPIO168 0, 4, 8, 12 General-purpose input/output 168 – – EPWM12B Enhanced PWM12 output B Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 36 This pin has an internal 50-ns (nominal) glitch filter. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 37 – – 3.3-V analog power pins. Place a minimum 2.2-µF decoupling capacitor on each pin. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 38 Power pins for the 3.3-V on-chip crystal oscillator (X1 and X2) and the two zero-pin internal oscillators DDOSC (INTOSC). Place a 0.1-μF (minimum) decoupling capacitor on each pin. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 39 Analog and digital ground. For Quad Flatpacks (QFPs), the PowerPAD on the bottom of the package must be soldered to the ground plane of the PCB. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 40 On the PZP package, pin 17 is double-bonded to V and V . This pin must be connect to V REFLOA – – – – Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 41 DDIO (2) Pins not bonded out in a given package will have the internal pullups enabled by the Boot ROM. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 42 (1) I = Input, O = Output, OD = Open Drain (2) GPIO Index settings of 9, 10, 11, 13, and 14 are reserved. Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 43 (3) High-Speed SPI-enabled GPIO mux option. This pin mux option is required when using the SPI in High-Speed Mode (HS_MODE = 1 in SPICCR). This mux option is still available when not using the SPI in High-Speed Mode (HS_MODE = 0 in SPICCR). Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 44 SD2_C3 (I) GPIO136 SCIRXDA (I) SD2_D4 (I) GPIO137 SCITXDB (O) SD2_C4 (I) GPIO138 SCIRXDB (I) GPIO139 SCIRXDC (I) GPIO140 SCITXDC (O) Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 45 EPWM9B (O) GPIO163 EPWM10A (O) GPIO164 EPWM10B (O) GPIO165 EPWM11A (O) GPIO166 EPWM11B (O) GPIO167 EPWM12A (O) GPIO168 EPWM12B (O) Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 46 XINT3, EPWM[TRIP6], EXTSYNCIN2, EPWM X-BAR, Output X-BAR INPUT7 ECAP1 INPUT8 ECAP2 INPUT9 ECAP3 INPUT10 ECAP4 INPUT11 ECAP5 INPUT12 ECAP6 INPUT13 XINT4 INPUT14 XINT5 Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 47 INPUT1 INPUT2 INPUT3 INPUT X-Bar INPUT4 INPUT5 INPUT6 FLT1.COMPH FLT1.COMPL FLT4.COMPH FLT4.COMPL FLT1.COMPH FLT1.COMPL FLT4.COMPH FLT4.COMPL Figure 4-8. Output X-BAR Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 48 Table 4-6. Alternate USB Function GPIO GPBAMSEL SETTING USB FUNCTION GPIO42 GPBAMSEL[10] = 1b USB0DM GPIO43 GPBAMSEL[11] = 1b USB0DP Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 49 SPISTEB GPCGMUX1[5:4]=11b GPCMUX1[5:4]=11b SPIC GPIO69 SPISIMOC GPCGMUX1[11:10]=11b GPCMUX1[11:10]=11b GPIO70 SPISOMIC GPCGMUX1[13:12]=11b GPCMUX1[13:12]=11b GPIO71 SPICLKC GPCGMUX1[15:14]=11b GPCMUX1[15:14]=11b GPIO72 SPISTEC GPCGMUX1[17:16]=11b GPCMUX1[17:16]=11b Terminal Configuration and Functions Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 50 1, 25, 26, 50, 51, 75, 76, 100 (1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 51 μA = 0 V Analog inputs ±2 Input capacitance (1) See Table 4-2 for a list of pins with a pullup or pulldown. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 52 CMPSS1 to CMPSS8 active • VCU does complex multiply/accumulate with parallel load • TMU calculates a cosine • FPU does multiply/accumulate with parallel load Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 53 Actual results will vary based on the system implementation and conditions. Operational Current vs. Frequency 0.45 0.35 0.25 0.15 0.05 SYSCLK (MHz) VDDIO VDDA VDD3VFL Figure 5-1. Operational Current Versus Frequency Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 54 TMS320F28377S, TMS320F28376S, TMS320F28375S, TMS320F28374S SPRS881A – AUGUST 2014 – REVISED JUNE 2015 www.ti.com Power vs. Frequency SYSCLK (MHz) Power Figure 5-2. Power Versus Frequency Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 55 (3) This number represents the current drawn by the digital portion of the ADC module. (4) The ePWM is at /2 of SYSCLK. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 56 JESD51-7, High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages • JESD51-9, Test Boards for Area Array Surface Mount Package Thermal Measurements (2) lfm = linear feet per minute Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 57 JESD51-7, High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages • JESD51-9, Test Boards for Area Array Surface Mount Package Thermal Measurements (2) lfm = linear feet per minute Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 58 Pulse duration, XRS driven low by device after supplies are µs w(RSL1) stable Pulse duration, reset pulse generated by watchdog 512t cycles w(WDRS) c(OSCCLK) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 59 Boot code execution time is based on the current SYSCLK speed. The SYSCLK will be based on user environment and could be with or without PLL enabled. Figure 5-4. Warm Reset Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 60 (2) On reset, internal oscillator 2 (INTOSC2) is the default clock source for both system PLL (OSCCLK) and auxiliary PLL (AUXOSCCLK). Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 61 CAN Bit Clock To CANs AUXCLKIN CLKSRCCTL2 AUXPLLCTL1 AUXCLKDIVSEL AUXCLK AUXOSCCLK AUXPLLCLK To USB bit clock Divider Auxiliary PLL AUXPLLRAWCLK Figure 5-5. Device Clocking Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 62 (USB) c(OSCCLK) (1) Cycle count includes code execution of PLL initialization routine which could vary depending on compiler optimizations and flash wait states. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 63 H – 2 H + 2 w(XCOH) (1) A load of 40 pF is assumed for these parameters. (2) H = 0.5t c(XCO) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 64 X1/X2 and AUXCLKIN. ssosc ssosc RESONATOR CRYSTAL GPIO133/AUXCLKIN ssosc 3.3V 3.3V 3.3V OSCILLATOR 3.3V OSCILLATOR Figure 5-6. Connecting Input Clocks to a 2837xS Device Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 65 (1) Start-up time is dependent on the crystal and tank circuit components. It is recommended that the crystal vendor characterize the application with the chosen crystal. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 66 TEST CONDITIONS UNIT Nominal frequency Frequency accuracy at room 30°C ±0.1% temperature Frequency accuracy across temperature ±3% Start-up and settling time µs OSCST Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 67 OTP endurance for the array (write cycles) write Table 5-21. Flash Data Retention Duration PARAMETER TEST CONDITIONS UNIT Data retention duration = 85°C years retention Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 68 TRST TDIS 3.3 V RTCK 4.7 k 4.7 k 3.3 V EMU0 EMU1 3.3 V Figure 5-7. Connecting to the 14-Pin JTAG Header Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 69 Fall time, GPIO switching high to low All GPIOs f(GPO) Toggling frequency, GPO pins fGPO GPIO r(GPO) f(GPO) Figure 5-9. General-Purpose Output Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 70 5 sampling periods for detection to occur. Because external signals are driven asynchronously, an 13-SYSCLK-wide pulse ensures reliable recognition. Figure 5-10. Sampling Mode Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 71 Sampling window width = (SYSCLK cycle x 2 x QUALPRD) x 5, if QUALPRD ≠ 0 Sampling window width = (SYSCLK cycle) x 5, if QUALPRD = 0 SYSCLK GPIOxn w(GPI) Figure 5-11. General-Purpose Input Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 72 INT12 INPUTXBAR13 CPU1.XINT4 Control GPIOx CPU1.XINT5 Control INPUTXBAR14 CPU1.TINT1 CPU1.TIMER1 INT13 CPU1.TINT2 CPU1.TINT2 CPU1.TIMER2 INT14 Peripherals Figure 5-12. External and ePIE Interrupt Sources Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 73 (2) This assumes that the ISR is in a single-cycle memory. w(INT) XNMI, XINT1, XINT2 d(INT) Address bus Interrupt Vector (internal) Figure 5-13. External Interrupt Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 74 Dx, LSx, GSx memories Power down, memory contents are lost On with output state preserved Oscillators, PLL, analog Enters Low-Power Mode peripherals, Flash Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 75 WAKE can be any enabled interrupt, WDINT or XRS. After the IDLE instruction is executed, a delay of five OSCCLK cycles (minimum) is needed before the wakeup signal could be asserted. Figure 5-14. IDLE Entry and Exit Timing Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 76 (1) This is the time taken to begin execution of the instruction that immediately follows the IDLE instruction. Execution of an ISR (triggered by the wakeup signal) involves additional latency. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 77 After a latency period, the STANDBY mode is exited. Normal execution resumes. The device will respond to the interrupt (if enabled). Figure 5-15. STANDBY Entry and Exit Timing Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 78 Flash module in active state cycles d(WAKE-HALT) • Wakeup from flash 17500t c(OSCCLK) – Flash module in sleep state • Wakeup from SARAM c(OSCCLK) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 79 The user must relock the PLL upon HALT wakeup to ensure a stable PLL lock. Figure 5-16. HALT Entry and Exit Timing Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 80 Delay time, IDLE instruction executed to XCLKOUT stop cycles d(IDLE-XCOS) c(SYSCLK) Delay time, external wake signal to loRestore function start d(WAKE-HIB) • Wakeup from flash Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 81 Regardless if the user has disabled Isolation in the IoRestore function or if IoRestore is not defined, the BootROM will automatically disable isolation before booting as determined by the HIBBOOTMODE register. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 82 Note that the EMIF module does not support mobile SDRAM devices. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 83 MEWC in the Asynchronous Wait Cycle Configuration Register. See the TMS320F2837xS Delfino Microcontrollers Technical Reference Manual (SPRUHX5) for more information. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 84 EMxWE high Output setup time, EMxD[y:0] valid (WS)*E–3 (WS)*E+1 su(EMDV-EMWEL) to EMxWE low Output hold time, EMxWE high to (WH)*E–3 (WH)*E h(EMWEH-EMDIV) EMxD[y:0] invalid Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 85 Figure 5-18. Asynchronous Memory Read Timing Extended Due to EMxWAIT SETUP STROBE STROBE HOLD EMxCS[y:2] EMxBA[y:0] EMxA[y:0] EMxD[y:0] EMxOE EMxWAIT Asserted Deasserted Figure 5-19. EMxWAIT Read Timing Requirements Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 86 Figure 5-20. Asynchronous Memory Write Timing Extended Due to EMxWAIT SETUP STROBE STROBE HOLD EMxCS[y:2] EMxBA[y:0] EMxA[y:0] EMxD[y:0] EMxWE EMxWAIT Asserted Deasserted Figure 5-21. EMxWAIT Write Timing Requirements Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 87 Output hold time, EMxCLK rising to EMxWE invalid oh(CLKH-WEIV) Delay time, EMxCLK rising to EMxD[y:0] tri-stated d(CLKH-DHZ) Output hold time, EMxCLK rising to EMxD[y:0] driving oh(CLKH-DLZ) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 88 BASIC SDRAM READ OPERATION EMxCLK EMxCS[y:2] EMxDQM[y:0] EMxBA[y:0] EMxA[y:0] 2 EM_CLK Delay EMxD[y:0] EMxRAS EMxCAS EMxWE Figure 5-22. Basic SDRAM Read Operation Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 89 SPRS881A – AUGUST 2014 – REVISED JUNE 2015 BASIC SDRAM WRITE OPERATION EMxCLK EMxCS[y:2] EMxDQM[y:0] EMxBA[y:0] EMxA[y:0] EMxD[y:0] EMxRAS EMxCAS EMxWE Figure 5-23. Basic SDRAM Write Operation Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 90 Analog Subsystem Block Diagram for the 176-pin PTP package. Figure 5-26 shows the Analog Subsystem Block Diagram for the 100-pin PZP package. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 91 Digital VDDA or VDAC Filter CTRIPOUT8H DAC12 REFLO DAC12 Digital CTRIP8L VREFLOD Filter CTRIPOUT8L CMPIN8N Figure 5-24. Analog Subsystem Block Diagram (337-Ball ZWT) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 92 Digital VDDA or VDAC Filter CTRIPOUT8H DAC12 REFLO DAC12 Digital CTRIP8L VREFLOD Filter CTRIPOUT8L CMPIN8N Figure 5-25. Analog Subsystem Block Diagram (176-Pin PTP) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 93 Digital VDDA or VDAC Filter CTRIPOUT4H DAC12 REFLO DAC12 Digital CTRIP4L VREFLOB Filter CMPIN4N CTRIPOUT4L Figure 5-26. Analog Subsystem Block Diagram (100-Pin PZP) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 94 – Saturating offset calibration – Error from setpoint calculation – High, low, and zero-crossing compare, with interrupt and ePWM trip capability – Trigger-to-sample delay capture Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 95 ADCEVT Event CONFIG ADCEVTINT Logic VREFLO Reference Voltage Levels Post Processing Block (1-4) Interrupt Block (1-4) ADCINT1-4 Figure 5-27. ADC Module Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 96 (6) Code deviation due to operation of multiple ADCs simultaneously. (7) All ADCs operating with identical ADCCLK, S+H duration, and triggers. (8) All ADCs operating with heterogenous ADCCLK, S+H duration, or triggers. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 97 (5) Code deviation due to operation of multiple ADCs simultaneously. (6) All ADCs operating with identical ADCCLK, S+H duration, and triggers. (7) All ADCs operating with heterogenous ADCCLK, S+H duration, or triggers. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 98 Sampling switch resistance 700 Ω Sampling capacitor 16.5 pF Nominal source impedance 50 Ω ADCINxP Switch VSSA ADCINxN Switch Figure 5-29. Differential Input Model Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 99 . For other transitions, the actually initial voltage on C will be close to the voltage of the previously REFLO converted channel. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 100 If the bit is cleared, this will coincide with the end of the S+H window. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 101 ADCSOCFLG.SOC1 ADCRESULT0 Sample n (old data) ADCRESULT1 (old data) Sample n+1 ADCINTFLG.ADCINTx Figure 5-30. ADC Timings for 12-Bit Mode in Early Interrupt Mode Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 102 ADCSOCFLG.SOC1 ADCRESULT0 Sample n (old data) ADCRESULT1 (old data) Sample n+1 ADCINTFLG.ADCINTx Figure 5-31. ADC Timings for 12-Bit Mode in Late Interrupt Mode Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 103 ADCSOCFLG.SOC1 ADCRESULT0 (old data) Sample n ADCRESULT1 (old data) Sample n+1 ADCINTFLG.ADCINTx Figure 5-32. ADC Timings for 16-Bit Mode in Early Interrupt Mode Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 104 (old data) Sample n ADCRESULT1 (old data) Sample n+1 ADCINTFLG.ADCINTx Figure 5-33. ADC Timings for 16-Bit Mode in Late Interrupt Mode (SYSCLK Cycles) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 105 Table 5-49. Temperature Sensor Electrical Characteristics over recommended operating conditions (unless otherwise noted) PARAMETER UNIT Temperature accuracy ±15 °C Start-up time µs ADC acquisition time Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 106 VDDA or VDAC Filter CTRIPOUT8H CTRIPOUT8L DAC12 CTRIP8L CAPOUT Trip DAC12 Digital CTRIPOUT8L Filter CMPIN8N Pin Figure 5-34. CMPSS Connectivity (337-Ball ZWT and 176-Pin PTP) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 107 CMPIN4P Pin CTRIP4H Digital CTRIPOUT4H VDDA or VDAC Filter DAC12 CTRIP4L DAC12 Digital CTRIPOUT4L Filter CMPIN4N Pin Figure 5-35. CMPSS Connectivity (100-Pin PZP) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 108 (1) Includes comparator input referred errors. (2) Disturbance error may be present on the reference DAC output for a certain amount of time after a comparator trip. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 109 VDDA SYSCLK > DACCTL[LOADMODE] DACVALS 12-bit DACVALA Buffer PWMSYNC1 > VSSA PWMSYNC2 PWMSYNC3 VSSA … PWMSYNCn DACCTL[SYNCSEL] Figure 5-36. DAC Module Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 110 (2) The DAC output is monotonic. (3) The DAC can generate voltages outside of this range, but the output voltage will not be linear. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 111 Capture events CEVT[1:4] Interrupt Continuous / Trigger to PIE Oneshot CTR_OVF Capture Control Flag CTR=PRD control CTR=CMP Figure 5-37. eCAP Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 112 (1) For an explanation of the input qualifier parameters, see Table 5-23. Table 5-54. eCAP Switching Characteristics over recommended operating conditions (unless otherwise noted) PARAMETER UNIT Pulse duration, APWMx output high/low w(APWM) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 113 Figure 5-38 shows the signal interconnections with the ePWM. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 114 CMPD Shadow (16) These events are generated by the type-4 ePWM digital compare (DC) submodule. Figure 5-38. ePWM Submodules Showing Critical Internal Signal Interconnections Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 115 Filter-Reset EQEPERR FLT1 PWM11.CMPC FLT1 CLKFAIL Filter-Reset FLT1 PWM11.CMPD CPU1.EMUSTOP FLT1 EPWMn.EMUSTOP Filter-Reset FLT1 PWM12.CMPC FLT1 Filter-Reset FLT1 PWM12.CMPD FLT1 Figure 5-39. ePWM Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 116 SYNCSEL.EPWM7SYNCIN EPWM9 EPWM10 EPWM10SYNCOUT EPWM11 SYNCSEL.EPWM10SYNCIN EPWM12 ECAP1 ECAP1SYNCOUT SYNCSEL .SYNCOUT ECAP2 SYNCSEL.ECAP1SYNCIN ECAP3 ECAP4 SYNCSEL.ECAP4SYNCIN ECAP5 ECAP6 Figure 5-40. Synchronization Chain Architecture Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 117 PWM refers to all the PWM pins in the device. The state of the PWM pins after TZ is taken high depends on the PWM recovery software. Figure 5-41. PWM Hi-Z Characteristics Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 118 (QDU) EQEPxSIN PCSOUT QPOSSLAT EQEPxSOUT EQEPxS QPOSILAT EQEPxSOE QPOSCNT QEINT QPOSCMP QPOSINIT QFRC QPOSMAX QCLR QPOSCTL eQEP Peripheral Figure 5-42. eQEP Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 119 Delay time, external clock to counter increment cycles d(CNTR)xin c(SYSCLK) Delay time, QEP input edge to position compare sync output cycles d(PCS-OUT)QEP c(SYSCLK) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 120 SFO function in end applications. SFO functions help to estimate the number of MEP steps per SYSCLK period dynamically while the HRPWM is in operation. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 121 (MFE) bit or the PWM signals. • Filter data can be 16-bit or 32-bit representation • PWMs can be used to generate modulator clock for sigma-delta modulators Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 122 Filter Channel 2 SD2_C2 Register Sync SD2_D3 Filter Channel 3 Data Bus SD2_C3 Sync SD2_D4 Filter Channel 4 SD2_C4 SysCLK Figure 5-43. SDFM Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 123 Figure 5-44. SDFM Timing Diagram – Mode 0 Mode 1 w(SDCH)M1 c(SDC)M1 SDx_Cy su(SDDV-SDCL)M1 su(SDDV-SDCH)M1 SDx_Dy h(SDCL-SDD)M1 h(SDCH-SDD)M1 Figure 5-45. SDFM Timing Diagram – Mode 1 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 124 Figure 5-46. SDFM Timing Diagram – Mode 2 (CLKx is driven externally) Mode 3 c(SDC)M3 w(SDCH)M3 SDx_Cy su(SDDV-SDCH)M3 h(SDCH-SDD)M3 SDx_Dy Figure 5-47. SDFM Timing Diagram – Mode 3 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 125 CAN protocol. In this situation, an external clock source must be used. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 126 An additional interrupt that can be used by the CPU when in FIFO mode • Module enable/disable capability • Free data format mode Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 127 Peripheral Bus I2CRSR I2CDRR Control/Status Registers Clock Synchronizer Prescaler Noise Filters Interrupt to I2C INT CPU/PIE Arbitrator Figure 5-48. I C Peripheral Module Interfaces Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 128 + 0.3 DDIO DDIO Low-level output voltage Sinking 3 mA Input current on pins 0.1 V < V < 0.9 V –10 µA Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 129 CLKSRG source could be LSPCLK, CLKX, or CLKR. Serial port performance is limited by I/O buffer switching speed. Internal prescalers must be adjusted such that the peripheral speed is less than the I/O buffer speed limit. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 130 DRR1 Receive Buffer McBSP Receive Interrupt Select Logic RX Interrupt Logic Interrupt MRINT Peripheral Read Bus To CPU Figure 5-49. McBSP Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 131 (3) Internal clock prescalers must be adjusted such that the McBSP clock (CLKG, CLKX, CLKR) speeds are not greater than the I/O buffer speed limit (30 MHz). Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 132 (2) 2P = 1/CLKG in ns. (3) C = CLKRX low pulse width = P D = CLKRX high pulse width = P Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 133 Bit 0 Bit (n−1) (n−2) (n−3) (XDATDLY=00b) Bit 0 Bit (n−1) (n−2) (XDATDLY=01b) Bit 0 Bit (n−1) (XDATDLY=10b) Figure 5-51. McBSP Transmit Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 134 (n-3) (n-4) Bit 0 Bit(n-1) (n-2) (n-3) (n-4) Figure 5-52. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 135 (n-3) (n-4) Bit 0 Bit(n-1) (n-2) (n-3) (n-4) Figure 5-53. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 136 (n-3) (n-4) Bit 0 Bit(n-1) (n-2) (n-3) (n-4) Figure 5-54. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 137 (n-3) (n-4) Bit 0 Bit(n-1) (n-2) (n-3) (n-4) Figure 5-55. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1 Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 138 (bits 7–0), and the upper byte (bits 15–8) is read as zeros. Writing to the upper byte has no effect. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 139 SCIRXST.4 – 2 SCIFFRX.15 RX Error RX Error RX ERR INT ENA SCI RX Interrupt select logic SCICTL1.6 Figure 5-56. SCI Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 140 Data-memory-mapped control and status registers enable the CPU to access the I C module registers and FIFOs. The SCI receiver and transmitter operate independently. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 141 SPISTE inversion for digital audio interface receive mode on devices with two SPI modules • DMA support • High-speed mode for up to 40-MHz full-duplex communication Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 142 PCLKCR8 Low Speed LSPCLK SYSCLK Prescaler Clock SYSRS SPISIMO GPIO SPISOMI SPIINT SPICLK SPITXINT SPISTE SPIRXDMA SPITXDMA Figure 5-57. SPI Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 143 TMS320F2837xS Delfino Microcontrollers Technical Reference Manual (SPRUHX5). In order to use the SPI in High-Speed mode, the application must use the high-speed enabled GPIOs (see Section 4.4.5). Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 144 – 3 d(SPCL-STE)M c(SPC) (clock polarity = 0) Delay time, SPICLK high to SPISTE invalid 0.5t – 3 d(SPCH-STE)M c(SPC) (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 145 (clock polarity = 0) Delay time, SPICLK high to SPISTE 0.5t – 3 d(SPCH-STE)M c(SPC) invalid (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 146 On the trailing end of the word, SPISTE will go inactive except between back-to-back transmit words in both FIFO and non-FIFO modes. Figure 5-58. SPI Master Mode External Timing (Clock Phase = 0) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 147 – 3 d(SPCL-STE)M c(SPC) (clock polarity = 0) Delay time, SPICLK high to SPISTE invalid 0.5t – 3 d(SPCH-STE)M c(SPC) (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 148 On the trailing end of the word, SPISTE will go inactive except between back-to-back transmit words in both FIFO and non-FIFO modes. Figure 5-59. SPI Master Mode External Timing (Clock Phase = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 149 SPISOMI SPISOMI Data Is Valid SPISIMO Data SPISIMO Must Be Valid SPISTE Figure 5-60. SPI Slave Mode External Timing (Clock Phase = 0) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 150 SPISOMI Data Is Valid Data Valid Data Valid SPISIMO Data SPISIMO Must Be Valid SPISTE Figure 5-61. SPI Slave Mode External Timing (Clock Phase = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 151 – 1 d(SPCL-STE)M c(SPC) (clock polarity = 0) Delay time, SPICLK high to SPISTE invalid 0.5t – 1 d(SPCH-STE)M c(SPC) (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 152 (clock polarity = 0) Delay time, SPICLK high to SPISTE 0.5t – 1 d(SPCH-STE)M c(SPC) invalid (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 153 On the trailing end of the word, SPISTE will go inactive except between back-to-back transmit words in both FIFO and non-FIFO modes. Figure 5-62. High-Speed SPI Master Mode External Timing (Clock Phase = 0) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 154 – 1 d(SPCL-STE)M c(SPC) (clock polarity = 0) Delay time, SPICLK high to SPISTE invalid 0.5t – 1 d(SPCH-STE)M c(SPC) (clock polarity = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 155 On the trailing end of the word, SPISTE will go inactive except between back-to-back transmit words in both FIFO and non-FIFO modes. Figure 5-63. High-Speed SPI Master Mode External Timing (Clock Phase = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 156 SPISOMI Data Is Valid SPISIMO Data SPISIMO Must Be Valid SPISTE Figure 5-64. High-Speed SPI Slave Mode External Timing (Clock Phase = 0) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 157 Data Valid Data Valid SPISIMO Data SPISIMO Must Be Valid SPISTE Figure 5-65. High-Speed SPI Slave Mode External Timing (Clock Phase = 1) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 158 USB. For applications using the USB boot mode, see Section 6.6.4 (Boot ROM and Peripheral Booting) for clock frequency requirements. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 159 Full speed, differential, C = 50 pF, 10%/90%, Rise time Rpu on D+ Full speed, differential, C = 50 pF, 10%/90%, Fall time Rpu on D+ Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 160 CPU1.CLA1 Memory) Figure 5-67. uPP Integration NOTE On some TI devices, the uPP IP is also called the Radio Peripheral Interface (RPI) module. Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 161 DATA OUT DATA[7:0]/GPIOx Internal Data Interleaving DATA IN (TX/RX) Arbit 64 Bit MEM RD I/F Arbi Q-FIFO Figure 5-68. uPP Functional Block Diagram Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 162 Delay time, ENABLE valid after CLK high d(CLKH-ENV) Delay time, DATA valid after CLK high d(CLKH-DV) Delay time, DATA valid after CLK low d(CLKL-DV) Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 163 Data9 Figure 5-69. uPP Single Data Rate (SDR) Receive Timing START ENABLE WAIT DATA[n:0] Figure 5-70. uPP Double Data Rate (DDR) Receive Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 164 Data9 Figure 5-71. uPP Single Data Rate (SDR) Transmit Timing START ENABLE WAIT DATA[n:0] Figure 5-72. uPP Double Data Rate (DDR) Transmit Timing Specifications Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 165 F2837xS. A USB 2.0 host port with MAC and PHY lets users easily add USB connectivity to their application. Functional Block Diagram Figure 6-1 shows the CPU system and associated peripherals. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 166 SD-1/2 1/../6 (16L FIFO) HRPWM-1/../8 (32-mbox) (16L FIFO) (16L FIFO) GPIO MUX, Input X-BAR, Output X-BAR Figure 6-1. Functional Block Diagram Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 167 32K x 16 0x003F 8000 0x003F FFBF Vectors 64 x 16 0x003F FFC0 0x003F FFFF (1) Only available on F28377S and F28375S. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 168 User OTP ECC Bank 0 128 x 16 0x0107 1000 0x0107 107F User OTP ECC Bank 1 128 x 16 0x0107 1200 0x0107 127F Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 169 User OTP ECC Bank 0 128 x 16 0x0107 1000 0x0107 107F Flash ECC Bank 0 32K x16 0x0108 0000 0x0108 7FFF Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 170 0x0000 4900 0x0000 49FF EPwm11Regs EPWM_REGS 0x0000 4A00 0x0000 4AFF EPwm12Regs EPWM_REGS 0x0000 4B00 0x0000 4BFF ECap1Regs ECAP_REGS 0x0000 5000 0x0000 501F Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 171 0x0000 7920 0x0000 793F TrigRegs TRIG_REGS 0x0000 7940 0x0000 794F DmaClaSrcSelRegs DMA_CLA_SRC_SEL_REGS 0x0000 7980 0x0000 798F EPwmXbarRegs EPWM_XBAR_REGS 0x0000 7A00 0x0000 7A3F Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 172 TMS320F28377S 0x00FF 0400 TMS320F28376S 0x00FE 0400 TMS320F28375S 0x00FD 0400 TMS320F28374S 0x00FC 0400 REVID 0x0005 D00C Silicon revision number Revision B 0x0000 0002 Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 173 GPIO to a particular master, the respective GPIO Data Register will control the GPIO. See the "General-Purpose Input/Output (GPIO)" chapter of the TMS320F2837xS Delfino Microcontrollers Technical Reference Manual (SPRUHX5) for more details. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 174 FPU register set (R0H to R7H) to carry out their operations. A detailed explanation of the workings of the FPU can be found in the TMS320C28x Extended Instruction Sets Reference Guide (SPRUHS1). Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 175 RPT MAC 2p+N Repeat MAC. Single cycle after the first operation. For more information, see the TMS320C28x Extended Instruction Sets Reference Guide (SPRUHS1). Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 176 CLA Message MSTF(32) RAMs MR0(32) MR1(32) MR2(32) Shared MR3(32) Peripherals MEALLOW MAR0(16) MAR1(16) CPU Read Data Bus Figure 6-2. CLA Block Diagram Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 177 – McBSP – EMIF • Word Size: 16-bit or 32-bit (SPI and McBSP limited to 16-bit) • Throughput: four cycles/word (without arbitration) Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 178 SPITX (A-C), SPIRX (A-C) DMA Trigger Source CPU and DMA Data Path SDFM EPWM McBSP EMIF1 (12) Figure 6-3. DMA Block Diagram Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 179 The device in this boot mode loops in the boot ROM. This mode is useful if users want to connect a debugger on a secure device or if users do not want the device to execute an application in flash yet. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 180 USB Boot and X2 pins). A 20-MHz crystal should be USB0DP - GPIO43 present on the board if this boot mode is selected. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 181 LSx memory is shared Data Write between CPU and CLA1. Emulation Read LSx memory is CLA1 Fetch Only Emulation Write program memory. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 182 (including passwords) in OTP. The secure resources available are: OTP memory, CLA, LSx RAM, flash sectors, and secure ROM. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 183 If the software does not respond to the enabled latched FAIL condition, then the NMI watchdog will trigger a reset after a preprogrammed time interval. Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 184 Out of Window Detector Key Detector Bad Key 55 + AA Generate WDRSTn 512-OSCCLK WDINTn Watchdog Timeout Output Pulse SCSR(WDENINT) Figure 6-4. Windowed Watchdog Detailed Description Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 185 Device Support 7.1.1 Development Support Texas Instruments (TI) offers an extensive line of development tools for the C28x family of MCUs, including tools to evaluate the performance of the processors, generate code, develop algorithm implementations, and fully integrate and debug software and hardware modules.

- Page 186 Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

- Page 187 100-Pin PZP PowerPAD Thermally Enhanced Thin Quad Flatpack (HTQFP) TECHNOLOGY F = Flash DEVICE 28377S 28376S 28375S 28374S Figure 7-1. Device Nomenclature Device and Documentation Support Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 188 TI EP meets the end system reliability requirement. Device and Documentation Support Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links: TMS320F28377S TMS320F28376S TMS320F28375S TMS320F28374S...

- Page 189 All other trademarks are the property of their respective owners. Electrostatic Discharge Caution This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

- Page 190 This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation. Mechanical Packaging and Orderable Information Copyright © 2014–2015, Texas Instruments Incorporated Submit Documentation Feedback Product Folder Links:...

- Page 196 PACKAGE OPTION ADDENDUM www.ti.com 26-Feb-2015 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples Drawing (4/5) TMS320F28374SPTPS PREVIEW HLQFP Call TI Call TI -40 to 125 TMS320F28374SPTPT PREVIEW HLQFP...

- Page 197 PACKAGE OPTION ADDENDUM www.ti.com 26-Feb-2015 Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples Drawing (4/5) TMX320F28377SZWTT PREVIEW NFBGA Call TI Call TI -40 to 105 The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs.

- Page 198 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue.

Need help?

Do you have a question about the Delfino TMS320F2837 S Series and is the answer not in the manual?

Questions and answers