Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Infineon Cypress CYTVII-B-E-2M-176-CPU

- Page 1 请注意赛普拉斯已正式并入英飞凌科技公司。 此封面页之后的文件标注有 “赛普拉斯” 的文件即该产品为此公司最初开发的。 请注 意作为英飞凌产品组合的部分, 英飞凌将继续为新的及现有客户提供该产品。 文件内容的连续性 事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何 变更。 未来的变更将在恰当的时候发生, 且任何变更将在历史页面记录。 订购零件编号的连续性 英飞凌继续支持现有零件编号的使用。 下单时请继续使用数据表中的订购零件编号。 www.infineon.com...

- Page 2 CYTVII-B-E-2M-176-CPU Evaluation Board User Guide Document Number. 002-29049 Rev. ** Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com...

- Page 3 Copyrights Copyrights © Cypress Semiconductor Corporation, 2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries (“Cypress”). This document, including any software or firmware included or referenced in this document (“Software”), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide.

-

Page 4: Table Of Contents

Contents 1. Introduction Precautions and Warnings...................4 2. Overview Functional Overview ....................7 3. Operation 4. Connections and Settings A. Schematics of CPU Board B. Component Assembly on CPU Board C. Schematics of Base Board D. Component Assembly on Base Board Revision History CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. -

Page 5: Introduction

Introduction This user guide provides instructions to use the CYTVII-B-E-2M-176-CPU and CYTVII-B-E-176-SO (when used with CYT2B98CAE Traveo™ II device) evaluation boards, collectively referred to as 'CPU board' in this document. This is an evaluation platform for the CYT2B98CAE Traveo II device. The board can be used standalone for basic validation or in combination with the CYTVII-B-E-BB Traveo II base board (available separately from Cypress). -

Page 6: Overview

Overview Figure 2-1 shows the CYTVII-B-E-176-SO board with the CYT2B78CAE Traveo II device. Figure 2-1. CYTVII-B-E-176-SO Board A variant of the CPU board (CYTVII-B-E-2M-176-CPU) is also available, where the Traveo II device is soldered directly onto the PCB. Functionally, the CYTVII-B-E-2M-176-CPU and CYTVII-B-E-176- SO boards are identical, except that the device can be easily replaced in the latter. - Page 7 Overview Figure 2-2. Traveo II Base board (CYTVII-B-E-BB) Two Samtec connectors on the CPU board and the corresponding mating connectors on the base board are used to connect signals across the two boards. When put together, the boards appear as shown in Figure 2-3.

-

Page 8: Functional Overview

Overview Functional Overview The CPU board has the following features: 1. One Traveo II device, either soldered or mounted on a socket (U4). 2. PMIC to generate the 5 V and 3.3 V output depending on the Jumper J23 selection, which pow- ers the CPU board and the base board (if connected). -

Page 9: Operation

Operation This section describes the operation of the CPU board and the base board. It is assumed that you have connected the CPU board to the base board using the Samtec interface and inserted a Traveo II device into the IC socket (applicable to SO boards only). The following method can be used to operate the CPU board and the base board: 1. - Page 10 Operation 4. A 12 V wall adapter board is supplied along with the CPU board. Connect the 12 V wall adapter to the barrel connector marked “12V DC” on the CPU board. Connect its plug to a mains socket using one of the four plug adapters provided in the white box (depending on the geographical location and the socket type available).

-

Page 11: Connections And Settings

Connections and Settings Ensure that the following jumpers are inserted on the base board to use each transceiver on the base board with respective firmware examples which activate each functionality of the device: 1. CAN0.0 from the device uses the CAN0 transceiver on the base board (connect jumpers J70, J71, J72) 2. - Page 12 Connections and Settings The device port pins are connected to pin headers on the base board as listed in Table 4-1. Table 4-1. Device Port Pin Connections on Base Board Access Port Pin on Pin Function Base Board PWM_18/PWM_22_N/TC_18_TR0/TC_22_TR1/SCB0_RX/SCB7_SDA/SCB0_MISO/ P0.0 JP6.15 LIN1_RX PWM_17/PWM_18_N/TC_17_TR0/TC_18_TR1/SCB0_TX/SCB7_SCL/SCB0_MOSI/...

- Page 13 Connections and Settings Table 4-1. Device Port Pin Connections on Base Board (continued) Access Port Pin on Pin Function Base Board PWM_M_9/PWM_44_N/TC_M_9_TR0/TC_44_TR1/EXT_MUX[2]_2/SCB3_RTS/ P13.2 JP10.16 SCB3_SCL/SCB3_CLK/LIN3_EN/CXPI1_EN/ADC[1]_14 PWM_45/PWM_M_9_N/TC_45_TR0/TC_M_9_TR1/EXT_MUX[2]_EN/SCB3_CTS/ P13.3 JP1.5 SCB3_SEL0/ADC[1]_15 PWM_M_10/PWM_45_N/TC_M_10_TR0/TC_45_TR1/PWM_H_4/SCB3_SEL1/ P13.4 JP6.4 LIN8_RX/ADC[1]_16 PWM_46/PWM_M_10_N/TC_46_TR0/TC_M_10_TR1/PWM_H_4_N/SCB3_SEL2/ P13.5 JP2.7 LIN8_TX/CXPI2_RX/ADC[1]_17 PWM_M_11/PWM_46_N/TC_M_11_TR0/TC_46_TR1/PWM_H_5/SCB3_SEL3/ P13.6 JP2.11 LIN8_EN/CXPI2_TX/TRIG_IN[22]/ADC[1]_18 PWM_47/PWM_M_11_N/TC_47_TR0/TC_M_11_TR1/PWM_H_5_N/CXPI2_EN/ P13.7...

- Page 14 Connections and Settings Table 4-1. Device Port Pin Connections on Base Board (continued) Access Port Pin on Pin Function Base Board PWM_58/PWM_59_N/TC_58_TR0/TC_59_TR1/PWM_H_3/SCB3_RTS/SCB3_SCL/ P17.3 JP4.5 TRIG_IN[26] SCB3_CLK/ PWM_57/PWM_58_N/TC_57_TR0/TC_58_TR1/PWM_H_3_N/SCB3_CTS/SCB3_SEL0/ P17.4 JP4.11 TRIG_IN[27] P17.5 PWM_56/PWM_57_N/TC_56_TR0/TC_57_TR1/SCB3_SEL1 JP3.10 P17.6 PWM_M_4/PWM_56_N/TC_M_4_TR0/TC_56_TR1/SCB3_SEL2 JP3.8 P17.7 PWM_M_5/PWM_M_4_N/TC_M_5_TR0/TC_M_4_TR1 JP3.6 PWM_M_6/PWM_M_5_N/TC_M_6_TR0/TC_M_5_TR1/PWM_H_0/SCB1_RX/ P18.0 JP3.18 ADC[2]_0...

- Page 15 Connections and Settings Table 4-1. Device Port Pin Connections on Base Board (continued) Access Port Pin on Pin Function Base Board PWM_2/PWM_3_N/TC_2_TR0/TC_3_TR1/PWM_H_5_N/SCB7_SEL2/LIN5_EN/ P2.5 JP8.7 TRIG_IN[7] P20.0 PWM_30/PWM_29_N/TC_30_TR0/TC_29_TR1/TC_H_2_TR1/SCB2_SEL2/LIN5_RX JP7.4 P20.1 PWM_49/PWM_30_N/TC_49_TR0/TC_30_TR1/TC_H_3_TR0/LIN5_TX JP7.5 P20.2 PWM_48/PWM_49_N/TC_48_TR0/TC_49_TR1/TC_H_3_TR1/LIN5_EN JP4.14 P20.3 PWM_47/PWM_48_N/TC_47_TR0/TC_48_TR1/SCB1_RX/SCB1_MISO/CAN1_2_TX JP4.15 PWM_46/PWM_47_N/TC_46_TR0/TC_47_TR1/SCB1_TX/SCB1_SDA/SCB1_MOSI/ P20.4 JP5.8 CAN1_2_RX PWM_45/PWM_46_N/TC_45_TR0/TC_46_TR1/SCB1_RTS/SCB1_SCL/SCB1_CLK/ P20.5...

- Page 16 Connections and Settings Table 4-1. Device Port Pin Connections on Base Board (continued) Access Port Pin on Pin Function Base Board PWM_25/PWM_M_11_N/TC_25_TR0/TC_M_11_TR1/SCB7_SEL1/TRIG_DBG[0]/ P23.4 #N/A SWJ_SWO_TDO/TRIG_IN[31] PWM_24/PWM_25_N/TC_24_TR0/TC_25_TR1/SCB7_SEL2/LIN9_RX/ P23.5 #N/A SWJ_SWCLK_TCLK P23.6 PWM_23/PWM_24_N/TC_23_TR0/TC_24_TR1/LIN9_TX/SWJ_SWDIO_TMS #N/A PWM_22/PWM_23_N/TC_22_TR0/TC_23_TR1/LIN9_EN/CAL_SUP_NZ/ P23.7 #N/A HIBERNATE_WAKEUP[1] SWJ_SWDOE_TDI/EXT_CLK/ PWM_1/PWM_2_N/TC_1_TR0/TC_2_TR1/PWM_H_6_N/SCB6_RX/SCB6_MISO/ P3.0 JP10.14 TRIG_DBG[0] CAN0_3_TX/ PWM_0/PWM_1_N/TC_0_TR0/TC_1_TR1/PWM_H_7_N/SCB6_TX/SCB6_SDA/...

- Page 17 Connections and Settings Table 4-1. Device Port Pin Connections on Base Board (continued) Access Port Pin on Pin Function Base Board P6.6 PWM_M_3/PWM_2_N/TC_M_3_TR0/TC_2_TR1/SCB4_SEL3/TRIG_IN[8]/ADC[0]_6 JP10.5 P6.7 PWM_3/PWM_M_3_N/TC_3_TR0/TC_M_3_TR1/TRIG_IN[9]/ADC[0]_7 JP11.11 PWM_M_4/PWM_3_N/TC_M_4_TR0/TC_3_TR1/SCB5_RX/SCB5_MISO/LIN4_RX/ P7.0 JP12.3 CXPI0_RX/ADC[0]_8 PWM_15/PWM_M_4_N/TC_15_TR0/TC_M_4_TR1/SCB5_TX/SCB5_SDA/SCB5_- P7.1 JP12.6 MOSI/LIN4_TX/CXPI0_TX/ADC[0]_9 PWM_M_5/PWM_15_N/TC_M_5_TR0/TC_15_TR1/SCB5_RTS/SCB5_SCL/SCB5_CLK/ P7.2 JP12.5 LIN4_EN/CXPI0_EN/ADC[0]_10 P7.3 PWM_16/PWM_M_5_N/TC_16_TR0/TC_M_5_TR1/SCB5_CTS/SCB5_SEL0/ADC[0]_11 JP10.10 P7.4 PWM_M_6/PWM_16_N/TC_M_6_TR0/TC_16_TR1/SCB5_SEL1/ADC[0]_12...

-

Page 18: Schematics Of Cpu Board

Schematics of CPU Board This appendix contains the schematics of TVII-B-E-2M board. CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. 002-29049 Rev. **... - Page 19 Schematics of CPU Board Figure A-1. Block Diagram of CPU Board SYSTEM ARCHITECTURE BOARD TO BOARD CONNECTOR-1 (180 PIN SAMTEC CONNECTOR) USB TO UART POWER SUPPLY TRANSCEIVER (PMIC 5V OUTPUT) (Data Only) (LDO 3V3 OUTPUT) TVII-B-E-2M RESET DEVICE CONTROLLER WITH RESET BUTTON PROGRAM/DEBUG INTERFACE (JTAG,SWD,ETM)

- Page 20 Schematics of CPU Board Figure A-2. Power Architecture POWER ARCHITECTURE VCC_12V 12V POWER BOARD TO BOARD CONNECTOR-2 INPUT BOARD TO BOARD CONNECTOR-1 PMIC(5V,1A) TRAVEO II UART TO USB_VIN CONNECTOR CONVERTER DEBUG INTERFACE ARM ETM MICTOR, ARM STANDARD JTAG, CORTEX DEBUG + ETM, CORTEX DEBUG CYPRESS SEMICONDUCTOR CYPRESS SEMICONDUCTOR...

- Page 21 Schematics of CPU Board Figure A-3. 5V Power Input 12V POWER INPUT VCC12V_EXT VCC_12V HDR_1X2 HDR_1X2 HDR_1X2 FUSE_12V ZENER_12V 1.6A B120-13 THRU HOLE 500SSP1S2M2QEA BLM21PG300SH1D CON_PWRJACK3_RAPC722 SMAJ12CA 100uF_25V 47uF 0.1uF 0.1uF 5002 12V to 5V PMIC VCC_12V VCC_12V VCCOUT 0.1uF 10uF 0.1uF 4.7uF...

- Page 22 Schematics of CPU Board Figure A-4. 3V3 LDO Regulator 3V3 LDO REGULATOR VCC_12V VCC_PMIC VCC VCC_LDO VCC_LDO 3 Pin Jumper 10 uF NCP1117DT33T5G 22 uF 0.1uF LED5V 220E CYPRESS SEMICONDUCTOR CYPRESS SEMICONDUCTOR CYPRESS SEMICONDUCTOR LTST-C150GKT 198 CHAMPION COURT 198 CHAMPION COURT 198 CHAMPION COURT THRU HOLE SAN JOSE, CA 95134...

- Page 23 Schematics of CPU Board Figure A-5. Debug Interface DEBUG INTERFACE ARM ETM MICTOR CORTEX DEBUG TRACE_CLOCK SRST_MICTOR SWO_TDO SWCLK_TCLK SWDIO_TMS SWDOE_TDI 0.1uF 0.1uF TRSTN SWDIO_TMS TRACE_DATA_3 SWCLK_TCLK TRACE_DATA_2 SWO_TDO TRACE_DATA_1 SWDOE_TDI NRST_CORTEX10 TRACE_CTL TRACE_DATA_0 CON_BOX_2X5_M THRU HOLE CON_MICTOR_2X19_F ARM STANDARD JTAG CORTEX DEBUG + ETM 0.1uF 220E...

- Page 24 Schematics of CPU Board Figure A-6. UART to USB & RESERT USB TO UART TRANSCEIVER OVERLAP THE VCCIO_USB PADS OF R25 & R26 VCCIO_USB VCC_USB USB_VIN 600E DEFAULT CLOSE HDR_1X2 4.7uF 0.1uF 0.1uF 4.7uF 10000pF USBDM CON_MUSB-B_5_F VBUS USBDM_CONN USBDP {12,16} UART_SCB3_RX USBDP...

- Page 25 Schematics of CPU Board Figure A-7. GPIO, Clock, and Filter TPS5 TPS7 TPS4 RC FILTER {11} GPIO_038 GPIO_082 {16} {11} GPIO_040 GPIO_084 {16} {11} BB_CAN2_TXD_N BB_CAN2_TXD {16} 0.1uF 0.1uF 0.1uF TPS6 TPS3 GPIO_083 {16} {11,18} BB_CAN2_RXD_N BB_CAN2_RXD {16} {11} GPIO_039 0.1uF 0.1uF The return path from Capacitor, must be wired to the VSSA...

- Page 26 Schematics of CPU Board Figure A-8. LQFP-176 P1 {18} BB_LIN1_RX P0.0/PWM_18/PWM_22_N/TC_18_TR0/TC_22_TR1/SCB0_RX/SCB7_SDA/SCB0_MISO/LIN1_RX {18} BB_LIN1_TX P0.1/PWM_17/PWM_18_N/TC_17_TR0/TC_18_TR1/SCB0_TX/SCB7_SCL/SCB0_MOSI/LIN1_TX {17,18} BB_LIN1_SLP {17,18} BB_CAN1_TXD P0.2/PWM_14/PWM_17_N/TC_14_TR0/TC_17_TR1/SCB0_RTS/SCB0_SCL/SCB0_CLK/LIN1_EN/CAN0_1_TX {17,18} BB_CAN7_TXD {17,18} BB_CAN1_RXD P0.3/PWM_13/PWM_14_N/TC_13_TR0/TC_14_TR1/SCB0_CTS/SCB0_SDA/SCB0_SEL0/CAN0_1_RX {17,18} BB_CAN7_RXD {16} GPIO_001 P1.0/PWM_12/PWM_13_N/TC_12_TR0/TC_13_TR1/PWM_H_4/SCB0_SCL/SCB0_MISO {16} GPIO_002 P1.1/PWM_11/PWM_12_N/TC_11_TR0/TC_12_TR1/PWM_H_5/SCB0_SDA/SCB0_MOSI {16} GPIO_003 P1.2/PWM_10/PWM_11_N/TC_10_TR0/TC_11_TR1/PWM_H_6/SCB0_CLK/TRIG_IN[0] {16} GPIO_004 P1.3/PWM_8/PWM_10_N/TC_8_TR0/TC_10_TR1/PWM_H_7/SCB0_SEL0/TRIG_IN[1] {6,19} TRSTN P2.0/PWM_7/PWM_8_N/TC_7_TR0/TC_8_TR1/TC_H_4_TR0/SCB7_RX/SCB0_SEL1/SCB7_MISO/LIN0_RX/CAN0_0_TX/SWJ_TRSTN/TRIG_IN[2] {18} BB_LIN0_TX...

- Page 27 Schematics of CPU Board Figure A-9. LQFP-176 P2 {16} BB_CAN7_WAKE P5.0/PWM_9/PWM_8_N/TC_9_TR0/TC_8_TR1/SCB5_SEL2/LIN7_RX {17} BB_CAN8_WAKE P5.1/PWM_10/PWM_9_N/TC_10_TR0/TC_9_TR1/LIN7_TX {17} BB_CAN9_WAKE P5.2/PWM_11/PWM_10_N/TC_11_TR0/TC_10_TR1/LIN7_EN {18} BB_LIN2_RX P5.3/PWM_12/PWM_11_N/TC_12_TR0/TC_11_TR1/LIN2_RX {16} GPIO_016 P5.4/PWM_13/PWM_12_N/TC_13_TR0/TC_12_TR1/LIN2_TX {16} GPIO_017 P5.5/PWM_14/PWM_13_N/TC_14_TR0/TC_13_TR1/LIN2_EN {19} BB_LIN3_RX P6.0/PWM_M_0/PWM_14_N/TC_M_0_TR0/TC_14_TR1/SCB4_RX/SCB4_MISO/LIN3_RX/ADC[0]_0 {19} BB_LIN3_TX P6.1/PWM_0/PWM_M_0_N/TC_0_TR0/TC_M_0_TR1/SCB4_TX/SCB4_SDA/SCB4_MOSI/LIN3_TX/ADC[0]_1 {17,19} BB_LIN3_SLP P6.2/PWM_M_1/PWM_0_N/TC_M_1_TR0/TC_0_TR1/SCB4_RTS/SCB4_SCL/SCB4_CLK/LIN3_EN/CAN0_2_TX/ADC[0]_2 {17,19} BB_CAN8_TXD {17,19} BB_LIN4_RX P6.3/PWM_1/PWM_M_1_N/TC_1_TR0/TC_M_1_TR1/SCB4_CTS/SCB4_SEL0/LIN4_RX/CAN0_2_RX/CAL_SUP_NZ/ADC[0]_3 {17,19} BB_CAN8_RXD {19}...

- Page 28 Schematics of CPU Board Figure A-10. LQFP-176 P3 {17} GPIO_024 P8.3/PWM_22/PWM_21_N/TC_22_TR0/TC_21_TR1/TRIG_DBG[0]/ADC[0]_18 {16} GPIO_025 P8.4/PWM_23/PWM_22_N/TC_23_TR0/TC_22_TR1/TRIG_DBG[1]/ADC[0]_19 {16} GPIO_026 P9.0/PWM_24/PWM_23_N/TC_24_TR0/TC_23_TR1/ADC[0]_20 {16} GPIO_027 P9.1/PWM_25/PWM_24_N/TC_25_TR0/TC_24_TR1/ADC[0]_21 {16} GPIO_028 P9.2/PWM_26/PWM_25_N/TC_26_TR0/TC_25_TR1/ADC[0]_22 {16} GPIO_029 P9.3/PWM_27/PWM_26_N/TC_27_TR0/TC_26_TR1/ADC[0]_23 {16} GPIO_030 P10.0/PWM_28/PWM_27_N/TC_28_TR0/TC_27_TR1/SCB4_RX/SCB4_MISO/TRIG_IN[18] {16} GPIO_031 P10.1/PWM_29/PWM_28_N/TC_29_TR0/TC_28_TR1/SCB4_TX/SCB4_SDA/SCB4_MOSI/TRIG_IN[19] {18} GPIO_032 P10.2/PWM_30/PWM_29_N/TC_30_TR0/TC_29_TR1/SCB4_RTS/SCB4_SCL/SCB4_CLK/LIN8_RX {18} GPIO_033 P10.3/PWM_31/PWM_30_N/TC_31_TR0/TC_30_TR1/SCB4_CTS/SCB4_SEL0/LIN8_TX {18} GPIO_034 P10.4/PWM_32/PWM_31_N/TC_32_TR0/TC_31_TR1/SCB4_SEL1/LIN8_EN/ADC[1]_0 {18} GPIO_035...

- Page 29 Schematics of CPU Board Figure A-11. LQFP-176 P4 {7,16} UART_SCB3_RX P13.0/PWM_M_8/PWM_43_N/TC_M_8_TR0/TC_43_TR1/EXT_MUX[2]_0/SCB3_RX/SCB3_MISO/LIN3_RX/CXPI1_RX/ADC[1]_12 {7,16} UART_SCB3_TX P13.1/PWM_44/PWM_M_8_N/TC_44_TR0/TC_M_8_TR1/EXT_MUX[2]_1/SCB3_TX/SCB3_SDA/SCB3_MOSI/LIN3_TX/CXPI1_TX/ADC[1]_13 {16,19} BB_CAN5_S P13.2/PWM_M_9/PWM_44_N/TC_M_9_TR0/TC_44_TR1/EXT_MUX[2]_2/SCB3_RTS/SCB3_SCL/SCB3_CLK/LIN3_EN/CXPI1_EN/ADC[1]_14 {16,19} BB_USER_LED6 {18,19} BB_LIN0_WAKE P13.3/PWM_45/PWM_M_9_N/TC_45_TR0/TC_M_9_TR1/EXT_MUX[2]_EN/SCB3_CTS/SCB3_SEL0/ADC[1]_15 {18,19} BB_USER_LED7 {18} BB_LIN1_WAKE P13.4/PWM_M_10/PWM_45_N/TC_M_10_TR0/TC_45_TR1/PWM_H_4/SCB3_SEL1/LIN8_RX/ADC[1]_16 {18} BB_USER_LED8 {18} BB_LIN2_WAKE P13.5/PWM_46/PWM_M_10_N/TC_46_TR0/TC_M_10_TR1/PWM_H_4_N/SCB3_SEL2/LIN8_TX/CXPI2_RX/ADC[1]_17 {18} BB_USER_LED9 {19} BB_LIN3_WAKE P13.6/PWM_M_11/PWM_46_N/TC_M_11_TR0/TC_46_TR1/PWM_H_5/SCB3_SEL3/LIN8_EN/CXPI2_TX/TRIG_IN[22]/ADC[1]_18 {19} BB_USER_BUTTON_1 {19} BB_LIN4_WAKE P13.7/PWM_47/PWM_M_11_N/TC_47_TR0/TC_M_11_TR1/PWM_H_5_N/CXPI2_EN/TRIG_IN[23]/ADC[1]_19 {19}...

- Page 30 Schematics of CPU Board Figure A-12. LQFP-176 P5 {18,19} BB_USER_LED4 P17.2/PWM_59/PWM_60_N/TC_59_TR0/TC_60_TR1/PWM_H_2_N/SCB3_TX/SCB3_SDA/SCB3_MOSI {18,19} BB_SPI0_WP {19} GPIO_056 P17.3/PWM_58/PWM_59_N/TC_58_TR0/TC_59_TR1/PWM_H_3/SCB3_RTS/SCB3_SCL/SCB3_CLK/TRIG_IN[26] {19} GPIO_057 P17.4/PWM_57/PWM_58_N/TC_57_TR0/TC_58_TR1/PWM_H_3_N/SCB3_CTS/SCB3_SEL0/TRIG_IN[27] {19} GPIO_058 P17.5/PWM_56/PWM_57_N/TC_56_TR0/TC_57_TR1/SCB3_SEL1 {19} GPIO_059 P17.6/PWM_M_4/PWM_56_N/TC_M_4_TR0/TC_56_TR1/SCB3_SEL2 {19} GPIO_060 P17.7/PWM_M_5/PWM_M_4_N/TC_M_5_TR0/TC_M_4_TR1 {19} BB_SPI0_MISO P18.0/PWM_M_6/PWM_M_5_N/TC_M_6_TR0/TC_M_5_TR1/PWM_H_0/SCB1_RX/SCB1_MISO/FAULT_OUT_0/ADC[2]_0 {19} BB_SPI0_MOSI P18.1/PWM_M_7/PWM_M_6_N/TC_M_7_TR0/TC_M_6_TR1/PWM_H_0_N/SCB1_TX/SCB1_SDA/SCB1_MOSI/FAULT_OUT_1/ADC[2]_1 {16} BB_SPI0_CLK P18.2/PWM_55/PWM_M_7_N/TC_55_TR0/TC_M_7_TR1/PWM_H_1/SCB1_RTS/SCB1_SCL/SCB1_CLK/ADC[2]_2 {6,19} TRACE_CLOCK P18.3/PWM_54/PWM_55_N/TC_54_TR0/TC_55_TR1/PWM_H_1_N/SCB1_CTS/SCB1_SEL0/TRACE_CLOCK/ADC[2]_3 {16} BB_SPI0_SS P18.4/PWM_53/PWM_54_N/TC_53_TR0/TC_54_TR1/PWM_H_2/SCB1_SEL1/TRACE_DATA_0/ADC[2]_4...

- Page 31 Schematics of CPU Board Figure A-13. LQFP-176 P6 {19} GPIO_070 P20.7/PWM_43/PWM_44_N/TC_43_TR0/TC_44_TR1/SCB1_SEL1/CXPI3_EN WCI/BTB P21.0/PWM_42/PWM_43_N/TC_42_TR0/TC_43_TR1/SCB1_SEL2/WCO_IN WCO/BTB P21.1/PWM_41/PWM_42_N/TC_41_TR0/TC_42_TR1/WCO_OUT ECI/BTB P21.2/PWM_40/PWM_41_N/TC_40_TR0/TC_41_TR1/TRIG_DBG[1]/EXT_CLK/ECO_IN ECO/BTB P21.3/PWM_39/PWM_40_N/TC_39_TR0/TC_40_TR1/ECO_OUT {19} GPIO_071 P21.4/PWM_38/PWM_39_N/TC_38_TR0/TC_39_TR1/HIBERNATE_WAKEUP[0] {6,7,14,18} CPU_XRES XRES {18} BB_LIN0_RX P21.5/PWM_37/PWM_38_N/TC_37_TR0/TC_38_TR1/LIN0_RX {19} GPIO_072 P21.6/PWM_36/PWM_37_N/TC_36_TR0/TC_37_TR1/LIN0_TX {18} GPIO_073 P21.7/PWM_35/PWM_36_N/TC_35_TR0/TC_36_TR1/LIN0_EN/CAL_SUP_NZ/RTC_CAL {6,19} TRACE_DATA_0 P22.0/PWM_34/PWM_35_N/TC_34_TR0/TC_35_TR1/SCB6_RX/SCB6_MISO/CAN1_1_TX/TRACE_DATA_0 {6,19} TRACE_DATA_1 P22.1/PWM_33/PWM_34_N/TC_33_TR0/TC_34_TR1/SCB6_TX/SCB6_SDA/SCB6_MOSI/CAN1_1_RX/TRACE_DATA_1 {6,19} TRACE_DATA_2 P22.2/PWM_32/PWM_33_N/TC_32_TR0/TC_33_TR1/SCB6_RTS/SCB6_SCL/SCB6_CLK/TRACE_DATA_2...

- Page 32 Schematics of CPU Board Figure A-14. LQFP-176 P7 DEFAULT CLOSE HDR_1X2 PROCESSOR POWER On each VDDIO/VSSIO CPU_BB_VDDD pin pair a 10uF and a 0.1uF is required VDDD VSSD VSSD DEFAULT CLOSE CPU_BB_VDDA VDDD VSSD HDR_1X2 10uF_16V 10uF_16V 0.1uF 0.1uF 0.1uF 4.7uF_20V VDDA VSSA...

- Page 33 Schematics of CPU Board Figure A-15. Board to Board Connector- J22A BOARD TO BOARD CONNECTOR This connects to J84 on the TVII Base board J22A BB_USER_BUTTON_4 {11} BB_USER_LED0 {13,18} (12,18,23) BB_SPI0_SS {13} BB_SPI0_CLK {13} GPIO_001 {9} GPIO_002 {9} GPIO_003 {9} GPIO_004 {9} GPIO_005 {9} GPIO_006 {9}...

- Page 34 Schematics of CPU Board Figure A-16. Board to Board Connector- J22B BOARD TO BOARD CONNECTOR Place R100 closer to the Samtec Connector J22 This connects to J84 VBTOB_3.3V VCC_LDO on the TVII Base board VBTOB_3.3V R100 J22B {10,18} BB_CAN6_TXD BB_CAN8_WAKE {10} {10,18} BB_CAN6_RXD BB_CAN9_WAKE {10}...

- Page 35 Schematics of CPU Board Figure A-17. Board to Board Connector- J21A BOARD TO BOARD CONNECTOR Place R1 closer to Samtec Connector J22 VBTOB_5V VCC_PMIC This connects to J38 VBTOB_5V VCC_12V on the TVII Base board J21A BB_USER_LED8 {12} {9,17} BB_CAN1_RXD {9,17} BB_CAN1_TXD {13,16}...

- Page 36 Schematics of CPU Board Figure A-18. Board to Board Connector- J21B BOARD TO BOARD CONNECTOR This connects to J38 J21B on the TVII Base board {8,10,16} BB_LIN2_SLP GPIO_078 {14} {10} BB_LIN3_RX GPIO_077 {14} {10} BB_LIN3_TX GPIO_076 {14} {12} BB_LIN3_WAKE GPIO_075 {14} {10,17} BB_LIN3_SLP GPIO_074 {14}...

-

Page 37: Component Assembly On Cpu Board

Component Assembly on CPU Board This appendix shows the top and bottom assembly of the PCB. Figure B-1. Top Assembly of the PCB ART FILM - PASSY TPS1 TPS2 TPS3 TPS4 TPS6 TPS7 PRIMARY_ASSEMBLY CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. 002-29049 Rev. **... - Page 38 Component Assembly on CPU Board Figure B-2. Bottom Assembly of the PCB CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. 002-29049 Rev. **...

-

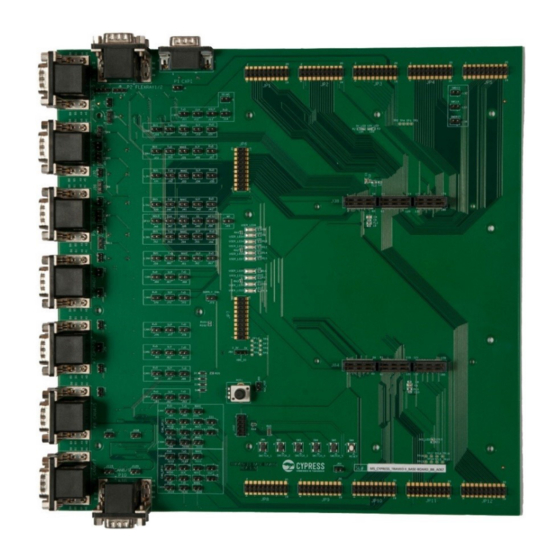

Page 39: Schematics Of Base Board

Schematics of Base Board This appendix contains the schematics of the Base board on which CPU Board is mounted. CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. 002-29049 Rev. **... - Page 40 Schematics of Base Board Figure C-1. Block Diagram of Base Board BOARD TO BOARD CONNECTORS (QTH-090-03-L-D-A) USER LED’S PUSH-BUTTON POWER INPUTS (12V, 5V & 3.3V) FROM CPU OR ADAPTER BOARD TRAVEO II EVM BASE BOARD CYPRESS SEMICONDUCTOR CYPRESS SEMICONDUCTOR CYPRESS SEMICONDUCTOR 198 CHAMPION COURT 198 CHAMPION COURT 198 CHAMPION COURT...

- Page 41 Schematics of Base Board Figure C-2. BTOB Connector-01 BTOB CONNECTOR-01 P_3V3 J84A J84B BB_USER_BUTTON_4 16,17 BB_USER_LED0 16,18 CAN6_TXD CAN8_WAKE 9,17 CAN6_RXD SPI0_SS 15,17 CAN9_WAKE 9,17 SPI0_CLK 15,17 CAN5_TXD 7,17 CAN5_RXD 7,17 CAN7_TXD CAN7_RXD BB_EXP1_GPIO_1 CAN4_TXD 7,17 BB_EXP1_GPIO_2 CAN4_RXD 7,17 BB_EXP1_GPIO_3 CAN8_TXD BB_EXP1_GPIO_4 CAN8_RXD...

- Page 42 Schematics of Base Board Figure C-3. BTOB Connector-02 BTOB CONNECTOR-02 P_5V P_12V J38A J38B 6,17 CAN1_RXD BB_EXP2_GPIO_6 BB_USER_LED8 16,17 11,17 LIN2_SLP BB_EXP2_GPIO_1 11,17 LIN3_RXD BB_EXP2_GPIO_7 6,17 CAN1_TXD 6,17 CAN1_S BB_EXP2_GPIO_2 11,17 LIN3_TXD BB_EXP2_GPIO_8 6,17 CAN0_RXD 11,17 LIN3_WAKE BB_EXP2_GPIO_9 BB_EXP2_GPIO_10 6,17 CAN0_TXD BB_USER_LED9 16,17...

- Page 43 Schematics of Base Board Figure C-4. CAN-FD_0 to 3 CAN_FD_0 CAN_FD_1 VDD_IO VDD_IO CON_DSUB_9_MM CON_DSUB_9_MM HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 22uF_20V 0.1uF 22uF_20V Default Closed 0.1uF Default Closed CAN0_TXD_W CAN0_H_W CAN0_H CAN1_TXD_W CAN1_H_W CAN1_H 5,17 CAN0_TXD 5,17 CAN1_TXD CANH CANH CAN0_RXD_W CAN0_L_W CAN0_L CAN1_RXD_W...

- Page 44 Schematics of Base Board Figure C-5. CAN-FD_4 to 7 CAN_FD_4 CAN_FD_5 VDD_IO VDD_IO CON_DSUB_9_MM CON_DSUB_9_MM HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 22uF_20V 22uF_20V Default Closed 0.1uF Default Closed 0.1uF CAN4_TXD_W CAN4_H_W CAN4_H CAN5_TXD_W CAN5_H_W CAN5_H R117 0E R112 0E 4,17 CAN4_TXD 4,17 CAN5_TXD CANH CANH...

- Page 45 Schematics of Base Board Figure C-6. CAN-FD_6 & 7 CAN_FD_6 CAN_FD_7 VCC_5V VDD_IO VBAT VCC_5V VDD_IO VBAT CON_DSUB_9_MM CON_DSUB_9_MM J109 HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 Default Closed Default Closed CAN6_TXD_W CAN6_H_W CAN6_H CAN7_TXD_W CAN7_H_W CAN7_H R126 0E R129 0E CAN6_TXD CAN7_TXD CANH CANH CAN6_RXD_W...

- Page 46 Schematics of Base Board Figure C-7. CAN-FD_8 & 9 CAN_FD_8 CAN_FD_9 VCC_5V VDD_IO VBAT VCC_5V VDD_IO VBAT CON_DSUB_9_MM CON_DSUB_9_MM J113 J112 J131 J114 HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 Default Closed Default Closed CAN8_TXD_W CAN8_H_W CAN8_H CAN9_TXD_W CAN9_H_W CAN9_H R140 0E R137 0E CAN8_TXD CAN9_TXD CAN8_RXD_W...

- Page 47 Schematics of Base Board Figure C-8. LIN INTERFACE_0 to 1 LIN0_INTERFACE LIN1_INTERFACE HDR_1X2 HDR_1X2 CON_DSUB_9_MM Default Closed Default Closed CON_DSUB_9_MM VBAT VBAT LIN_VS LIN_VS 1N4002-T 1N4002-T LIN0_BUS LIN1_BUS VDD_IO 22uF_20V 22uF_20V 0.1uF VDD_IO 0.1uF Default Open Default Open 4.7K_1% HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2...

- Page 48 Schematics of Base Board Figure C-9. LIN INTERFACE_2 to 3 LIN2_INTERFACE LIN3_INTERFACE HDR_1X2 HDR_1X2 CON_DSUB_9_MM Default Closed CON_DSUB_9_MM VBAT Default Closed VBAT LIN_VS LIN_VS 1N4002-T 1N4002-T LIN2_BUS LIN3_BUS VDD_IO VDD_IO 22uF_20V 22uF_20V 0.1uF 0.1uF Default Open Default Open 4.7K_1% HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2...

- Page 49 Schematics of Base Board Figure C-10. LIN INTERFACE_4 to 5 LIN4_INTERFACE LIN5_INTERFACE HDR_1X2 HDR_1X2 CON_DSUB_9_MM CON_DSUB_9_MM Default Closed VBAT Default Closed VBAT LIN_VS LIN_VS 1N4002-T 1N4002-T LIN4_BUS LIN5_BUS VDD_IO VDD_IO 22uF_20V 22uF_20V 0.1uF 0.1uF Default Open Default Open HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 4.7K_1%...

- Page 50 Schematics of Base Board Figure C-11. Flexray-01 & RESET FLEXRAY INTERFACE -01 RESET VDD_IO VDD_IO VBAT Place C67, C68, C69 &C70 close to pin 0.1uF FRA_TXD_W FRA_ERRN_W FRA_TXD FRA_ERRN ERRN FRA_RXD_W CON_DSUB_9_MM FRA_RXD FRA_INH_W FRA_INH FRA_TXEN_W FRA_TXEN TXEN FRA_BP_W RXEN FRA_BM_W FRA_BGE BB_RST_NP...

- Page 51 Schematics of Base Board Figure C-12. Flexray-02 & INH FLEXRAY INTERFACE-02 SUPPLY_INH HDR_1X2 VDD_IO Default Closed VDD_IO VBAT 4.7K_1% Place C72, C73, C74 & C75 close to pin SUPPLY_INH_W LIN0_INH SUPPLY_INH 5,17 1N4148W-7-F FRB_TXD_W FRB_ERRN_W FRB_TXD FRB_ERRN LIN1_INH ERRN FRB_RXD_W CON_DSUB_9_MM 1N4148W-7-F FRB_RXD...

- Page 52 Schematics of Base Board Figure C-13. CXPI, EEPROM & POT HDR_1X2 CXPI_INTERFACE EEPROM INTERFACE CXPI_VS Default Closed VBAT VDD_IO 1N4002-T VDD_IO 22uF_20V 1N4148W-7-F 0.1uF CON_DSUB_9_M HDR_1X2 HDR_1X2 4.7K_1% HDR_1X2 HDR_1X2 HDR_1X2 HDR_1X2 Default Closed Default Closed 10uF 0.1uF Default closed CXPI_TXD_W CXPI_BUS 5,17...

- Page 53 Schematics of Base Board Figure C-14. USER_LED & PUSHBUTTON USER_LED INTERFACE NOTE: 5-RED & 5-GREEN LED COLOR BB_USER_LED0_W BB_USER_LED4_W LTST-C150GKT LTST-C150GKT 4,18 BB_USER_LED0 5,18 BB_USER_LED4 BB_USER_LED1_W BB_USER_LED5_W LD10 LTST-C150GKT LTST-C150GKT 5,18 BB_USER_LED1 5,18 BB_USER_LED5 BB_USER_LED2_W BB_USER_LED6_W LD11 LTST-C150GKT LTST-C150GKT 5,18 BB_USER_LED2 5,18 BB_USER_LED6...

- Page 54 Schematics of Base Board Figure C-15. Pin Header Section-01 PIN HEADER SECTION -01 VCC_3V3 VCC_5V VCC_3V3 VCC_5V JP10 BB_PWM_2 BB_PWM_1 UART1_RX UART1_TX BB_PWM_4 BB_PWM_3 UART1_CTS UART1_RTS BB_PWM_6 BB_PWM_5 CAN2_RXD CAN2_TXD BB_ADC_2 BB_PWM_7 CAN_SPI1_SS1 CAN_SPI1_SS0 BB_ADC_4 BB_ADC_3 CAN2_S CAN_SPI1_SS2 BB_ADC_6 BB_ADC_5 CAN4_S CAN3_S BB_ADC_8...

- Page 55 Schematics of Base Board Figure C-16. Pin Header Section-02 PIN HEADER SECTION -02 VCC_5V VCC_3V3 VCC_5V VCC_3V3 DEBUG_GPIO_5 SPI2_MISO DEBUG_GPIO_6 SPI2_MOSI UART0_RX UART0_CTS DEBUG_GPIO_7 SPI2_CLK UART0_RTS UART0_TX 5 DEBUG_GPIO_8 SPI2_SS 5,16 BB_USER_LED7 BB_USER_LED5 5,16 DEBUG_GPIO_9 CAN3_TXD DEBUG_GPIO_10 CAN3_RXD 5,16 BB_USER_LED3 BB_USER_LED1 5,16 5,15...

-

Page 56: Component Assembly On Base Board

Component Assembly on Base Board This appendix shows the top and bottom assembly of the PCB. Figure D-1. Top Assembly of the PCB ART FILM - TASY J132 J133 J134 LD1 LD2 LD10 LD11 LD12 R101 R102 J100 J103 J106 J104 J105 LD13... - Page 57 Component Assembly on Base Board Figure D-2. Bottom Assembly of the PCB ART FILM - BASY C 1 1 C 1 6 R 3 4 R 3 3 R 5 8 R 6 2 R 6 3 R 6 7 R 6 8 R 7 2 R 7 3...

-

Page 58: Revision History

Revision History Document Revision History Document Title: CYTVII-B-E-2M-176-CPU Evaluation Board User Guide Document Number: 002-29049 Revision ECN# Issue Date Description of Change 6742894 12/09/2019 New user guide for TVII CPU board. CYTVII-B-E-2M-176-CPU Evaluation Board User Guide, Document Number. 002-29049 Rev. **...

Need help?

Do you have a question about the Cypress CYTVII-B-E-2M-176-CPU and is the answer not in the manual?

Questions and answers