Chapters

Table of Contents

Summary of Contents for Texas Instruments CC2538

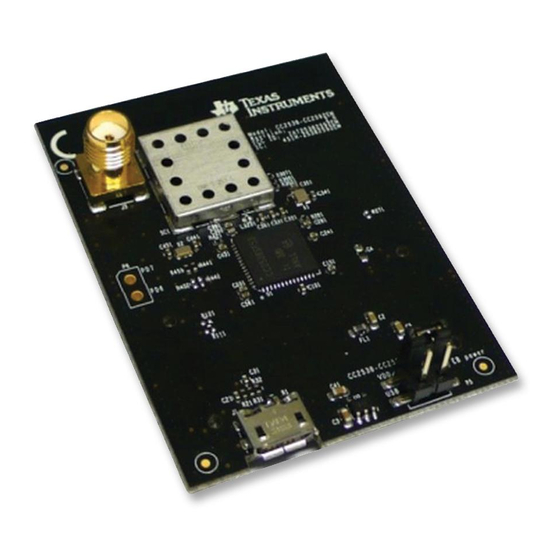

- Page 1 Public Version CC2538 System-on-Chip Solution for 2.4-GHz IEEE 802.15.4 and ZigBee®/ZigBee IP® Applications Texas Instruments CC2538™ Family of Products Version B User's Guide Literature Number: SWRU319B April 2012 – Revised April 2013...

- Page 2 WARNING: EXPORT NOTICE Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S.

-

Page 3: Table Of Contents

The Cortex-M3 Processor Introduction ......................Block Diagram ........................Overview ..................2.3.1 System-Level Interface ................. 2.3.2 Integrated Configurable Debug ..................2.3.3 Trace Port Interface Unit SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 4 3.2.4.1.2 Updating an MPU Region Using Multiple-Word Writes ....................3.2.4.1.3 Subregions ..............3.2.4.2 MPU Access Permission Attributes ..........3.2.4.2.1 MPU Configuration for a CC2538 Microcontroller ..................... 3.2.4.3 MPU Mismatch ....................... Register Map ................... SysTick Register Descriptions ....................NVIC Register Descriptions ............

- Page 5 Power-On Reset and Brownout Detector .................... 7.4.3 Clock Loss Detector ....................Emulator in Power Modes ....................Chip State Retention ................7.6.1 CRC Check on State Retention SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 6 9.3.1.1.2 GPIO Instances Register Mapping Summary ..............9.3.1.2 GPIO Common Register Descriptions ....................9.3.2 IOC Registers ..............9.3.2.1 IOC Registers Mapping Summary Contents SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 7 General-Purpose Timers ....................11.1 General-Purpose Timers ......................11.2 Block Diagram ....................11.3 Functional Description ..................11.3.1 GPTM Reset Conditions ....................11.3.2 Timer Modes SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 8 13.4.1.1 SMWDTHROSC Registers Mapping Summary ..............13.4.1.2 SMWDTHROSC Register Descriptions ......................Watchdog Timer ......................14.1 Watchdog Timer ..................... 14.2 Watchdog Timer Registers ................... 14.2.1 SMWDTHROSC Registers Contents SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 9 18.4.4.2 Flow Control ............18.4.4.2.1 Hardware Flow Control (RTS and CTS) ..................... 18.4.5 LIN Support ....................18.4.5.1 LIN Master ....................18.4.5.2 LIN Slave SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 10 19.4.2.1 Transmit FIFO ..................... 19.4.2.2 Receive FIFO ......................19.4.3 Interrupts ....................19.4.4 Frame Formats ..........19.4.4.1 Texas Instruments Synchronous Serial Frame Format ................19.4.4.2 Freescale SPI Frame Format ................19.4.4.2.1 SPO Clock Polarity Bit ................19.4.4.2.2 SPH Phase Control Bit .........

- Page 11 22.1.1 Terms and Conventions Used in this Manual ....................22.1.1.1 Acronyms ................22.1.1.2 Formulae and Nomenclature ......................22.1.2 Overview ....................22.1.2.1 Feature List SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 12 22.2.1.1.2 Key Store .................. 22.2.1.1.3 AES Crypto Engine ................22.2.1.1.4 SHA-256 Hash Engine ..............22.2.1.1.5 Master Control and Interrupts ................... 22.2.1.1.6 Debug Capabilities Contents SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 13 22.2.5.2.1 Regular use ................. 22.2.5.2.2 Interrupting DMA Transfers ............22.2.5.2.3 Interrupts and HW/SW Synchronization ....................22.2.5.3 Hashing ............... 22.2.5.3.1 Data Format and Byte Order SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 14 22.4.2.1 PKA Registers Mapping Summary ................22.4.2.2 PKA Register Descriptions ..........................Radio ........................23.1 RF Core ......................23.1.1 Interrupts ..................... 23.1.2 Interrupt Registers Contents SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 15 23.10 RX FIFO Access ................ 23.10.1 Using the FIFO and FIFOP Signals ....................23.10.2 Error Conditions ......................23.10.3 RSSI ..................23.10.4 Link Quality Indication SWRU319B – April 2012 – Revised April 2013 Contents Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 16 23.14.9.33 ISSTART ....................23.14.9.34 ISRXON ..................23.14.9.35 ISRXMASKBITSET ..................23.14.9.36 ISRXMASKBITCLR ....................23.14.9.37 ISTXON .................... 23.14.9.38 ISTXONCCA ..................23.14.9.39 ISSAMPLECCA ....................23.14.9.40 ISRFOFF Contents SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 17 SmartRF™ Studio Software for Evaluation (www.ti.com/smartrfstudio) .................. TIMAC Software (www.ti.com/timac) ................Z-Stack™ Software (www.ti.com/z-stack) ........................Abbreviations ...................... Additional Information ................. Texas Instruments Low-Power RF Web Site ..................Low-Power RF Online Community ............. Texas Instruments Low-Power RF Developer Network ..................... Low-Power RF eNewsletter ........................References ......................

- Page 18 19-3. TI Synchronous Serial Frame Format (Continuous Transfer) ..........19-4. Freescale SPI Format (Single Transfer) With SPO = 0 and SPH = 0 List of Figures SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 19 23-4. Format of the Frame Control Field (FCF) ................... 23-5. Frame Data Written to the TX FIFO ........................23-6. TX Flow SWRU319B – April 2012 – Revised April 2013 List of Figures Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 20 23-19. FFT of the Random Bytes ........23-20. Histogram of 20 Million Bytes Generated With the RANDOM Instruction ....................23-21. Running a CSP Program List of Figures SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 21 TEX, S, C, and B Bit Field Encoding ................3-4. Cache Policy for Memory Attribute Encoding ..................... 3-5. AP Bit Field Encoding ............3-6. Memory Region Attributes for a CC2538 Microcontroller ....................3-7. Peripherals Register Map ......................4-1. Memory Map ....................4-2.

- Page 22 22-8. ExpMod Result Vector/Scratchpad Area Memory Allocation ............ 22-9. ExpMod Scratchpad Area / Input Vector Overlap Restrictions ..............22-10. Required PKA RAM Sizes for Exponentiations List of Tables SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 23 22-56. Valid Combinations for CTRL_ALG_SEL Flags ..................22-57. Master Control Algorithm Select ......................22-58. Software Reset ....................22-59. Interrupt Configuration SWRU319B – April 2012 – Revised April 2013 List of Tables Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 24 ..............23-2. Frame Filtering and Source Matching Memory Map ............... 23-3. IEEE 802.15.4-2006 Symbol-to-Chip Mapping ..................... 23-4. FSM State Mapping List of Tables SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 25 .................. 23-8. RFCORE_FFSM Register Summary .................. 23-9. RFCORE_XREG Register Summary ................... 23-10. CCTEST Register Summary ..................23-11. ANA_REGS Register Summary SWRU319B – April 2012 – Revised April 2013 List of Tables Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 26: Preface

SWRU319B – April 2012 – Revised April 2013 Read This First About This Document This user's guide provides information on how to use the CC2538 and describes the functional blocks of the system-on-chip (SoC) designed around the ARM® Cortex™-M3 core and an IEEE 802.15.4 radio. Audience This manual is intended for system software developers, hardware designers, and application developers. - Page 27 (see SIGNAL and SIGNAL below). Change the value of the signal from the logically True state to deassert a signal the logically False state. SWRU319B – April 2012 – Revised April 2013 Read This First Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 28 TI’s ZigBee PRO stack Z-Stack™ with associated profiles and the ZigBee IP stack with Smart Energy 2.0 profile. The usage is, however, not limited to these protocols alone. The CC2538 is, for example, also suitable for 6LoWPAN and wireless HART implementations.

- Page 29 After each register description, a table summarizes all hyperlinked register calls. To navigate in the PDF documents, see Acrobat Reader Tips. SWRU319B – April 2012 – Revised April 2013 Read This First Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 30 Beginning or end of two or more simultaneous operations Flow Line Lines indicate the sequence of steps and the direction of flow. Read This First SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 31 Click the Go To Previous View button or the Go To Next View button. NOTE: This navigation tip is useful to return to your previous view after clicking on a register call hyperlink. SWRU319B – April 2012 – Revised April 2013 Read This First Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 32: Architectural Overview

SWRU319B – April 2012 – Revised April 2013 Architectural Overview The CC2538 device family provides solutions for a wide range of applications. To help the user develop these applications, this user's guide focuses on the use of the different building blocks of the CC2538 device family. -

Page 33: Target Applications

Public Version Target Applications www.ti.com Target Applications The CC2538 family is positioned for low-power wireless applications such as: • IEEE 802.15.4 Radio Networks • ZigBee Smart Energy 1.x and to 2.0 profiles • Home and building automation • Intelligent lighting systems •... -

Page 34: Cc2538 Block Diagram

Power-on reset and brown-out MAC timer detection Low-power RF chain comparator Modulator Demod 12-bit ADC With Temp Sensor Figure 1-1. CC2538 Block Diagram Architectural Overview SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 35 CC2538 device to a low-power state during extended periods of inactivity. A power-up and power-down sequencer, a 32-bit sleep timer (which is a real-time clock [RTC]) with interrupt and 16KB of RAM with retention in all power modes positions the CC2538 microcontroller perfectly for battery applications.

-

Page 36: Functional Overview

1.3.1.2 Memory Map A memory map lists the location of instructions and data in memory. The memory map for the CC2538 can be found in the Memories section of this User's Guide. Register addresses are given as a hexadecimal increment, relative to the base address of the module as shown in the memory map. -

Page 37: Nested Vector Interrupt Controller

The following sections describe the on-chip memory modules. 1.3.2.1 SRAM The CC2538 provides a 16KB block of single-cycle on-chip SRAM with full retention in all power modes. In addition, some variants offer an additional 16KB of single-cycle on-chip SRAM without retention in the lowest power modes. -

Page 38: Rom

1.3.2.3 The ROM is preprogrammed with a serial boot loader (SPI or UART). For applications that require in-field programmability, the royalty-free CC2538 boot loader can act as an application loader and support in-field firmware updates. 1.3.3 Radio The CC2538 device family provides a highly integrated low-power IEEE 802.15.4-compliant radio transceiver. -

Page 39: Mac Timer

A watchdog timer is used to regain control when a system fails due to a software error or because an external device does not respond in the expected way. When enabled by software, the watchdog timer must be cleared periodically; otherwise, the watchdog timer resets the CC2538 device when it times out. 1.3.5.3... -

Page 40: System Control And Clock

1.3.7 System Control and Clock System control determines the overall operation of the CC2538 device. System control provides information about the CC2538 device, controls power-saving features, controls the clocking of the CC2538 device and individual peripherals, and handles reset detection and reporting. -

Page 41: Serial Communications Peripherals

Universal serial bus (USB) is a serial bus standard designed to allow peripherals to be connected and disconnected using a standardized interface. The CC2538 device supports the USB 2.0 FS configuration in device mode and has the following features: •... -

Page 42: I 2 C

Both the I C master and slave can generate interrupts. The CC2538 microcontroller includes an I C module with the following features: •... -

Page 43: Ssi

FIFO contains four entries 1.3.9 Programmable GPIOs GPIO pins offer flexibility for a variety of connections. The CC2538 GPIO module is comprised of four GPIO blocks, each corresponding to an individual GPIO port. The GPIO module supports CC2538 programmable I/O pins. The number of GPIOs available depends on the peripherals being used (see Chapter 5 for the signals available to each GPIO pin). -

Page 44: Adc

An analog comparator is a peripheral that compares two analog voltages, two external pin inputs, and provides a logical output that signals the comparison result. The CC2538 microcontroller provides an independent integrated and low-power analog comparator that can be active in all power modes. The comparator output is mapped into the digital I/O port, and the MCU can treat the comparator output as a regular digital input. -

Page 45: The Cortex-M3 Processor

........................... Topic Page ..............The Cortex-M3 Processor Introduction ....................Block Diagram ......................Overview ..................Programming Model ..................Instruction Set Summary SWRU319B – April 2012 – Revised April 2013 The Cortex-M3 Processor Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 46: The Cortex-M3 Processor Introduction

32-MHz operation • 1.25 DMIPS/MHz The CC2538 builds on this core to bring high-performance 32-bit computing to cost-sensitive embedded microcontroller applications, such as factory automation and control, industrial control power devices, building and home automation, and stepper motor control. This chapter provides information on the CC2538 implementation of the Cortex-M3 processor, including the programming model, the memory model, the exception model, fault handling, and power management. -

Page 47: Overview

The Cortex-M3 processor closely integrates a nested vector interrupt controller (NVIC) to deliver industry- leading interrupt performance. The CC2538 NVIC includes a nonmaskable interrupt (NMI) and provides eight interrupt priority levels. The tight integration of the processor core and NVIC provides fast execution of interrupt service routines (ISRs), dramatically reducing interrupt latency. -

Page 48: Trace Port Interface Unit

This section describes the Cortex-M3 programming model. In addition to the descriptions of the individual core registers, information about the processor modes and privilege levels for software execution and stacks is included. The Cortex-M3 Processor SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 49: Processor Mode And Privilege Levels For Software Execution

N/A (not applicable) and there is no offset. SWRU319B – April 2012 – Revised April 2013 The Cortex-M3 Processor Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 50: Cortex-M3 Register Set

Cortex general-purpose register 10 Purpose Register 10 (R10). Cortex General- – – Cortex general-purpose register 11 Purpose Register 11 (R11). The Cortex-M3 Processor SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 51: Register Descriptions

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 DATA SWRU319B – April 2012 – Revised April 2013 The Cortex-M3 Processor Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 52 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 DATA Bits Field Name Description Type Reset 31:0 DATA Register data — SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 53 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 DATA SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 54 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 DATA Bits Field Name Description Type Reset 31:0 DATA Register data — SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 55 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 LINK Bits Field Name Description Type Reset 31:0 LINK This field is the return address. 0xFFFF FFFF SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 56: Psr Register Combinations

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 Q ICI / IT RESERVED ICI / IT ISRNUM SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 57 For more information, see Section 5.2.4. The value of this bit is meaningful only when accessing PSR or EPSR. 23:16 RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 58 Interrupt vector 54 0x47- Reserved 0x7F For more information, see Section 5.1.2. The value of this field is meaningful only when accessing PSR or IPSR. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 59 Prevents the activation of all exceptions except for NMI. No effect. The processor clears the FAULTMASK bit on exit from any exception handler except the NMI handler. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 60 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 RESERVED SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 61: Exceptions And Interrupts

{Rd,} Rn , #imm12 N, Z, C, V Rd, label Load PC-relative address – AND, ANDS {Rd,} Rn, Op2 Logical AND N, Z, C SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 62 N, Z, C Multiply with accumulate, 32-bit Rd, Rn, Rm, Ra – result Multiply and subtract, 32-bit Rd, Rn, Rm, Ra – result SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 63 Store register signed halfword – STRT Rt, [Rn {, #offset}] Store register word – SUB, SUBS {Rd,} Rn, Op2 Subtract N, Z, C, V SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 64 Zero extend a byte – UXTH {Rd,} Rm {,ROR #n} Zero extend a halfword – – Wait for event – – Wait for interrupt – SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 65: Cortex™-M3 Peripherals

........................... Topic Page ..............Cortex™-M3 Peripherals Introduction ..................Functional Description ....................Register Map ................SysTick Register Descriptions ................NVIC Register Descriptions SWRU319B – April 2012 – Revised April 2013 Cortex™-M3 Peripherals Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 66: Cortex™-M3 Peripherals Introduction

Public Version Cortex™-M3 Peripherals Introduction www.ti.com Cortex™-M3 Peripherals Introduction This chapter provides information on the CC2538 implementation of the Cortex-M3 processor peripherals, including: • System timer (SysTick) (see SysTick): Provides a simple, 24-bit clear-on-write, decrementing, wrap-on- zero counter with a flexible control mechanism. -

Page 67: Nvic

The NVIC detects that the interrupt signal is asserted and the interrupt is not active. • The NVIC detects a rising edge on the interrupt signal. SWRU319B – April 2012 – Revised April 2013 Cortex™-M3 Peripherals Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 68: Scb

Section 4.1.1). Table 3-2 shows the possible MPU region attributes. For guidelines for programming a microcontroller implementation, see MPU Configuration for a CC2538 Microcontroller. Cortex™-M3 Peripherals SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 69: Updating An Mpu Region

MPU settings. • After MPU setup, if it includes memory transfers that must use the new MPU settings. SWRU319B – April 2012 – Revised April 2013 Cortex™-M3 Peripherals Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 70: Updating An Mpu Region Using Multiple-Word Writes

1 apply to the first 128-KB region, configure the SRD field for region 2 to 0x03 to disable the first two subregions, as Figure 3-1 shows. Cortex™-M3 Peripherals SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 71: Mpu Access Permission Attributes

TEX, C, B, and S access permission bits. All encodings are shown for completeness; however, the current implementation of the Cortex-M3 does not support the concept of cacheability or shareability. For information on programming the MPU for CC2538 implementations, see MPU Configuration for a CC2538 Microcontroller. -

Page 72: Mpu Configuration For A Cc2538 Microcontroller

Read-only, by privileged or unprivileged software 3.2.4.2.1 MPU Configuration for a CC2538 Microcontroller CC2538 microcontrollers have only a single processor and no caches. As a result, the MPU should be programmed as shown in Table 3-6. Table 3-6. Memory Region Attributes for a CC2538 Microcontroller In current CC2538 microcontroller implementations, the shareability and cache policy attributes do not affect the system behavior. -

Page 73: Peripherals Register Map

0x0000 0000 Interrupt 64–95 Active Interrupt 64–95 Active Bit (ACTIVE2) 0x30C ACTIVE3 0x0000 0000 Interrupt 96–127 Active Interrupt 96–127 Active Bit (ACTIVE3) SWRU319B – April 2012 – Revised April 2013 Cortex™-M3 Peripherals Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 74 PRI35 0x0000 0000 Interrupt 140–143 Interrupt 140–143 Priority (PRI35) Priority 0x490 PRI36 0x0000 0000 Interrupt 144–147 Interrupt 144–147 Priority (PRI36) Priority Cortex™-M3 Peripherals SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 75: Systick Register Descriptions

Size Alias 3 3 (MPUATTR3) SysTick Register Descriptions This section lists and describes the System Timer registers, in numerical order by address offset. SWRU319B – April 2012 – Revised April 2013 Cortex™-M3 Peripherals Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 76 RESERVED Reserved 0x000 CLK_SRC Clock source Value Description External reference clock (not implemented for CC2538 microcontrollers) System clock Because an external reference clock is not implemented, this bit must be set in order for SysTick to operate. INTEN Interrupt enable...

-

Page 77: Nvic Register Descriptions

Ensure that software uses correctly aligned register accesses. The processor does not support unaligned accesses to NVIC registers. An interrupt can enter the pending state even if it is disabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 78: Interrupt Enable

On a read, indicates the interrupt is enabled. On a write, enables the interrupt. A bit can be cleared only by setting the corresponding INT[n] bit in the DIS1 register. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 79 On a read, indicates the interrupt is enabled. On a write, enables the interrupt. A bit can be cleared only by setting the corresponding INT[n] bit in the DISn register. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 80 On a read, indicates the interrupt is enabled. On a write, clears the corresponding INT[n] bit in the EN0 register, disabling interrupt [n]. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 81 On a read, indicates the interrupt is enabled. On a write, clears the corresponding INT[n] bit in the EN2 register, disabling interrupt [n] SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 82 On a read, indicates the interrupt is enabled. On a write, clears the corresponding INT[n] bit in the EN4 register, disabling interrupt [n] SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 83 If the corresponding interrupt is already pending, setting a bit has no effect. A bit can be cleared only by setting the corresponding INT[n] bit in the UNPEND1 register. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 84 If the corresponding interrupt is already pending, setting a bit has no effect. A bit can be cleared only by setting the corresponding INT[n] bit in the UNPEND3 register. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 85 PEND0 register, so that interrupt [n] is no longer pending. Setting a bit does not affect the active state of the corresponding interrupt. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 86 PEND2 register, so that interrupt [n] is no longer pending. Setting a bit does not affect the active state of the corresponding interrupt. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 87 PEND4 register, so that interrupt [n] is no longer pending. Setting a bit does not affect the active state of the corresponding interrupt. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 88 Reset 31:0 Interrupt active 0x0000 0000 Value Description The corresponding interrupt is not active. The corresponding interrupt is active, or active and pending. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 89 Reset 31:0 Interrupt active 0x0000 0000 Value Description The corresponding interrupt is not active. The corresponding interrupt is active, or active and pending. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 90 (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. 28:24 RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 91 (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. 20:16 RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 92 (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. 12:8 RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 93 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 94 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 95 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 96 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 97 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 98 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 99 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 100 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 101 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 102 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 103 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 104 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 105 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 106 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 107 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 108 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 109 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 110 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 111 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 112 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 113 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 114 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 115 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 116 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 117 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 118 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 119 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 120 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 121 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 122 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 123 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 124 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 125 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 126 [4n], where n is the number of the Interrupt Priority register (n=0 for PRI0, and so on). The lower the value, the greater the priority of the corresponding interrupt. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 127: System Control Block (Scb) Register Descriptions

RESERVED Bits Field Name Description Type Reset 31:3 RESERVED Reserved 0x0000 0000 DISFOLD Disable IT folding Value Description No effect Disables IT folding SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 128 Description 0xC23 Cortex-M3 processor. Revision number Value Description The pn value in the rnpn product revision identifier; for example, the 0 in r2p0. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 129 On a read, indicates a SysTick exception is pending. On a write, changes the SysTick exception state to pending. This bit is cleared by writing 1 to the PENDSTCLR bit. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 130 Description There are preempted active exceptions to execute. There are no active exceptions, or the currently executing exception is the only active exception. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 131 [7:5] INTx field showing the binary point. An x denotes a group priority field bit, and a y denotes a subpriority field bit. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 132 This field is used to guard against accidental writes to this register. 0x05FA must be written to this field to change the bits in this register. On a read, 0xFA05 is returned. ENDIANESS Data endianness The CC2538 implementation uses only little-endian mode so this is cleared to 0. 14:11 RESERVED Reserved...

- Page 133 ISR. Setting this bit enables an interrupt-driven application to avoid returning to an empty main application. RESERVED Reserved SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 134 Unaligned LDM, STM, LDRD, and STRD instructions always fault regardless of whether UNALIGNED is set. Reserved Reserved MAINPEND Allow main interrupt trigger SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 135 This field configures the priority level of the memory management fault. Configurable priority values are in the range 0–7, with lower values having higher priority. RESERVED Reserved SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 136 This field configures the priority level of debug. Configurable priority values are in the range 0–7, with lower values having higher priority. RESERVED Reserved 0x00 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 137 MEMP Memory management fault pending Value Description A memory management fault exception is not pending. A memory management fault exception is pending. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 138 Caution above before setting this bit. MEMA Memory management fault active Value Description Memory management fault is not active. Memory management fault is active. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 139 Value Description No unaligned access fault has occurred, or unaligned access trapping is not enabled. The processor has made an unaligned memory access. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 140 The value in the Bus Fault Address (FAULTADDR) register is not a valid fault address. The FAULTADDR register is holding a valid fault address. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 141 This bit is cleared by setting it to 1. IBUS Instruction bus error R/W1C Value Description An instruction bus error has not occurred. An instruction bus error has occurred. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 142 Value Description An instruction access violation has not occurred. The processor tried an instruction fetch from a location that does not permit execution. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 143 When this bit is set, the PC value stacked for the exception return points to the instruction that was preempted by the exception. This bit is cleared by setting it to 1. RESERVED Reserved SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 144: Mpu Register Descriptions

This section lists and describes the MPU registers, in numerical order by address offset. The MPU registers can be accessed only from privileged mode. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 145 Indicates there are eight supported MPU data regions. RESERVED Reserved 0x00 SEPARATE Separate or unified MPU Value Description Indicates the MPU is unified. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 146 The MPU is enabled during hard fault, NMI, and FAULTMASK handlers. When the MPU is disabled and this bit is set, the resulting behavior is unpredictable. ENABLE MPU enable SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 147 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 ADDR REGION SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 148 The MPUNUMBER register is updated with the value of the REGION field and the base address is updated for the region specified in the REGION field. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 149 On a write, contains the value to be written to the MPUNUMBER register. On a read, returns the current region number in the MPUNUMBER register. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 150 Maximum possible size occupies the complete memory map. This refers to the N parameter in the MPUBASE register (see MPU Region Base Address (MPUBASE)). SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 151 The SIZE field defines the size of the MPU memory region specified by the MPUNUMBER register. For more information, see Example SIZE Field Values. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 152 For information on using this bit field, see Table 3-5. 23:22 RESERVED Reserved 21:19 Type extension mask For information on using this bit field, see Table 3-3. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 153 Maximum possible size occupies the complete memory map. This refers to the N parameter in the MPUBASE register (see MPU Region Base Address (MPUBASE)). SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 154 The SIZE field defines the size of the MPU memory region specified by the MPUNUMBER register. For more information, see Example SIZE Field Values. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 155 For information on using this bit field, see Table 3-5. 23:22 RESERVED Reserved 21:19 Type extension mask For information on using this bit field, see Table 3-3. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 156 MPUNUMBER register. For more information, see Example SIZE Field Values. ENABLE Region enable Value Description The region is disabled. The region is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 157: Memory Map

SWRU319B – April 2012 – Revised April 2013 Memory Map This chapter describes the memory map..........................Topic Page ....................Memory Model SWRU319B – April 2012 – Revised April 2013 Memory Map Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 158: Memory Model

The processor has a fixed memory map that provides up to 4GB of addressable memory. Table 4-1 provides the memory map for the CC2538 controller. In this manual, register addresses are given as a hexadecimal increment, relative to the base address of the module, as shown in the memory map. -

Page 159: Memory Regions, Types, And Attributes

An additional memory attribute is Execute Never (XN), which means the processor prevents instruction accesses. A fault exception is generated only when an instruction is executed from an XN region. SWRU319B – April 2012 – Revised April 2013 Memory Map Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 160: Memory System Ordering Of Memory Accesses

For more information on memory types and the XN attribute, see Section 4.1.1, Memory Regions, Types, and Attributes. CC2538 devices may have reserved memory areas within the address ranges listed in Table 4-2... -

Page 161: Bit-Banding

A word access to a bit-band address results in a word access to the underlying memory, and similarly for halfword and byte accesses. This allows bit-band accesses to match the access requirements of the underlying peripheral. SWRU319B – April 2012 – Revised April 2013 Memory Map Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 162: Sram Memory Bit-Banding Regions

The alias word at 0x2200 001C maps to bit 7 of the bit-band byte at 0x2000 0000: 0x2200 001C = 0x2200 0000 + (0*32) + (7*4) Memory Map SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 163: Directly Accessing An Alias Region

(LSByte) of a word stored at the lowest-numbered byte, and the most-significant byte (MSByte) stored at the highest-numbered byte. Figure 4-2 shows how data is stored. SWRU319B – April 2012 – Revised April 2013 Memory Map Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 164: Synchronization Primitives

Load-Exclusive instruction. The processor removes its exclusive access tag if one of the following conditions occurs: • The processor executes a CLREX instruction. Memory Map SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 165 An exception occurs, which means the processor can resolve semaphore conflicts between different threads. For more information about the synchronization primitive instructions, see the Cortex-M3 Instruction Set Technical User's Manual. SWRU319B – April 2012 – Revised April 2013 Memory Map Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 166: Interrupts

SWRU319B – April 2012 – Revised April 2013 Interrupts This chapter describes the interrupts..........................Topic Page ....................Exception Model ....................Fault Handling Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 167: Exception Model

The CC2538 has 48 interrupts that are spread across a range of 147 possible ARM® Cortex™-M3 interrupt inputs in a regular interrupt map setting. - Page 168 In the system, peripherals use interrupts to communicate with the processor. Table 5-2 lists the interrupts on the CC2538 controller. For an asynchronous exception, other than reset, the processor can execute another instruction between when the exception is triggered and when the processor enters the exception handler.

-

Page 169: Interrupts

GPTimer 0B 0x0000 0094 GPTimer 1A 0x0000 0098 GPTimer 1B 0x0000 009C GPTimer 2A 0x0000 00A0 GPTimer 2B 0x0000 00A4 Analog Comparator SWRU319B – April 2012 – Revised April 2013 Interrupts Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 170 0x0000 0158 Reserved 0x0000 015C Reserved 0x0000 0160 Reserved 0x0000 0164 Reserved 0x0000 0168 Reserved 0x0000 016C Reserved 0x0000 070 Reserved 170 Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 171 Reserved 0x0000 0274 Reserved 0x0000 0278 Reserved 0x0000 027C Reserved 0x0000 0280 Reserved 0x0000 0284 Reserved 0x0000 0288 Reserved 0x0000 028C Reserved SWRU319B – April 2012 – Revised April 2013 Interrupts Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 172: Exception Handlers

The least-significant bit (LSB) of each vector must be 1, indicating that the exception handler is Thumb code. ® Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 173: Exception Priorities

Interrupt 0–3 Priority (PRI0). Configurable priority values for the CC2538 implementation are in the range 0 to 7. NOTE: This means that the Reset and Hard fault exceptions, with fixed negative priority values, always have higher priority than any other exception. -

Page 174: Interrupt Priority Grouping

This operation is referred to as stacking and the structure of eight data words is referred to as stack frame. Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 175: Exception Return

Reserved Return to Thread mode. 0xFFFF FFF9 Exception return uses state from MSP. Execution uses MSP after return. 0xFFFF FFFA–0xFFFF FFFC Reserved SWRU319B – April 2012 – Revised April 2013 Interrupts Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 176: Fault Handling

Attempting to use an instruction set other than the Thumb instruction set, or returning to a non load-store-multiple instruction with ICI continuation. 176 Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 177: Fault Status And Fault Address Registers

Bus Fault Address (FAULTSTAT) Bus fault (BFAULTSTAT) (FAULTADDR) Bus Fault Address (FAULTADDR) Usage Fault Status Configurable Fault Status Usage fault – (UFAULTSTAT) (FAULTSTAT) SWRU319B – April 2012 – Revised April 2013 Interrupts Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 178: Lockup

That is, an pended interrupt can occur as soon as the PKA interrupt is enabled, even when the PKA is busy. The PKA ISR can test bit 15 of the PKA_FUNCTION register to confirm that the PKA interrupt is actually active. Interrupts SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 179: Jtag Interface

Switching Debug Interface from 2-pin cJTAG to 4-pin JTAG ..................Debugger Connection ..................Primary Debug Support ............Debug Access Security Through ICEPick ..................CM3 Debug Interrupt SWRU319B – April 2012 – Revised April 2013 JTAG Interface Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 180: Test/Debug System Top Level Diagram

TCK signal is low. Logic inside the chip maintains the signal level while the TCK signal is high. JTAG Interface SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 181: Ieee 1149.7 Features Subset

The TMS sequence from Run-Test-Idle is (1 1 0 0*n 1 1 1 0 1 0) for the IR shift to end in Pause DR. The TMS sequence from Pause DR to Pause DR is (1 1 1 0 1 0) (Done twice). SWRU319B – April 2012 – Revised April 2013 JTAG Interface Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 182 TDO. No additional steps are required by the user to have TDI and TDO mapped as GPIO. Previous configurations of PB6 and PB7 will be overridden. JTAG Interface SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 183: Debugger Connection

On the device, CM3 is the only debug TAP connected to the ICEPick. The CM3 DAP can be accessed using ICEPick with secondary debug TAP 0 ID. SWRU319B – April 2012 – Revised April 2013 JTAG Interface Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 184: Primary Debug Support

Following 0x0E IR, the data register read (DR) reflects status of various activities related to the flash mass erase command. Table 6-4 shows the description. JTAG Interface SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 185: Data Register Description For Instruction 0X0E(Read Only)

1 - Assert an interrupt to CM3 (pulling the signal high) 0 - De-assert interrupt to CM3 (pulling the signal down) SWRU319B – April 2012 – Revised April 2013 JTAG Interface Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 186: System Control

SWRU319B – April 2012 – Revised April 2013 System Control The system control module configures the overall operation of the CC2538 device. Configurable features include reset control, power control, clock control, and low-power modes. Low-power operation is enabled through different operating modes (power modes). Ultralow-power operation is obtained by turning off the power supply to modules to avoid static (leakage) power consumption and also by using clock gating and turning off oscillators to reduce dynamic power consumption. -

Page 187: Power Management

This section describes how to manage the different power saving actions. 7.1.1 Control Inputs to Power Management CC2538 has different configuration registers and an initiator (WFI instruction) for control of operational (i.e power) modes. 7.1.1.1 Clock Gating Registers The description of the clock gating registers for each peripheral are found in the register section (see ). -

Page 188: Flow Diagram For Operational Modes

Sequencing time Functional limitations Active Clock gating with RCGC None None Sleep Clock gating with SCGC Enter: immediate CPU in sleep 188 System Control SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 189: Sequencing When Using Power Modes

7.1.2.3.2. 7.1.2.1 Sequencing when using Power Modes When using power management in CC2538 it is important to understand the sequence of events and timing involved in the process. A simple flow diagram for power management is shown in Figure 7-2. As can be seen from the figure PM1, 2 and 3 are always entered from a state where the CPU is running on 16 MHz RCOSC. -

Page 190: Simple Flow Diagram For Power Management

Active mode to PM1, PM2 or PM3. As seen in Figure 7-2 the power down sequence to PM1, PM2 and PM3 from Active mode always System Control SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 191: Enter Power Mode When Running On 16 Mhz System Clock

WFI was asstered. Figure 7-3 show an example of a sequence when CC2538 is in Active mode running on 32 MHz system clock, until the chip has entered PM1, PM2 or PM3. SWRU319B – April 2012 – Revised April 2013... -

Page 192: Timing Example For Transition From 32 Mhz To Pm's

After calibration is finished both clock sources are running and a switch from 32 MHz to 16 MHz can start and will occur immediately (~0.3us). System Control SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 193: Exit From Power Modes

PM2 and PM3 the required time for restore that is driven by 16 MHz clock (approx 30us) will be saved. 7.1.2.4.2 32 MHz Qualification Time In the CC2538 an additional module for detection of 32 MHz XOSC stability is available. Enabling this feature adds approx 20 us to the 32 MHz XOSC startup time, see 7.2.1 for details. -

Page 194: Simplified Figure Of Current Consumption In Pm1

PM3 is the most effective power saving mode but can only wake up from pin interrupts (Sleep Mode Timer is disabled) System Control SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 195: Block Diagram Oscillators And Clocks

Figure 7-6. Block Diagram Oscillators and Clocks 7.2.1 High Frequency Oscillators Figure 7-6 gives an overview of the clock system with available clock sources on the CC2538 device. Two high-frequency oscillators are present in the device: • 32 MHz crystal oscillator •... -

Page 196: Mhz Rcosc Calibration

32 MHz XOSC (such as the radio) are started. In the CC2538, an additional module for detection of 32 MHz XOSC stability is available. This amplitude detector can be useful in environments with significant noise on the power supply to ensure that the clock source is not used until the clock signal is stable. -

Page 197: Clock Gate Matrix

Forcing the RESET_N input pin low • A POR condition • A brownout reset (BOD) condition • Watchdog timer reset condition SWRU319B – April 2012 – Revised April 2013 System Control Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 198: Reset Of Peripherals

Clock-loss detetector is disabled. During reset, the GPIO pins are configured as inputs with pull-up. In the CC2538, a system reset can be generated immediately in software by writing the NVIC_APINT_SYSRESETREQ bit to '1' in the NVIC_APINT register (see Application Interrupt and Reset Control (APINT) for the register description). -

Page 199: Sys_Ctrl Register Summary

During entry/exit to/from PM2 and PM3 the device state is stored during power down and read back during power up are CRC checked. A feature to automatically reset the CC2538 in the case of a CRC error can be enabled by setting bit CRC_REN_RF and CRC_REN_USB to '1' in the SRCRC register. - Page 200 0x400D 2080 SYS_CTRL_CLD 0x0000 003F 0x94 0x400D 2094 SYS_CTRL_IWE 0x0000 0000 0x98 0x400D 2098 SYS_CTRL_I_MAP 0x0000 0000 0xA8 0x400D 20A8 SYS_CTRL_RCGC 200 System Control SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 201: Sys_Ctrl Register Descriptions

Instance SYS_CTRL Description The clock control register handels clock settings in the CC2538. The settings in CLOCK_CTRL do not always reflect the current chip status which is found in CLOCK_STA register. Type 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10... - Page 202 1: A change of system clock source has been initiated and is not finished. Same as when OSC bit in CLOCK_STA and CLOCK_CTRL register are not equal SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 203 0: Clock for GPT2 is gated. 1: Clock for GPT2 is enabled. GPT1 0: Clock for GPT1 is gated. 1: Clock for GPT1 is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 204 0: Clock for GPT1 is gated. 1: Clock for GPT1 is enabled. GPT0 0: Clock for GPT0 is gated. 1: Clock for GPT0 is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 205 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 RESERVED SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 206 0: SSI1 module is not reset 1: SSI1 module is reset SSI0 0: SSI0 module is not reset 1: SSI0 module is reset SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 207 Reset 31:2 RESERVED This bit field is reserved. 0x0000 0000 UART1 0: Clock for UART1 is gated. 1: Clock for UART1 is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 208 Reset 31:1 RESERVED This bit field is reserved. 0x0000 0000 I2C0 0: Clock for I2C0 is gated. 1: Clock for I2C0 is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 209 0: Clock for AES is gated. 1: Clock for AES is enabled. 0: Clock for PKA is gated. 1: Clock for PKA is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 210 0x0000 0000 0: AES module is not reset 1: AES module is reset 0: PKA module is not reset 1: PKA module is reset SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 211 This bit field is reserved. CRC_REN_RF 1: Enable reset of chip if CRC fails. 0: Disable reset feature of chip due to CRC. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 212 This bit field is reserved. 0x00 0: CLD is disabled. 1: CLD is enabled. Writing to this register shall be ignored if VALID = 0 SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 213 This bit field is reserved. 0x0000 0000 ALTMAP 1: Select alternate interrupt map. 0: Select regular interrupt map. (See the ASD document for details.) SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 214 RESERVED This bit field is reserved. 0x0000 0000 RFC0 0: Clock for RF CORE is gated. 1: Clock for RF CORE is enabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 215 0 --> Does not override any power mode settings from SYSREGS and does not prohibit system to go into any power down modes. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 216 0 --> Does not override any power mode settings from SYSREGS and does not prohibit system to go into any power down modes. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 217: Internal Memory

Flash Page Erase ......Flash Lock Bit Page and Customer Configuration Area (CCA) .................... Flash Mass Erase ..................... ROM Sub System ......................SRAM SWRU319B – April 2012 – Revised April 2013 Internal Memory Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 218: Introduction

Introduction The CC2538 family contains flash memory up to 512 kB for storage of program code. The flash memory is programmable from the user software and through the debug interface. The flash controller handles writing and erasing the embedded flash memory. The embedded flash memory consists of up to 256 pages of 2048 bytes each. -

Page 219: Example Write Sequence

1 are ignored. Only the bits written 0 are set to 0, whereas all bits FFFFFFF written 1 are ignored. SWRU319B – April 2012 – Revised April 2013 Internal Memory Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 220: Dma Flash Write

DMA channel is configured and how a DMA transfer is initiated to write a block of data from a location in SRAM to flash memory. Internal Memory SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 221: Flash Write Using Dma

To write to the flash using the CPU, a program executing from SRAM must implement the steps outlined in the procedure described in Section 8.3.1. Disable interrupts to ensure the operation does not time out. SWRU319B – April 2012 – Revised April 2013 Internal Memory Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 222: Flash Size Configuration

The following code example of how to erase one flash page in the CC2538 is given for use with the IAR compiler: unsigned char erase_page_num = 3;... -

Page 223: Upper 32 Bytes Of Lock Bit Page And Cca Layout

Back door configuration 2006 Reserved Reserved for future use 2005 Reserved Reserved for future use 2004 Reserved Reserved for future use SWRU319B – April 2012 – Revised April 2013 Internal Memory Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 224: Fields At Por/ Reset

0 - Backdoor and boot loader disable Level Sets active level for selected pin on pad A 1 - Active High 0 - Active Low 224 Internal Memory SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 225: Layout Of Byte 2007

NOTE: If the Enable bit is set to 0 in the CCA area of the Lock Bit page, the CC2538 ROM boot loader ignores any received boot loader commands, even if no application image is present in the flash memory. -

Page 226: Icepick Tap State

This reflects the command issued to the flash controller for the mass erase 1 - Command issued 0 - Command is not issued 226 Internal Memory SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 227: Rom Sub System

Data can also be transferred to and from the SRAM using the micro direct memory access controller (μDMA). The internal SRAM of the CC2538 is located at 0x2000 0000 of the device memory map, and has the following features: •... -

Page 228: Flash_Ctrl Register Summary

0x400D 3014 FLASH_CTRL_DIE CFG0 0x0000 0000 0x18 0x400D 3018 FLASH_CTRL_DIE CFG1 0x0000 2000 0x1C 0x400D 301C FLASH_CTRL_DIE CFG2 8.9.1.1.2 FLASH_CTRL Register Descriptions Internal Memory SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... - Page 229 FCTL.BUSY is 1. If FCTL.ERASE is set simultaneously with this bit, the erase operation is started first, then the write is started. SWRU319B – April 2012 – Revised April 2013 Internal Memory Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 230 1 to the FCTL.WRITE bit. New 32-bit data is written only if FCTL.FULL = 0. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

- Page 231 Description These settings are a function of the FLASH information page bit settings, which are programmed during production test, and are subject for specific configuration for multiple device flavors of cc2538. Type 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10...

- Page 232 These settings are a function of the FLASH information page bit settings, which are programmed during production test, and are subject for specific configuration for multiple device flavors of cc2538. The DIE_*_REVISION registers are an exeception to this, as they are hardwired and are not part of the FLASH information page.

- Page 233 Public Version SRAM www.ti.com Bits Field Name Description Type Reset PKA_EN 1: PKA is enabled. 0: PKA is permanently disabled. SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated...

-

Page 234: General-Purpose Inputs/Outputs

This chapter describes the input/output (I/O) control and the general-purpose inputs/outputs (GPIOs)..........................Topic Page ...................... I/O Control ......................GPIO ................. I/O Control and GPIO Registers General-Purpose Inputs/Outputs SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 235: Pheripheral Signal Select Values (Same For All Ioc_Pxx_Sel Registers)

SSI1 FSS OUT SSI1 TX_SER OUT I2C SDA I2C SCL GPT0CP1 GPT0CP2 GPT1CP1 0x10 GPT1CP2 0x11 GPT2CP1 0x12 GPT2CP2 0x13 GPT3CP1 0x14 GPT3CP2 SWRU319B – April 2012 – Revised April 2013 General-Purpose Inputs/Outputs Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 236: Gpio

GPIO pins can function as I/O signals for the on-chip peripheral modules. For information on how to setup GPIO pins to be used for alternate hardware (i.e., peripheral) functions, see Section 9.2.2.3. General-Purpose Inputs/Outputs SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 237: Digital I/O Pads (The Diagram Shows One Of 32 Possible I/O Pins)

The data control register is only valid when the AF register selects GPIO not the alternate function. SWRU319B – April 2012 – Revised April 2013 General-Purpose Inputs/Outputs Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 238: Gpiodata Write Example

GPIO Interrupt Both Edges (GPIO_IBE) register • GPIO Interrupt Event (GPIO_IEV) register Interrupts are enabled and disabled through the GPIO Interrupt Enable (GPIO_IE) register. General-Purpose Inputs/Outputs SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 239: Power-Up Interrupt

GPIO_AFSEL register, then it is first necessary to unlock the commit register, as described above, and write the desired protection bits. SWRU319B – April 2012 – Revised April 2013 General-Purpose Inputs/Outputs Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 240: Pad Configuration Override Registers

On reset all bits in the IOC_Pxx_OVER registers are set to 0, except for the PUE bits. This means that at reset all GPIO pads are set as inputs and are pulled up. General-Purpose Inputs/Outputs SWRU319B – April 2012 – Revised April 2013 Submit Documentation Feedback Copyright © 2012–2013, Texas Instruments Incorporated... -

Page 241: Configuration