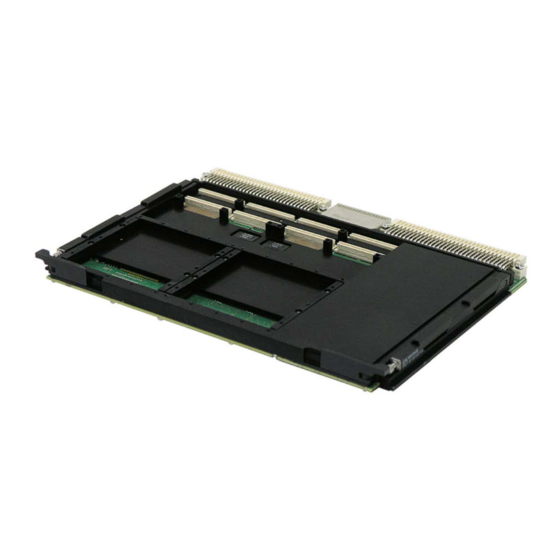

User Manuals: abaco systems PPC11A Rugged VME Computer

Manuals and User Guides for abaco systems PPC11A Rugged VME Computer. We have 1 abaco systems PPC11A Rugged VME Computer manual available for free PDF download: Hardware Reference Manual

abaco systems PPC11A Hardware Reference Manual (159 pages)

6U VME

Brand: abaco systems

|

Category: Motherboard

|

Size: 2 MB

Table of Contents

-

1 Unpacking

16 -

-

Inspection19

-

-

-

Introduction26

-

Features29

-

Sdram33

-

NOR Flash33

-

Nvsram35

-

-

I/O39

-

Ethernet40

-

Usb43

-

Sata44

-

Gpio44

-

Mil-Std-155346

-

Graphics47

-

Mezzanines48

-

I 2 C Buses55

-

Main Bus55

-

I 2 C Bus 357

-

I 2 C Reset57

-

DIP Switches58

-

-

Timers60

-

AXIS Timer61

-

Fpga64

-

Jtag65

-

Leds66

-

-

-

-

6 Connectors

112-

-

PMC Connectors119

-

XMC Connectors123

-

-

Product Codes130

-

-

-

Software Support131

-

Boot Firmware131

-

Built in Test131

-

-

I/O Modules132

-

Test Access Card132

-

-

-

Volatile Memory133

-

-

-

Ppc4A135

-

P0 Connector135

-

P1 Connector136

-

P2 Connector137

-

-

Ppc7A139

-

P0 Connector139

-

P1 Connector140

-

P2 Connector141

-

-

Ppc7D143

-

P0 Connector143

-

P1 Connector145

-

P2 Connector146

-

-

Ppc10A148

-

P0 Connector148

-

P1 Connector150

-

P2 Connector151

-

-

-

Advertisement