Table of Contents

Advertisement

Quick Links

MA35D1 BSP

NuMicro

®

Family

Arm

®

Cortex

®

-A35-based Microprocessor

MA35D1 BSP

User Manual

The information described in this document is the exclusive intellectual property of

Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

®

Nuvoton is providing this document only for reference purposes of NuMicro

microcontroller and

microprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

Jan. 03, 2023

Page 1 of 25

Rev 1.02

Advertisement

Table of Contents

Summary of Contents for Nuvoton NuMicro MA35D1 BSP

- Page 1 MA35D1 BSP User Manual The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. ® Nuvoton is providing this document only for reference purposes of NuMicro microcontroller and microprocessor based system design.

-

Page 2: Table Of Contents

MA35D1 BSP Table of Contents 1 OVERVIEW ...................... 3 2 BSP FEATURES ....................4 2.1 Supported Platforms ..................... 4 2.2 BSP Contents ......................... 4 2.3 Repositories ........................5 3 DEVELOPMENT BOARD SETUP ..............6 3.1 Power on Setting ......................6 3.2 Hardware Connection .................... -

Page 3: Overview

MA35D1 BSP OVERVIEW The MA35D1 series microprocessor is based on a poweful Armv8-A architecture dual-core ARM ® Cortex-A35 with TrustZone , which features 32 KB I-cache, 32 KB D-cache, and 512 KB L2 Cache. The internal 64/32-bit CPU core operates up to 1 GHz supporting secure boot. The MA35D1 also embeds a ARM Cortex-M4 processor core running at 180 MHz with 16 KB / 16 KB I and D Cache for expansible system DRAM access, Floating Point Unit, Memory Protect Unit and a dedicated 128 KB SRAM for code excuting. -

Page 4: Bsp Features

MA35D1 BSP BSP FEATURES This BSP supports Linux operating system for MA35D1. The peripheral drivers are also included in the BSP allowing applications to access them. The image reside at EL3 as secure monitor is BL31 from Trusted Firmware-A (TF-A), which is included. And this BSP includes OP-TEE to provide the secure service provided in secure EL1. -

Page 5: Repositories

MA35D1 BSP for MA35D1. Pin Tool A pin configuration tool that can generate dts file for MA35D1. NuEclipse Includes a series of Eclipse plug-ins and tools. The plug-ins allow the user to create, build, and debug ARM-based projects within the Eclipse framework Table 2-1 BSP Content List Repositories The following lists the repositories holds the MA35D1BSP source code. -

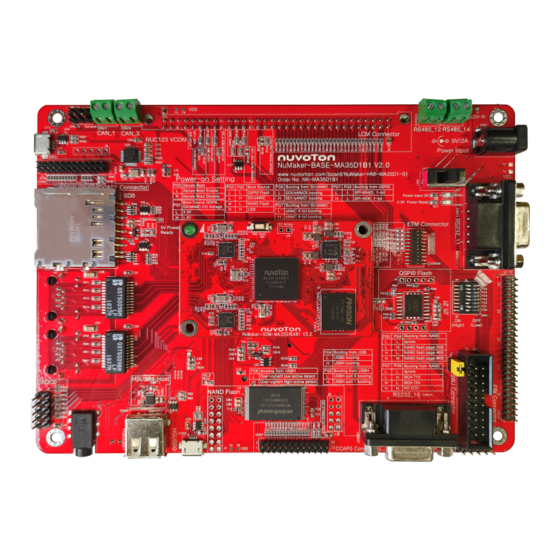

Page 6: Development Board Setup

MA35D1 BSP DEVELOPMENT BOARD SETUP Power on Setting There are several boot options can be decided by power on setting of MA35D1. For example, the boot source, ECC bit to use, SD interface selection, etc. Table 3-1 lists the power on setting for MA35D1. The power on setting should be set according to the boot scenario desired before reset or power on the system. -

Page 7: Hardware Connection

MA35D1 BSP Hardware Connection All boards manufactured by Nuvoton come alone with two USB device ports. One for download firmware and the other is VCOM for debugging. NuWriter tool comes alone with GUI and command line interface provided for firmware download. Please refer to MA35D1 NuWriter User Manual for the usage of NuWriter tool. - Page 8 MA35D1 BSP Figure 3-2 Setup Serial Port Figure 3-3 Select Port Number For engineers to develop on a native Linux machine where, Putty could be an alternative for Tera Term which does not support Linux platform. To use putty, first launch it and select the connection interface.

- Page 9 MA35D1 BSP Figure 3-4 Select Connection Jan. 03, 2023 Page 9 of 25 Rev 1.02...

-

Page 10: Ice Interface

Some of the platforms provide JTAG interface which could be used to debug Cortex-A35 or Cortex- M4. This is a 20-pin socket with fool-proof connector on EVB board as shown in Figure 3-6. Users could use Nuvoton Nu-Link2 Pro, J&D Tech CodeViser, or other debugger supports CoreSight SoC- 400. - Page 11 MA35D1 BSP Figure 3-6 ICE Interface Jan. 03, 2023 Page 11 of 25 Rev 1.02...

-

Page 12: Development Environment Setup

MA35D1 BSP DEVELOPMENT ENVIRONMENT SETUP This section describes the steps to build up the BSP dev elopement environment without using Yocto or Buildroot. Please refer to MA35D1 Yocto User Manual or MA35D1 Buildroot User Manual for setting up the development environment using Yocto or Buildroot. Linux Development Environment Except for Coretx-M4 bare-metal firmware, the development environment in based on Linux system. -

Page 13: Coretx-M4 Firmware Development Environment

MA35D1 BSP Figure 4-2 Linaro Tool Chain Download Selection Coretx-M4 firmware Development Environment Keil uVision, IAR Embedded Workbench, and NuEclipse are used as bare metal firmware development environment. NuEclipse supports both Windows ® and Linux operating system while Keil uVision and IAR Embedded Workbench are available on Windows ®... -

Page 14: Ma35D1 Boot Source

Power-On-Setting and OTP. To setup an USB connection between MA35D1 and computer, Nuvoton provides a tool named NuWriter. This tool first loads a system initial firmware to MA35D1, and then send a second firmware named xusb.bin to take over the USB connection and storage access on MA35D1 after the system initial firmware finish execution. -

Page 15: Boot From Nand Flash

MA35D1 BSP Start USBD USB boot USBH Initial USB Host Initial USB Device EHCI Connect to Read header 0 (sector 2) Read header 1 (sector 3) Download DDR Initial DRAM Check header fail match Download xusb.bin SD backup (update firmware) to Load new header enabled DRAM... - Page 16 MA35D1 BSP Start Enable NAND Page size 2KB + 64 ECC–BCH8 Read ONFI ONFI supported? Get NAND Device ID Supported ID? Ignore outside setting? (page size / ECC) Use outside setting Set Page size Set ECC Read header 0 (block 0~3) Read header 1 (block 0~3) Check header...

-

Page 17: Boot From Spi Nand Flash

MA35D1 BSP Boot from SPI NAND Flash The MA35D1 supports booting from SPI NAND Flash using QSPI0 interface. Compared to parallel NAND Flash, SPI NAND uses less pins to connect with microprocessors. So microprocessors can save the pins for other purpose. Depending on the Power-On-Setting and OTP, IBR can set the SPI clock to 50 MHz or 30 MHz and read data from SPI Flash using 1-bit mode or quad mode. -

Page 18: Boot From Spi Nor Flash

MA35D1 BSP Start Enable QSPI clock Set 1-bit MFP Set QSPI clock (OTP) QSPI control setting Reset NAND (0xff) busy Read header 0 (block 0~3) ready one page data Get status Read 512 bytes (0xf) Read header 1 (block 0~3) one page data Check R/B# status Read 512 bytes... -

Page 19: Boot From Emmc And Sd Card

MA35D1 BSP Start Enable QSPI clock Set 1-bit MFP Set QSPI clock (OTP) QSPI control setting Read header 0 (offset 0) 512 bytes by 1-bit mode Read header 1 (offset 0x1000) 512 bytes by 1-bit mode Check header fail match Load new header 4-bit mode images... -

Page 20: Backup Boot From Sd0 Interface

MA35D1 BSP Start SDH boot Enable SD0 clock Enable SD1 clock Set SD0 MFP Set SD1 MFP Set SD0 clock to 200kHz Set SD1 clock to 200kHz Configure SD0 Configure SD1 Is SDHC / SD / eMMC? Set SD clock to 20MHz SD0 setting (data width, Unknown block size) -

Page 21: Booting Prebuild Images

MA35D1 BSP BOOTING PREBUILD IMAGES The MA35D1 BSP contains pre-built images for different hardware. Please refer to this section for the procedures to load prebuild images to different hardware and bring up the system. SOM Board The MA35D1 evaluation board supports booting from several storage devices. Each boot source required different images to bring up the system. -

Page 22: Boot From Nand Flash

MA35D1 BSP glibc/deploy/images/numaker-som-ma35d16a81 directory. 6.1.3 Boot from NAND Flash Configure the PG[3:2] = 10b (SW4[3] ON, SW4[4] OFF), the IBR will read images from NAND Flash. The packed binary file “core-image-buildroot-ma35d1-som-256m.rootfs.nand” in Buildroot is used for NAND Flash boot. This file is put at MA35D1_Buildroot/output/images directory. The packed binary file “nvt-image-qt5-numaker-som-ma35d16a81-yyyymmddhhmmss.rootfs.nand”... -

Page 23: Boot From Nand Flash

MA35D1 BSP Yocto is used for SD card boot. The file is put at build/tmp-glibc/deploy/images/numaker-iot- ma35d16f70 directory. 6.2.3 Boot from NAND Flash Configure the PG[3:2] = 00b, (SW1[2] ON, SW1[3] OFF), the IBR will read images from NAND Flash. The packed binary file “core-image-buildroot-ma35d1-iot-128m.rootfs.nand” in Buildroot is used for NAND boot. -

Page 24: Revision History

MA35D1 BSP REVISION HISTORY Date Revision Description 2022.03.02 1.00 Initial version. Changed Yoctol and Build output image. 2022.05.28 1.01 Updated board pictures. Updated out-of-date figures and added hyper link to 2023.01.03 1.02 reference document Jan. 03, 2023 Page 24 of 25 Rev 1.02... - Page 25 MA35D1 BSP Important Notice Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, “Insecure Usage”.

Need help?

Do you have a question about the NuMicro MA35D1 BSP and is the answer not in the manual?

Questions and answers