Summary of Contents for AMD -K6-2/450 - MHz Processor

- Page 1 ® Embedded AMD-K6™ Processors BIOS Design Guide Application Note Publication # 23913 Rev: A Amendment/0 Issue Date: November 2000...

- Page 2 Trademarks AMD, the AMD logo, and combinations thereof, AMD-K6, 3DNow!, E86, AMD PowerNow!, and Super7 are trademarks, and FusionE86 is a service mark of Advanced Micro Devices, Inc. MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

-

Page 3: Table Of Contents

AMD-K6™E Embedded Processor ..... . . 3 AMD-K6™-2 Processor....... . . 3 AMD-K6™-2E Embedded Processor. - Page 4 Sample Code ........67 New AMD-K6™ Processor Instructions......68 Additional Considerations .

- Page 5 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Software Timing Dependencies Relative to Memory Controller Setup ........69 Pipelining Support .

- Page 6 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Contents...

- Page 7 (Models 9 and D) ....... . 39 Figure 11. L2 Cache Organization (AMD-K6™-III Processor) ..40 Figure 12.

- Page 8 23913A/0—November 2000 Figure 20. L2 Tag or Data Location (AMD-K6™-2E+ Processor)—EDX ....... . 50 Figure 21.

- Page 9 Summary by Register of MSR Differences within the AMD-K6™ Family....... . 14 Table 8.

- Page 10 (Low-Power Model D)......56 Table 28. CPUID Functions in AMD-K6™ Processors... 60 Table 29.

-

Page 11: Revision History

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Revision History Date Description November 2000 Initial public release. Revision History... - Page 12 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Revision History...

-

Page 13: Introduction

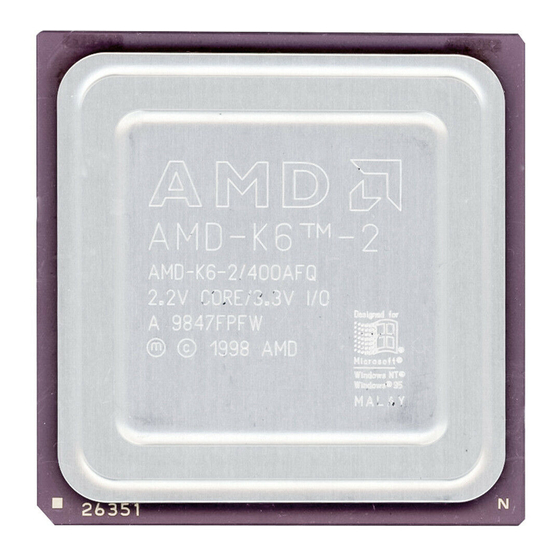

This document highlights the BIOS modifications required to fully support the AMD-K6™ processors used by AMD’s embedded customers. The information in this application note pertains to the following processors in the AMD-K6 family: AMD-K6E embedded processor AMD-K6-2 processor AMD-K6-2E embedded processor... -

Page 14: Processor Models And Steppings

MSRs are defined identically. 4. Low-power versions implement one additional register to support AMD PowerNow!™ technology. 5. AMD PowerNow! technology is supported on low-power versions of these processors only. The descriptions in the remainder of this section provide more... -

Page 15: Amd-K6™E Embedded Processor

8/ 0, 8/ 1, 8/ 2, 8/ 3, 8 /4, 8 /5 , 8/6 , or 8/7 . Model 8/[ 7: 0] is manufactured in the 0.25-micron process and was the original version of the AMD-K6-2 available as a desktop product. Model 8/[7:0] implements the same six MSRs as the Model 7, and the bits and fields within these six MSRs are defined identically. -

Page 16: Amd-K6™-2E Embedded Processor

AMD-K6™-2E+ Embedded Processor In addition to supporting the 3DNow! instruction set and a 100- MHz processor bus, the AMD-K6-2E+ processor contains a 128- Kbyte backside L2 cache. It also supports the 3DNow! DSP instructions extensions. Low-power versions of the processor support AMD PowerNow!™... -

Page 17: Amd-K6™-Iii Processor

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 AMD-K6™-III Processor In addition to supporting the 3DNow! instruction set and a 100- MHz processor bus, the AMD-K6-III processor contains a 256- Kbyte backside L2 cache. Model 9/[3:0] Model 9/[3:0] is any of four possible model/steppings—models 9/0, 9/1, 9/2, or 9/3. -

Page 18: Bios Consideration Checklist

Use the Time Stamp Counter (TSC) to ‘clock’ a timed operation and compare the result to the real-time clock (RTC) to determine the operating frequency. See the CPU Speed Determination Program available on the AMD website at http://www.amd.com/products/cpg/bin/. Display the recommended BIOS boot string as shown in Table 5 on page 11. -

Page 19: Cache Testing

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Cache Testing The AMD-K6 family of processors does not contain MSRs to allow for testing of the L1 cache. However, the AMD-K6-2E+, AMD-K6-III, and AMD-K6-IIIE+ processors do contain an MSR that allows for testing of their L2 caches. This MSR is called L2AAR, and it is described in “Level-2 Cache Array... -

Page 20: States After Reset And Init

MSRs are compatible with those of Pentium processors. Differences are listed in Table 2 through Table 4. Table 2. AMD-K6™E Processor (Model 7) and AMD-K6™ Processor (Model 8/[7:0]) State after RESET Register RESET State 0000_05MSh... -

Page 21: Processor State After Init

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Table 4. AMD-K6™-2E+ (Model D), AMD-K6™-III (Model 9), and AMD-K6™-IIIE+ Processors (Model D) State after RESET Register RESET State 0000_05MSh 0000_0000_0000_0002h EFER L2AAR 0000_0000_0000_0000h PFIR 0000_0000_0000_0000h PSOR 0000_0000_0000_00SBh STAR 0000_0000_0000_0000h... -

Page 22: Built-In Self-Test (Bist)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Built-In Self-Test (BIST) Fo r a l l m o d e l s o f t h e A M D -K 6 p ro c e ss o r, B I S T i s run unconditionally following the falling transition of RESET. -

Page 23: Cpuid Identification Algorithms

C P U I D i n s t r u c t i o n , s e e “Embedded AMD Processor Recognition” on page 57. To determine if the processor is enabled with AMD PowerNow! technology, use CPUID function 8000_0007, as described on page 79. -

Page 24: Figure 1. Cpuid Instruction Flow Chart

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Check for CPUID instruction support Execute CPUID Extended Function EAX=8000_0001h Utilize Vendor String and No CPUID instruction-- Extended Function Feature CPUID instruction Use other means bits to determine 3DNow!, supported... -

Page 25: System Management Mode (Smm)

IDT base located at offset FF94h. I/O Trap Dword Differences The I/O trap dword is located at offset FFA4h. Its AMD-K6 processor bit fields are shown in Table 6. This state-save area, which is reserved in Pentium processors, contains information regarding an I/O instruction that may have been trapped by an SMI# assertion. -

Page 26: Model-Specific Registers Overview

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Model-Specific Registers Overview Each of the models of the AMD-K6 processor family support a different set of model-specific registers (MSRs). These differences are summarized by register in Table 7. The differences are summarized by model in Table 8 on page 15, where an ‘X’... -

Page 27: Summary By Model Of Msr Differences Within The

PFIR L2AAR EPMR Notes: 1. There are four MSRs that every model and stepping of the AMD-K6 family of processors support identically—MCAR, MCTR, TR12, and TSC. 2. L2D, EWBEC, and DPE are bits/fields supported in EFER for the indicated models/steppings. All models/steppings support the System Call Extension (SCE) bit in EFER, even if the corresponding SYSCALL and SYSRET instructions and the STAR register are not supported. -

Page 28: Standard Model-Specific Registers (All Models)

Standard Model-Specific Registers (All Models) This section describes the four standard MSRs that every model and stepping of the AMD-K6 family of processors support identically. See the appropriate AMD-K6 or AMD-K6E processor data sheet for more detail on these standard registers. -

Page 29: Model 7 And Model 8/[7:0] Registers

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Model 7 and Model 8/[7:0] Registers The AMD-K6E processor Model 7 and the AMD-K6-2 processor Model 8/[7:0] provide the model-specific registers listed in Table 9. The contents of ECX selects the MSR to be addressed by the RDMSR and WRMSR instruction. -

Page 30: Extended Feature Enable Register (Efer)

SYSRET instructions. Notes: 1. The AMD-K6E processor Model 7 provides the SCE bit in the EFER register, but this bit does not affect processor operation because the SYSCALL and SYSRET instructions and the STAR register are not supported in this models. -

Page 31: Write Handling Control Register (Whcr)

Enable Limit (WAELIM) field, and the Write Allocate Enable 15-to-16-Mbyte (WAE15M) bit. The WHCR register is MSR C000_0082h. AMD-K6 processors contain a split level-1 (L1) 64-Kbyte writeback cache organized as a separate 32-Kbyte instruction cache and a 32-Kbyte data cache with two-way set associativity. -

Page 32: Figure 3. Write Handling Control Register (Whcr)

— “Write to a Cacheable Page” and “Write to a Sector” (for more information, see the “Cache Organization” chapter in the appropriate AMD-K6 or AMD-K6E processor data sheet. The maximum value of this limit is ((2 –1) ·... - Page 33 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 This value (8), when multiplied by 4 Mbytes, yields 32 Mbytes as the write allocate limit. Write Allocate Enable The WAE15M bit is used to enable write allocations for the 15-to-16-Mbyte Field.

-

Page 34: Syscall/Sysret Target Address Register (Star)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 SYSCALL/SYSRET Target Address Register (STAR) Models 8, 9, and D implement the STAR register. This register contains the target EIP address used by the SYSCALL instruction and the 16-bit code and stack segment selector bases used by the SYSCALL and SYSRET instructions. -

Page 35: Model 8/[F:8] Registers

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Model 8/[F:8] Registers The AMD-K6-2 processor Model 8/[F:8] and AMD-K6-2E processor Model 8/[F:8] provides the ten MSRs listed in Table The contents of ECX select the MSR to be addressed by the RDMSR and WRMSR instruction. -

Page 36: Extended Feature Enable Register (Efer)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Extended Feature Enable Register (EFER) The Extended Feature Enable Register (EFER) contains the control bits that enable the extended features of the processor. Figure 5 shows the format of the EFER register, and Table 13 defines the function of each bit of the EFER register. - Page 37 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 buffer operates in conjunction with the Memory Type Range Registers (MTRRs). Refer to “UC/WC Cacheability Control Register (UWCCR)” on page 30 for a description of the MTRRs. Merging multiple write cycles into a single write cycle reduces processor bus utilization and processor stalls, thereby increasing the overall system performance.

-

Page 38: Table 14. Write Ordering And Performance Settings For Efer

In order to achieve the highest level of performance while still maintaining support for the EWBE# signal, AMD recommends that the BIOS set EFER[3:2] to 01b (close-to-best performance). Many uniprocessor systems do not support the EWBE# signal, in which case AMD recommends that the BIOS set EFER[3:2] to 10b or 11b (best performance). -

Page 39: Write Handling Control Register (Whcr)

8/[F:8], 9, and D. AMD-K6 processors contain a split level-1 (L1) 64-Kbyte writeback cache organized as a separate 32-Kbyte instruction cache and a 32-Kbyte data cache with two-way set associativity. -

Page 40: Figure 6. Write Handling Control Register (Whcr)

— “Write to a Cacheable Page” and “Write to a Sector” (for more information, see the “Cache Organization” chapter in the appropriate AMD-K6 or AMD-K6E processor data sheet. The maximum value of this limit is ((2 –1) ·... - Page 41 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Write Allocate Enable The WAE15M bit is used to enable write allocations for the 15-to-16-Mbyte Field memory write cycles that address the 1 Mbyte of memory between 15 Mbytes and 16 Mbytes. This bit must be set to 1 to allow write allocates in this memory area.

-

Page 42: Uc/Wc Cacheability Control Register (Uwccr)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 UC/WC Cacheability Control Register (UWCCR) Models 8/[F:8], 9, and D provide two variable-range Memory Type Range Registers (MTRRs)—MTRR0 and MTRR1—that each specify a range of memory. Each range can be defined as one of the following memory types: Uncacheable (UC) Memory—Memory read cycles are sourced... -

Page 43: Figure 7. Uc/Wc Cacheability Control Register (Uwccr)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Symbol Description Bits Symbol Description Bits Uncacheable Memory Type Uncacheable Memory Type Write-Combining Memory Type Write-Combining Memory Type Physical Base Address 1 Physical Address Mask 1 Physical Base Address 0... -

Page 44: Table 16. Valid Masks And Range Sizes For Uwccr Register

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Memory-Range The following rules regarding the address alignment and size of Restrictions each range must be adhered to when programming the physical base address and physical address mask fields of the UWCCR register: The minimum size of each range is 128 Kbytes. - Page 45 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Examples Suppose that the range of memory from 16 Mbytes to 32 Mbytes is uncacheable, and the 8-Mbyte range of memory on top of 1 Gbyte is writ e-com binable . Range 0 is def ined as t he uncacheable range, and range 1 is defined as the write- combining range.

-

Page 46: Processor State Observability Register (Psor)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Processor State Observability Register (PSOR) Models 8/[F:8], 9, and standard-power versions of Model D provide the Processor State Observability Register (PSOR) as defined in Figure 8. The PSOR register is MSR C000_0087h. -

Page 47: Table 17. Processor-To-Bus Clock Ratios (Models 8/[F:8] And 9)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Table 17. Processor-to-Bus Clock Ratios (Models 8/[F:8] and 9) State of BF[2:0] Processor-Clock to Bus-Clock Ratio 100b 2.5x 101b 3.0x 110b 6.0x 111b 3.5x 000b 4.5x 001b 5.0x 010b 4.0x 011b 5.5x... -

Page 48: Page Flush/Invalidate Register (Pfir)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Page Flush/Invalidate Register (PFIR) Models 8/[F:8], 9, and D contain the Page Flush/Invalidate Register (PFIR) (see Figure 9) that allows cache invalidation and optional flushing of a specific 4-Kbyte page from the linear address space. - Page 49 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 F/I Bit This bit is used to control the type of action that occurs to the specified linear page. If a 0 is written to this bit, the operation is a flush, in which case all cache lines in the modified state within the specified page are written back to memory, after which the entire page is invalidated.

-

Page 50: Model 9 Registers

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Model 9 Registers The AMD-K6-III processor (Model 9) provides the eleven model- specific registers listed in Table 19. The contents of ECX selects the MSR to be addressed by the RDMSR and WRMSR instruction. -

Page 51: Extended Feature Enable Register (Efer)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Extended Feature Enable Register (EFER) Figure 10 shows the format of the EFER register for models 9 and D, and Table 20 defines the function of each bit of the EFER register. -

Page 52: Level-2 Cache Array Access Register (L2Aar)

Models 9 and D provide the L2AAR register that allows for direct access to the L2 cache and L2 tag arrays. The L2 cache in the AMD-K6-III processor is organized as shown in Figure 11: Four 64-Kbyte ways Each way contains 1024 sets... -

Page 53: Figure 12. L2 Cache Sector And Line Organization

Description Selects the desired cache set 15-6 Line Selects Line1 (1) or Line0 (0) Octet Selects one of four octets Dword Selects upper (1) or lower (0) dword Figure 13. L2 Tag or Data Location (AMD-K6™-III Processor)—EDX Model 9 Registers... -

Page 54: Figure 14. L2 Data-Eax

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Table 21. Tag versus Data Selector Instruction Operation (EDX[20]) Read dword from L2 data array into EAX. Dword location RDMSR is specified by EDX. Read tag, line state and LRU information from L2 tag array RDMSR into EAX. -

Page 55: Figure 15. L2 Tag Information (Amd-K6™-Iii Processor)-Eax

10b Used More Recently Than 11b, But Less Recently Than 01b 11b Least Recently Used Figure 16. LRU Byte Writing to L2 Tag of When writing to the L2 tag of the AMD-K6-III processor, special AMD-K6™-III consideration must be given to the least significant bit of the Processor Tag field of the EAX register—... - Page 56 43). It is important to note that this special consideration is only required if the AMD-K6-III processor will subsequently be expected to properly execute instructions or access data from the L2 cache following the setup of the L2 cache by means of the L2AAR register.

-

Page 57: Model D Registers

The contents of ECX selects the MSR to be addressed by the RDMSR and WRMSR instruction. The AMD-K6-2E+ and AMD-K6-IIIE+ processors contain a split Level-1 (L1) 64-Kbyte writeback cache organized as a separate 32-Kbyte instruction cache and a 32-Kbyte data cache with two-way set associativity. -

Page 58: Processor State Observability Register (Psor) (Low-Power Versions)

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Processor State Observability Register (PSOR) (Low-Power Versions) The low-power versions of the AMD-K6-2E+ and AMD-K6-IIIE+ processors provide the Processor State Observability Register (PSOR) as defined in Figure 17. Note: Standard-power versions of Model D support the PSOR as defined on page 34. -

Page 59: Table 23. Processor-To-Bus Clock Ratios (Low-Power Model D)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 NOL2 Bit This read-only bit indicates whether the processor contains an L2 cache. Note: This bit is always set to 0 for Model D. STEP Field This read-only field contains the stepping ID. This is identical to the value returned by CPUID standard function 1 in EAX[3:0]. -

Page 60: Level-2 Cache Array Access Register (L2Aar)

Some information in this section is duplicated to account for the different L2 cache sizes in the AMD-K6-2E+ and AMD-K6-IIIE+ processors. The L2 cache in the AMD-K6-2E+ and AMD-K6-IIIE+ processors is organized as shown in Figure 18: Four 32-Kbyte ways (AMD-K6-2E+ processor) or four 64-... -

Page 61: Figure 19. L2 Cache Sector And Line Organization

EDX register. The EDX register specifies the location of the access, and whether the access is to the L2 cache data or tags (refer to Figure 20 on page 50 for the AMD-K6-2E+ processor and Figure 21 on page 50 for the AMD-K6-IIIE+ processor). -

Page 62: Figure 21. L2 Tag Or Data Location

Selects Line1 (1) or Line0 (0) Octet Selects one of four octets Dword Selects upper (1) or lower (0) dword Figure 20. L2 Tag or Data Location (AMD-K6™-2E+ Processor)—EDX Symbol Description Selects Tag (1) or Data (0) access Selects desired cache way... -

Page 63: Figure 22. L2 Data-Eax (Same As Figure 14)

5 2 ( A M D -K 6 -2 E + p ro c e s s o r ) a n d Fi g u re 2 4 (AMD-K6-IIIE+ processor). Similarly, if the L2 tag is written, the write data is taken from EAX. -

Page 64: Figure 23. L2 Tag Information

Tag data read or written 31-14 Line1ST Line 1 state (M=11, E=10, S=01, I=00) 11-10 Line0ST Line 0 state (M=11, E=10, S=01, I=00) 9-8 Two bits of LRU for each way Figure 23. L2 Tag Information (AMD-K6™-2E+ Processor)—EAX 10 9 Line1ST Line0ST Reserved... -

Page 65: Figure 25. Lru Byte (Same As Figure 16)

10b Used More Recently Than 11b, But Less Recently Than 01b 11b Least Recently Used Figure 25. LRU Byte (same as Figure 16) Writing to L2 Tag of When writing to the L2 tag of the AMD-K6-IIIE+ processor, AMD-K6-IIIE+ special consideration must be given to the least significant bit Processor of the Tag field of the EAX register—... -

Page 66: Enhanced Power Management Register (Epmr) (Low-Power Versions)

Enhanced Power Management Register (EPMR) (Low-Power Versions) To support AMD PowerNow! technology, the low-power versions of the AMD-K6-2E+ and AMD-K6-IIIE+ processors Model D are designed with enhanced power management (EPM) features: dynamic bus divisor control, and dynamic voltage ID control. -

Page 67: Epm 16-Byte I/O Block (Low-Power Versions Only)

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 EPM 16-Byte I/O Block (Low-Power Versions Only) The EPM 16-byte I/O block contains one 4-byte field—Bus D iv is o r a n d Vo lt a g e I D Co n t ro l ( B V C ) — fo r en abl in g , controlling, and monitoring the EPM features (see Figure 27). -

Page 68: Figure 28. Bus Divisor And Voltage Id Control (Bvc) Field

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 11 10 9 8 7 SGTC VIDO IBF[2:0] Reserved Symbol Description Bits SGTC Stop Grant Time-out Counter 31-12 BVCM Bus Divisor and VID Change Mode VIDC Voltage ID Control Bus Divisor Control... -

Page 69: Embedded Amd Processor Recognition

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Embedded AMD Processor Recognition The CPUID instruction provides a simple way for hardware and software to identify the type of processor and its feature set. After detecting the processor and its capabilities, software can be accurately tuned to the system for optimal performance and benefit to users. -

Page 70: Testing For The Cpuid Instruction

“Appendix A” on page 71 contains a detailed description of the CPUID instruction. Testing for the CPUID Instruction Beginning with the AMD-K6E processor Model 7, all AMD processors support the CPUID instruction. However, it is still recommended that software verify that the CPUID instruction is supported. -

Page 71: Using Cpuid Functions

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 If the value has changed, the CPUID instruction is available for identifying the processor and its features. The following code sample demonstrates the way a program uses the PUSHFD and POPFD instructions to test the ID bit. -

Page 72: Identifying The Processor's Vendor

8000_0000h. Within AMD’s family of processors, different members can execute a different number of functions. Table 28 summarizes the CPUI D functio ns c ur rently implem ente d on AMD processors. Table 28. CPUID Functions in AMD-K6™ Processors AMD-K6™-2... -

Page 73: Testing For Extended Functions

If this value is at least 8000_0001h, extended functions are supported. With one exception, the AMD extended feature flags include all the information provided in the standard feature flags as well as indicators for the additional AMD processor-specific feature enhancements. -

Page 74: Figure 29. Contents Of Eax Register Returned By Function 1

1101b (Dh) xxxx AMD-K6-IIIE+ Processor (Model D) Notes: 1. Contact your AMD representative for the latest stepping information. Refer to Table 1 on page 2 for the range of allowable stepping IDs associated with each model number. Embedded AMD Processor Recognition... -

Page 75: Identifying Supported Features

Page size extensions for 36-bit addresses are PSE-36 (Page Size Extension) supported using a 4-byte directory entry. 18–21 Reserved on all AMD processors AMD additions to the original MMX™ instruction set AMD Multimedia Instruction Extensions are supported. Embedded AMD Processor Recognition... -

Page 76: Determining Instruction Set Support

1. “Appendix A” on page 71 contains details on bit values. 2. Bit definitions: 0 = No Support, 1 = Support 3. For more information on these instructions, see the AMD Extensions to the 3DNow!™ and MMX™ Instructions Sets Manual, order# 22466. -

Page 77: Support

3DNow! and MMX instructions, use the following algorithm. A code sample using the CPUID instruction to identify the processor and its features is available from AMD’s website at http://www.amd.com/products/cpg/bin. There are other ways to implement detection besides the way shown in the sample. -

Page 78: Amd Processor Signature (Extended Function)

Extended function 8000_0001h returns the embedded AMD processor signature. The signature is returned in the EAX register and provides generation, model, and stepping information for AMD processors. Figure 30 shows the contents returned in the EAX register. 12 11 Reserved Generation/Family 11–8... -

Page 79: Displaying Cache Information

See “Function 8000_0007h — AMD PowerNow!™ Technology Information” on page 79 for more detailed bit descriptions. Sample Code A code sample using the CPUID instruction to identify the processor and its features is available from AMD’s website at http://www.amd.com/products/cpg/bin. Embedded AMD Processor Recognition... -

Page 80: New Amd-K6™ Processor Instructions

Instruction Specification Application Note, order# 21086 for more information. (Note that Model 7 processors do not support these instructions.) The AMD-K6-2E+ Model D/[7:4] and the AMD-K6-IIIE+ Model D/[3:0] processors implement the following additional instructions: 3DNow!™ Instruction Extensions—5 new instructions for multimedia software. -

Page 81: Additional Considerations

All production models and steppings of the AMD-K6 processor support the WAELIM form of write allocate, which is the only form of write allocate that should be enabled. AMD does not recommend enabling the obsolete form of write allocate (WCDE) because system performance can be degraded by doing so. -

Page 82: Read-Only Memory

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 sampling KEN# before it was valid (in this case, BRDY# was used by the processor to sample KEN#). If NA# is not asserted during memory write cycles, then the processor does not fully take advantage of the potential performance gains that bus pipelining can achieve. -

Page 83: Appendix A

Beginning with the AMD-K6E processor Model 7, all AMD processors support the CPUID instruction. However, it is still recommended that software verify that the CPUID instruction is supported. See “Testing for the CPUID Instruction” on page 58 for more information. -

Page 84: Standard Functions

The second value is the vendor identification string. This 12-character ASCII string is returned in the EBX, EDX, and ECX registers in little-endian format. AMD processors return a vendor identification string of “AuthenticAMD” as follows:... -

Page 85: Embedded Amd-K6™ Processors Bios Design Guide 23913A/0—November

In most cases, a “1” indicates the feature is present, and a “0” indicates the feature is not present. Table 31 on page 74 contains a list of the currently defined standard feature flags for the AMD-K6 family of processors. Reserved bits will be used for new features as they are added. -

Page 86: Table 31. Standard Feature Flag Descriptions

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Table 31. Standard Feature Flag Descriptions AMD-K6-2E+ AMD-K6-2 & AMD-K6E AMD-K6-2E AMD-K6-III AMD-K6-IIIE+ Processor Processors Processor Processors Feature (Model 7) (Model 8) (Model 9) (Model D) Floating-Point Unit Virtual Mode Extensions... -

Page 87: Extended Functions

‘0’ indicates the feature is not present. Table 32 on page 76 contains a list of the currently defined extended feature flags for the AMD-K6 family of processors. Reserved bits will be used for new features as they are added. -

Page 88: Table 32. Extended Feature Flag Descriptions

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Table 32. Extended Feature Flag Descriptions AMD-K6-2 AMD-K6-2E+ AMD-K6E AMD-K6-2E AMD-K6-III AMD-K6-IIIE+ Processor Processors Processor Processors Feature (Model 7) (Model 8) (Model 9) (Model D) Floating-Point Unit Virtual Mode Extensions... - Page 89 AMD-K6™-2+ for the AMD-K6-2E+ processor and AMD-K6™-III+ for the AMD-K6-IIIE+ processor. However, the actual value returned for either processor is AMD-K6™-III. The AMD CPUID utility v2.07 should be used to display the name string specified for AMD-K6E, Model D processors. This utility can be obtained from http: //www.amd.com/products/cpg/bin/amdcpuid.exe.

-

Page 90: Table 33. Ebx Format Returned By Function 8000_0005H

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Function 8000_0005h — L1 Cache Information Input: EAX = 8000_0005h Output: EAX = Reserved EBX = TLB Information ECX = L1 Data Cache Information EDX = L1 Instruction Cache Information Function 8000_0005h returns information about the processor’s on-chip L1 caches and... -

Page 91: Table 36. Ecx Format Returned By Function 8000_0006H

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Function 8000_0006h — L2 Cache Information This function is only available on AMD-K6 processors models 9 and D. Input: EAX = 8000_0006h Output: EAX = Reserved EBX = Reserved ECX = L2 Unified Cache Information EDX = Reserved Function 8000_0006h returns information about the processor’s L2 cache. -

Page 92: Cache Associativity Field Definitions

Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Cache Associativity Field Definitions This section describes the values returned in the associativity fields. Associativity for L1 The associativity fields for the L1 data cache, L1 instruction Caches and L1 TLBs cache, L1 data TLB, and L1 instruction TLB are all 8 bits wide. -

Page 93: Appendix B

Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Appendix B Values Returned by the CPUID Instruction Table 39 contains all the values returned for AMD-K6 processors by the CPUID instruction. Table 39. CPUID Values Returned by AMD-K6™ Processors AMD-K6-2 &... - Page 94 1. Low-power versions only. Reserved on standard-power version. 2. Extended functions 8000_0002h, 8000_0003h, and 8000_0004h each return part of the processor name string. Some AMD-K6-2E pro- cessors may have the following name string: function 8000_0002h, ECX = 322D_296Dh and EDX = 6F72_5020h, and function 8000_0003h, EAX = 7373_6563h and EBX = 0000_726Fh.

-

Page 95: Index

....58 AMD-K6™-2 Processor ....... 3 overview . - Page 96 3DNow! test ........65 AMD-K6™-2 processor ......17 CLI .

- Page 97 ......13 signatures for embedded AMD processors (table) ..62 speed detection .

- Page 98 Preliminary Information Embedded AMD-K6™ Processors BIOS Design Guide 23913A/0—November 2000 Write Cycles out-of-order ........25...

Need help?

Do you have a question about the -K6-2/450 - MHz Processor and is the answer not in the manual?

Questions and answers