Advertisement

Quick Links

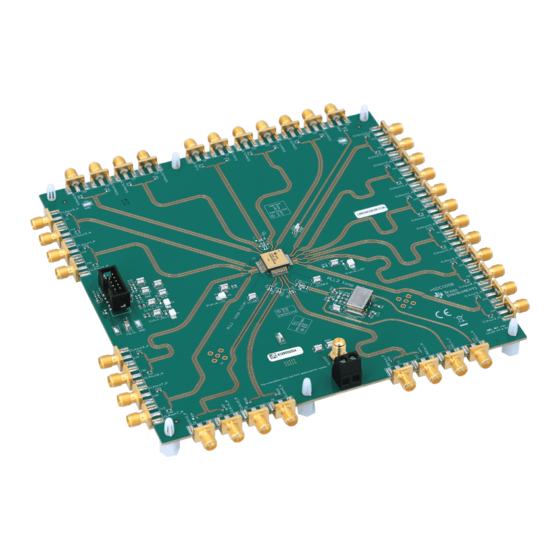

The LMK04832EVM-CVAL evaluation module (EVM) provides a platform to evaluate the performance and

features of the LMK04832-SP Space Grade Ultra-Low-Noise JESD204B Dual-Loop Clock Jitter Cleaner

from Texas Instruments. The user's guide describes how to set up and operate the EVM. The LMK04832-

SP device on each EVM is an Engineering Model, intended for engineering evaluation only. The devices

and EVMs are not suitable for qualification, production, radiation testing or flight use.

1

Evaluation Board Kit Contents

....................................................................................................................

2

Quick Start

3

PLL Loop Filters and Loop Parameters

4

Default TICS Pro Mode

5

Using TICS Pro to Program the LMK04832-SP

6

Evaluation Board Inputs and Outputs

7

Recommended Test Equipment

8

Length Matching

..................................................................................................................

9

Schematics

10

Bill of Materials

Appendix A

TICS Pro Usage

1

Quick Start Diagram

2

Clock Outputs Page Description Diagram

3

Selecting a Default Mode for the LMK04832-SP Device

4

Selecting the LMK04832-SP

5

Loading the Device

6

Setting the Default Configuration for LMK04832-SP

7

Setting Digital Delay, Clock Divider, Analog Delay, and Output Format

8

Schematic - Power Supply

9

Schematic - LMK04832-SP

10

Schematic - Digital

11

Schematic - Clock Outputs 1 of 2

12

Schematic - Clock Outputs 2 of 2

13

TICS Pro - Communication Setup Window

14

TICS Pro - User Controls Page

15

TICS Pro - Raw Registers Page

16

TICS Pro - Set Modes Page

17

TICS Pro - Holdover Page

18

TICS Pro - CLKinX Control Page

19

TICS Pro - PLL1 and 2 Page

20

TICS Pro - SYNC / SYSREF Page

21

TICS Pro - Clock Outputs Page

22

TICS Pro - Other Page

SNAU252 – June 2020

Submit Documentation Feedback

LMK04832EVM-CVAL User's Guide

.............................................................................................

...................................................................................

.....................................................................................................

...................................................................................

..........................................................................................

............................................................................................................

.............................................................................................................

...................................................................................................

.........................................................................................................

................................................................................

...............................................................................................

..........................................................................................................

................................................................................................

...............................................................................................

.........................................................................................................

........................................................................................

........................................................................................

.............................................................................

..........................................................................................

.........................................................................................

..............................................................................................

................................................................................................

........................................................................................

.............................................................................................

......................................................................................

..........................................................................................

....................................................................................................

Copyright © 2020, Texas Instruments Incorporated

Contents

.........................................................................

List of Figures

...............................................................

....................................................................

............................................

LMK04832EVM-CVAL User's Guide

User's Guide

SNAU252 – June 2020

2

3

6

7

7

11

13

13

15

20

25

3

5

7

8

9

9

10

15

16

17

18

19

25

26

27

28

29

30

31

32

33

34

1

Advertisement

Summary of Contents for Texas Instruments LMK04832EVM-CVAL

- Page 1 LMK04832-SP Space Grade Ultra-Low-Noise JESD204B Dual-Loop Clock Jitter Cleaner from Texas Instruments. The user’s guide describes how to set up and operate the EVM. The LMK04832- SP device on each EVM is an Engineering Model, intended for engineering evaluation only. The devices and EVMs are not suitable for qualification, production, radiation testing or flight use.

-

Page 2: Table Of Contents

Differential Pair Lengths ......................Bill of Materials Trademarks PLLatinum is a trademark of Texas Instruments. All other trademarks are the property of their respective owners. Evaluation Board Kit Contents Table 1 lists the components found in the evaluation board kit. - Page 3 Reference clock from signal generator or other external 4.5 V source. 122.88 MHz Default is (Default) LDO to IC Figure 1. Quick Start Diagram SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 4 Quick Start www.ti.com Quick Start Description The LMK04832EVM-CVAL allows full verification of the device functionality and performance specifications. To quickly set up and operate the board with basic equipment, refer to the quick start procedure below and test setup shown in Figure 1.

- Page 5 24. CLKoutY_SRC_MUX: Select device clock or SYSREF clock path for CLKoutY. 25. SCLKX_Y_DIS_MODE: Set the output state of output clock drivers for the SYSREF clock. For values SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

-

Page 6: Pll1 Loop Filter Parameters For Crystek 122.88-Mhz Vcxo

The reference clock consequently serves only as a frequency reference rather than a phase reference. The loop filters on the LMK04832EVM-CVAL evaluation board are setup using the approach above. The loop filter for PLL1 has been configured for a narrow loop bandwidth (< 1 kHz). The specific loop bandwidth values depend on the phase noise performance of the oscillator mounted on the board. -

Page 7: Default Tics Pro Modes For The Lmk04832-Sp

Start TICS Pro Application Click Start → Programs → Texas Instruments → TICS Pro. The TICS Pro program is installed by default to the Texas Instruments application group. Select Device Click Select Device → Clock Generator/Jitter Cleaner (Dual Loop) → LMK04832-SP. - Page 8 Ctrl+L is the accelerator key assigned to the Write All Registers option and is very convenient. LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 9 1. Click on the Clock Outputs page, Section A.9 2. Uncheck CLKoutX_Y_PD in the Clock Output box to enable the channel, 3. Set the following as needed: SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 10 50-Ω input as follows. a. For LVDS: i. A balun (like ADT2-1T or high quality Prodyn BIB-100G) is recommended for differential-to- single-ended conversion. LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

-

Page 11: Description Of Evaluation Board Inputs And Outputs

(normal, inverted, or off/tri-state). Best performance/EMI reduction is achieved by using a complementary output mode like Norm/Inv. It is not recommended to use Norm/Norm or Inv/Inv mode. SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated... - Page 12 Main power supply input for the evaluation board. Input The LMK04832EVM-CVAL default is setup to use the TPS7A4501HKU/EM voltage regulator. This is a space grade voltage regulator. 0-ohm resistors R3, R5, R6, R14 and R15 can be re-configured to route power through the on-board commercial Power grade LDO, the TPS7A4533KTTR.

- Page 13 50-Ω cables to minimize external sources of skew or other errors/distortion that may be introduced if using oscilloscope probes. Length Matching Specific traces on the LMK04832EVM-CVAL were length matched to ensure device functions such as skew and 0-delay mode phase could be tested. Table 6 contains the lengths of each of the traces on the EVM.

-

Page 14: Differential Pair Lengths

CLKout7_N, CLKout8_P, CLKout8_N SYNC CLKout2_P, CLKout2_N, CLKout3_P, CLKout3_N, CLKout4_P, CLKout4_N, CLKout5_P, CLKout5_N, CLKout9_P, Skew 4240.5 ± 0.5 CLKout9_N,CLKout10_P, CLKout10_N, CLKout11_P, CLKout11_N, CLKout12_P, CLKout12_N, CLKout13_P, CLKout13_N LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated... - Page 15 10µF 0.01uF Vcc11_CG3 120 ohm 10µF 0.01uF Vcc12_CG0 120 ohm 10µF 0.01uF Vcc3_SYSREF SYSREF 120 ohm 10µF 0.01uF Figure 8. Schematic - Power Supply SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 16 VCXO_GND 603281 49.9 0.1µF 100nF VCXOs OSCin_3_N OSCin_N Vcont PLL1 Loop Filter CVHD-950-122.880 VCXO Loop Filter 2.7uF 0.1uF 680nF Figure 9. Schematic - LMK04832-SP LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 17 R107 SYNC TP21 R108 SYNC Status_LD2 SYNC C106 R110 100pF Status_LD2 C107 100pF Status_LD2 Green 2.1V SYNC Level Translation Figure 10. Schematic - Digital SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 18 C103 CLKout8_N 13nH CLKout8_1_N CLKout12_1_N CLKout12_N CLKout8_N CLKout12_N 0.1µF 0.1µF C102 CLKout10_1_N CLKout10_N CLKout10_N 0.1µF Figure 11. Schematic - Clock Outputs 1 of 2 LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 19 Vcc11_CG3 Vcc11_CG3 Vcc12_CG0 CLKout9_P CLKout11_P CLKout13_P CLKout9_1_P CLKout11_1_P CLKout13_1_P CLKout9_P CLKout11_P CLKout13_P 0.1µF 0.1µF 0.1µF Figure 12. Schematic - Clock Outputs 2 of 2 SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 20 CAP, CERM, 2200 Kemet C0603C222K5RAC pF, 50 V, +/- 10%, X7R, 0603 C64, C72 CAP, CERM, 0.1 Kemet C0603C104K4RAC uF, 16 V, +/- 10%, X7R, 0603 LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

-

Page 21: Bill Of Materials

RES, 270, 5%, Vishay-Dale CRCW0402270RJN R29, R37 0.063 W, AEC- Q200 Grade 0, 0402 RES, 100, 1%, Vishay-Dale CRCW0402100RFK 0.063 W, AEC- Q200 Grade 0, 0402 SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated... - Page 22 Miniature, SMT TP10, TP11, TP12, TP13, TP14, TP16, TP17, TP18, TP19, TP20, TP21 Wide Vin Low- Texas Instruments TPS7A4501HKU/E Dropout Voltage Regulator, HKU0010A (CFP- LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 23 R36, R48, R62, R67 AEC-Q200 Grade 0, 0603 R26, R35, R42, R55 RES, 100, 1%, Vishay-Dale CRCW0402100RFK 0.063 W, AEC- Q200 Grade 0, 0402 SNAU252 – June 2020 LMK04832EVM-CVAL User’s Guide Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 24 Grade 0, 0603 TP4, TP5, TP6, Test Point, Keystone 5019 TP15 Miniature, SMT Ultra-Low Noise Crystek Corporation 603281 LVPECL VCXO with 162dBc/Hz NOISE Floor, SMD LMK04832EVM-CVAL User’s Guide SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 25 Devices used by other instances of TICS Pro will not display in this list. Figure 13. TICS Pro - Communication Setup Window SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 26 The User Controls page has controls typically not included on one of the other dedicated pages. Figure 14. TICS Pro - User Controls Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 27 NOTE: Use the Export Register Map to create a text file with the register values for simple re-use of the register configuration. Figure 15. TICS Pro - Raw Registers Page SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 28 LMK04832-SP modes of operation. Figure 16. TICS Pro - Set Modes Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 29 In addition to the above steps, auto clock selection mode must be used to allow the LMK04832-SP to automatically switch to holdover when enabled clocks for auto switching (CLKinX_EN) are lost. Figure 17. TICS Pro - Holdover Page SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 30 CLKinX is selected, where the CLKinX inputs are routed to. Also on this page are controls to reset the PLL1 R or PLL2 N divider. Figure 18. TICS Pro - CLKinX Control Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 31 Independent to allow the OSCin frequency to be unlinked from the external VCXO frequency. Figure 19. TICS Pro - PLL1 and 2 Page SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 32 (0x01) Conditional Low, keeping the SYSREF_CLR = 1 during transition will prevent glitch pulses from the SYSREF output. Figure 20. TICS Pro - SYNC / SYSREF Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 33 CLKoutY (odd clock), X for controls impacting only CLKoutX and Y for controls impacting only CLKoutY. Figure 21. TICS Pro - Clock Outputs Page SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

- Page 34 _TYPE field which allows the input or output mode of the pin to be defined. The second is the _MUX field which, when set for output, controls what the pin will output. Figure 22. TICS Pro - Other Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated...

-

Page 35: Tics Pro - Current Calculator Page

In the lower left is some boxes to account for extra I due to LEDs, VCXO, or other. Figure 23. TICS Pro - Current Calculator Page SNAU252 – June 2020 TICS Pro Usage Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated... -

Page 36: Tics Pro - Burst Page

Burst Page The Burst page allows the user to program sequences of register programming or pin control. Figure 24. TICS Pro - Burst Page TICS Pro Usage SNAU252 – June 2020 Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated... - Page 37 TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. TI objects to and rejects any additional or different terms you may have proposed. IMPORTANT NOTICE Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated...

Need help?

Do you have a question about the LMK04832EVM-CVAL and is the answer not in the manual?

Questions and answers