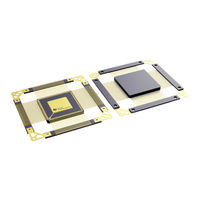

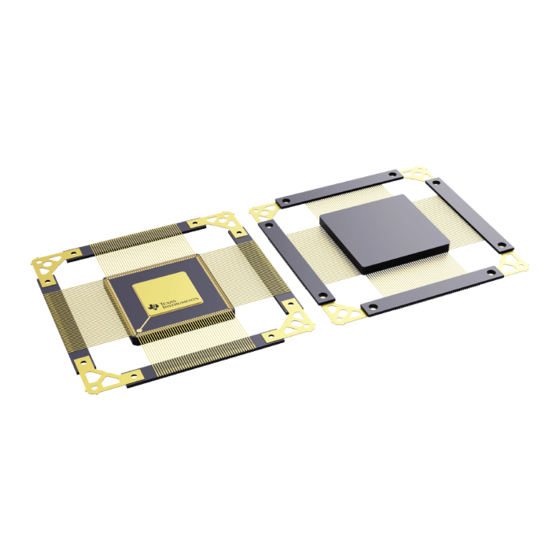

Texas Instruments SM320F2812-HT Data Manuals

Manuals and User Guides for Texas Instruments SM320F2812-HT Data. We have 1 Texas Instruments SM320F2812-HT Data manual available for free PDF download: Data Manual

Texas Instruments SM320F2812-HT Data Data Manual (153 pages)

Digital Signal Processor

Brand: Texas Instruments

|

Category: Signal Processors

|

Size: 1.42 MB

Table of Contents

Advertisement

Advertisement

Related Products

- Texas Instruments SM320C6455-EP

- Texas Instruments SmartRF06

- Texas Instruments SolarMagic SM72445

- Texas Instruments SMALL-AMP-DIP

- Texas Instruments Start-Up Customization

- Texas Instruments StudyCards

- Texas Instruments SERDESUB-16OVT

- Texas Instruments SRC4194EVM

- Texas Instruments SN65LVDS387EVM

- Texas Instruments SN65DSI83 EVM