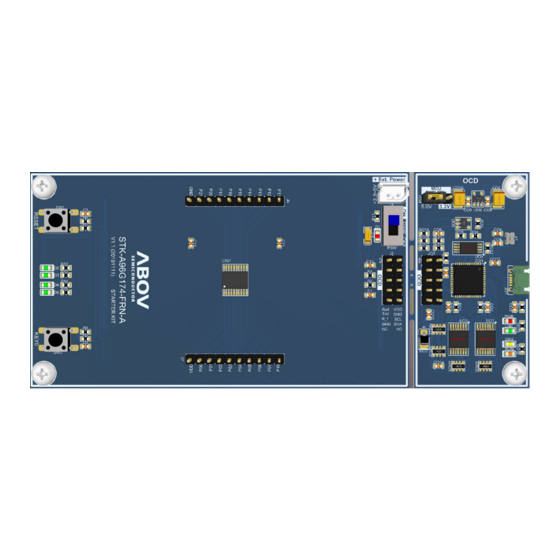

Abov A96G174 Manuals

Manuals and User Guides for Abov A96G174. We have 1 Abov A96G174 manual available for free PDF download: User Manual

Abov A96G174 User Manual (211 pages)

16 MHz 8-bit A96G174 Microcontroller 8 Kbyte Flash memory, 12-bit ADC, 3 Timers, USART, I2C, Window WDT

Brand: Abov

|

Category: Microcontrollers

|

Size: 2 MB

Table of Contents

-

Description11

-

Pinouts14

-

Addressing27

-

Data Memory31

-

SFR Map35

-

SFR Map37

-

6 I/O Ports43

-

Register Map44

-

P0 Port45

-

P1 Port49

-

P2 Port53

-

Register Map65

-

Register Map70

-

Register Map75

-

Timer 0/1/278

-

Timer 078

-

Register Map84

-

Timer 187

-

Register Map95

-

Timer 299

-

16-Bit PPG Mode103

-

Register Map105

-

12 12-Bit ADC108

-

Block Diagram109

-

ADC Operation110

-

Register Map111

-

13 I2C114

-

Block Diagram114

-

Bit Transfer115

-

Data Transfer116

-

Acknowledge116

-

Block Operation119

-

Slave Receiver123

-

Register Map124

-

14 Usart129

-

Block Diagram130

-

Clock Generation131

-

Data Format133

-

Parity Bit134

-

Sending Tx Data134

-

Parity Generator135

-

USART Receiver135

-

Parity Checker137

-

SPI Mode139

-

Register Map143

-

IDLE Mode155

-

STOP Mode155

-

Register Map158

-

16 Reset159

-

Power on Reset160

-

Register Map166

-

Register Map168

-

Memory Map176

-

Flash Memory Map176

-

Flash Operation177

-

Security183

-

Configure Option183

-

Compiler185

-

Programmers199

-

OCD Emulator199

-

Gang Programmer200

-

Appendix204

-

Revision History209

Advertisement