Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for MYiR MYC-YT507H

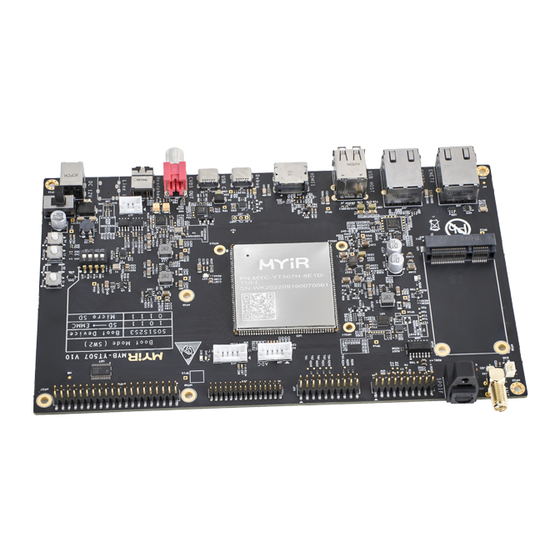

- Page 1 MYIR-MYC-YT507H-HW-HDG-EN_V1.0 MYC-YT507H Hardware Design Guide File ID: MYIR-MYC-YT507H-HW-HDG-EN Version: V1.0 File status: Author: [ ]The draft Dana Date created: [ √ ] Official release 2022-04-15 Date updated: 2022-04-15 Copyright © MYIR Electronics Limited 2020-2030 all rights reserved. - 1 -...

-

Page 2: History

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 History Version Author Participants Date Description V1.0 Dana 20220415 Initial Version - 2 -... -

Page 3: Table Of Contents

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Contents History ............................ - 2 - Contents ..........................- 3 - 1. Overview ......................- 6 - 1.1. Supported products ....................- 6 - 1.2. Disclaimer ........................- 6 - 2. Power supply design ..................- 7 - 2.1. Reference Design ....................... - 7 - 2.2. - Page 4 MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.4.1. Reference Design ..................- 22 - 5.4.2. Layout Guidelines ..................- 23 - 5.5. MIPI CSI ........................- 24 - 5.5.1. Reference Design ..................- 24 - 5.5.2. Layout Guidelines ..................- 24 - 5.6. Parallel CSI ........................- 25 - 5.6.1.

- Page 5 MYIR-MYC-YT507H-HW-HDG-EN_V1.0 6.1. Power supply design ....................- 36 - 6.2. system start up Check ....................- 36 - 6.3. Peripheral circuits design ..................- 37 - Appendix A ......................- 38 - Warranty & Technical Support Services ..............- 38 - - 5 -...

-

Page 6: Overview

Please make adjustments according to the actual situation. MYIR shall not be liable for any form of technical endorsement or joint liability for any proposal contained in any document. - 6 -... -

Page 7: Power Supply Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 2. Power supply design The design of the power supply system is of vital importance in the design of embedded products, engineers need to consider not only the basic electrical parameters of power itself, but also the stability of the power supply design, such as electromagnetic compatibility, temperature range, safety design, etc. -

Page 8: Power Sequence

Figure 2-3 Power input circuit in noise-sensitive situations 2.3. Power Sequence The MYC-YT507H core board and carrier board have power-on sequence requirements. Ensure that the core board is powered on first. It is recommended to enable power supply for 5V and 3.3V peripherals of the carrier board after initialization of the core board. -

Page 9: Layout Guidelines

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 2.4. Layout Guidelines The distance between different power supply planes should be at least 20mil; Widen the width of the power line and ground wire as far as possible, to meet the required rated current value, the width of the feedback signal should not be too narrow, it is recommended to be more than 10mil;... -

Page 10: Boot Configure

BOOT SEL[4:0] pins do not add pull-up or pull-down design in the core board. But there is a 15K pull-up resistor inside the chip by default. MYC-YT507H core board start up mode mainly has eMMC start up, Micro SD card start up. See Table 3-1. -

Page 11: Reset And Key Circuit Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 4. Reset and key circuit design MYC-YT507H core board provides 3 special pins, the function is Reset, ONOFF start off, FEL burning mirror. During design, it is suggested to reserve resistance and capacitor to form a simple RC filter to filter out the jitter interference when the key is pressed, while avoiding the interference introduced from the key to affect the reset signal.In the harsh electromagnetic... -

Page 12: Reference Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 4.1. Reference Design Figure 4-2 reset Reference design Figure 4-3 external hardware watchdog Resetting reference circuit 4.2. Layout Guidelines The width of reset signal line should not be too narrow, it is recommended not less than 8mil; Reset signal is sensitive signal, which is recommended to be surrounded by ground;... -

Page 13: Interface Circuit Design

5. Interface circuit design 5.1. SMHC SMHC stands for SD/MMC Host Controller. MYC-YT507H core board support leads to two SMHC interfaces. It is recommended to use the SMHC0 interface for Micro SD circuits and the SMHC1 to use peripherals with SDIO WIFI or other SDIO interfaces. -

Page 14: Reference Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.1.1. Reference design Figure 5-2 SD card Reference design Figure 5-3 WIFI reference circuit - 14 -... -

Page 15: Layout Guidelines

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.1.2. Layout guidelines Single-ended signal 50 Ω impedance; Trace match the data line and control line to be within 100 mils; SD1_CLK is recommended to be surrounded with ground. If not, ensure the distance between the clock signal and other signals follow 3W rule. -

Page 16: Uart

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.2. UART The MYC-YT507H core board supports up to six serial ports. Due to the pin reuse of the chip, the core board only uses 4 channels of serial port by default, among which UART1 has flow control (RTS and CTS signal) function, and the other 3 channels of UART only have TXD and RXD by default. -

Page 17: Uart To Rs485

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Figure 5-5 Isolate RS232 reference circuit Figure 5-6 Isolating 5V power reference circuit 5.2.2. UART to RS485 Reference circuit UART to RS485 chip is TI ISO3802DW isolation conversion chip, the chip integrated signal isolation function, do not need to add additional signal isolation chip. The converted RS485_A/B can be directly connected to the RS485 connector. -

Page 18: Uart To Usb

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Figure 5-7 isolation rs485 reference circuit Figure 5-8 Isolating 5V power reference circuit 5.2.3. UART to USB The reference circuit uses FT234xD-T conversion chip to convert UART debugging serial port signal to USB signal. USB interface adopts Type C USB connector, which is easy to plug and unplug. -

Page 19: Layout Guidelines

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Figure 5-9 Debug serial port reference circuit 5.2.4. Layout Guidelines Keep sufficient spacing between signal and power plane before and after isolation; The 120 Ω resistor (R5) in the RS485 circuit is placed close to the conversion chip;... -

Page 20: Usb

USB2.0 Host interfaces, and the OTG controller provides one USB2.0 interface. MYC-YT507H core board brings it all out. If users want to use THE OTG function of USB, they can use Micro USB port or Type C USB port. - Page 21 MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Differential impedance of the USB signal is controlled by 90Ω; USB signal line as short as possible; USB signals as soon as possible, if the substation is changed, it is necessary to place the GND reflow via in the range of 200 mils from the changing layer.

-

Page 22: Ethernet

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.4. Ethernet The MYC-YT507H core board provides two Ethernet MAC controllers. Contains one RMII interface and one RGMII interface (supporting RMII). Ethernet interface design requires proper network PHY chip. Figure 5-12 Ethernet reference circuit 5.4.1. Reference Design Figure 5-13 Ethernet RMII reference circuit... -

Page 23: Layout Guidelines

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Figure 5-14 Ethernet RGMII reference circuit 5.4.2. Layout Guidelines RGMII signal isometric control, error ±25mil, line spacing more than 2W; Equal length control of RMII signal, error +-50mil, line spacing more than 2W; Network differential signal isometric control, difference internal error ± 30mil, spacing of adjacent difference pairs more than 3W;... -

Page 24: Mipi Csi

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.5. MIPI CSI MYC-YT507H provides a 4-lane MIPI CSI camera input interface. MIPI CSI interface supports 8M@30fps or 1080p@25fps. In order to improve the stability and reliability of the interface, ESD protection and common mode inductance filtering should also be considered when designing the interface circuit. -

Page 25: Parallel Csi

BT656,BT601,BT1120, data bit width can support 8 bits, 16 bits, 32 bits. Due to pin multiplexing, the Parallel interface of MYC-YT507H core board chooses 8-bit data signal by default. It is recommended to use mile-Electronics my-CAM011B camera module with connection, please visit http://www.myir-tech.com/product/my_cam011b.htm... -

Page 26: Reference Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.6.1. Reference Design Figure 5-17 Parallel CSI Interface Reference Circuit 5.6.2. Layout guidelines Parallel CSI signal routing for equal length control, error range ± 100mil; It is recommended that the spacing between signal cables be at least 2W. -

Page 27: I2C

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.7. I2C MYC-YT507H core board supports four I2C controllers and two modes, with the rate of 100Kbit/s in standard mode and 400Kbit/s in fast mode. Several devices can be mounted on the same I2C main line. The following points should be paid attention to in schematic design: ... -

Page 28: Lvds

Link LVDS interfaces to support 1366x768@60fps display output. In addition, two Single Link LVDS can form Dual Link LVDS to support higher display resolution 1920x1080@60fps. MYIR officially designed a 7 inch LVDS MY-LVDS070C LCD module. The LCD module supports a resolution of 1024x600, please refer to the website for details http://www.myir-... -

Page 29: Layout Guidelines

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 Figure 5-20 Dual Link LVDS reference design 5.8.2. Layout guidelines The difference pair of data and clock shall follow the rule of equal length and equal distance, the difference pair error control is +-5mil, and the difference impedance is 100 Ω. Less holes,... -

Page 30: Hdmi

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.9. HDMI MYC-YT507H core board native support one HDMI display output interface, the highest support 4K@60fps resolution. 5.9.1. Reference Design Figure 5-21 HDMI Display output reference circuit 5.9.2. Layout Guidelines Dynamic resistance (Rdy) of ESD device on HDMI differential line is less than 0.35 Ω , parasitic capacitance is less than 0.35pF,... -

Page 31: Tv Out

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.10. TV OUT MYC-YT507H core board supports one TV-out (CVBS) output interface and supports NTSC and PAL modes. 5.10.1. Reference Design Figure 5-22 TV-OUT Display output reference circuit 5.10.2. Layout Guidelines TV-out wiring needs 75 Ω resistors in series and needs large package, because CVBS output current type, if the package is too small, it will heat up and burn OUT the resistance;... -

Page 32: Spdif-Out

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.11. SPDIF-OUT SPDIF, SONY / PHILIPS Digital Interface, SONY / PHILIPS Digital Audio Interface. SPDIF is a transmission specification for digital signals. It usually uses coaxial and optical fiber as transmission carriers. Coaxial uses electrical transmission and optical fiber uses optical transmission. -

Page 33: Audio I2S

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.12. AUDIO I2S MYC-YT507H core board supports three I2S interfaces. In circuit design, I2S interface signal needs to be connected to the audio codec chip, and then connected to the headset and microphone. In the reference circuit, the AUDIO_GND of the audio circuit is isolated from the DGND of the digital circuit by magnetic beads, and the capacitor of the power supply pin and the filter capacitor of the audio signal should also be connected to the AUDIO_GND. -

Page 34: Line Out

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.13. Line OUT T507-H native supports line Out output. MYC-YT507H core board is directly connected to the line Out interface. 5.13.1. Reference Design 图 5-25 Line Out 接口参考电路 5.13.2. Layout Guidelines Line Out belongs to analog audio signal, and 10mil or above is recommended. -

Page 35: Adc

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 5.14. ADC MYC-YT507H core board supports GPADC and LRADC. GPADC has a 12-bit resolution, a maximum sampling rate of 1Mhz, and supports a signal input range of 0~1.8V. LRADC supports a maximum resolution of 6 bits and a sampling rate of 2Khz. The corresponding LRADC supports a range of 0~ 1.35v input signals. -

Page 36: Design Checklist

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 6. Design checklist 6.1. Power supply design Check box Proposal The recommended value is 5V and the absolute value is 1. core module supply voltage 4.5V-5.5V Use capacitors with 47uF and above value for core module 2. Decoupling capacitance... -

Page 37: Peripheral Circuits Design

MYIR-MYC-YT507H-HW-HDG-EN_V1.0 6.3. Peripheral circuits design Category Check box Proposal Capacitance value of USB D+/D- The capacitance value of ESD devices is signal ESD device recommended to be less than 2pF The interface 5V capacitor requires a 1-ohm Whether the capacitor of the supply... -

Page 38: Warranty & Technical Support Services

Delivery Time MYIR will always keep a certain stock for its regular products. If your order quantity is less than the amount of inventory, the delivery time would be within three days; if your order quantity is greater than the number of inventory, the delivery time would be always four to six weeks. - Page 39 For any maintenance service, customers should communicate with MYIR to confirm the issue first. MYIR’s support team will judge the failure to see if the goods need to be returned for repair service, we will issue you RMA number for return maintenance service after confirmation.

- Page 40 Products Life Cycle MYIR will always select mainstream chips for our design, thus to ensure at least ten years continuous supply; if meeting some main chip stopping production, we will inform customers in time and assist customers with products updating and upgrading.

Need help?

Do you have a question about the MYC-YT507H and is the answer not in the manual?

Questions and answers