Table of Contents

Advertisement

Quick Links

ADS5474 ADX Evaluation Board for Interleaving

......................................................................................................................

1

1.1

1.2

1.3

1.4

2

2.1

2.2

2.3

2.4

2.5

2.6

2.7

....................................................................................................................

3

...........................................................................................................................

4

5

5.1

5.2

5.3

5.4

6

6.1

6.2

7

7.1

7.2

....................................................................................................................

8

9

10

.......................................................................................................................

11

12

13

14

14.1

14.2

14.3

1

.....................................................................................................................

2

.....................................................................................................................

3

230-MHz

...................................................................................................................

4

5

.......................................................................................................................

6

SLAU247 - August 2008

Submit Documentation Feedback

..............................................................................................................

...............................................................................................

...............................................................................................

.......................................................................................

.................................................................................................

.................................................................................................................

...........................................................................................................

........................................................................................................

........................................................................................................

............................................................................................

.......................................................................................................

...............................................................................................................

.................................................................................................................

...................................................................................................

.............................................................................................

...............................................................................................

.................................................................................................

.........................................................................................................

........................................................................................................

...............................................................................................................

..................................................................................................

.........................................................................................

......................................................................................................

..........................................................................................................

............................................................................................................

.........................................................................................

.....................................................................................

....................................................................................................

..........................................................................................................

.................................................................................................................

..............................................................................................................

Contents

..........................................................................

......................................................

List of Figures

ADS5474 ADX Evaluation Board for Interleaving

User's Guide

SLAU247 - August 2008

3

3

3

3

3

4

4

4

4

4

5

5

6

6

8

9

9

9

10

10

10

10

10

10

10

11

12

12

13

13

15

15

16

16

20

22

4

13

13

14

14

16

1

Advertisement

Table of Contents

Summary of Contents for Texas Instruments ADS5474

-

Page 1: Table Of Contents

User's Guide SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Contents ........................Overview ......................Purpose ....................EVM Basic Functions ....................Power Requirements ................ADS-ADX EVM Operational Procedure ..................Circuit and Operational Description ....................Schematic Diagram ......................... Power ...................... - Page 2 List of Tables ..................DIP Switches Functional Descriptions ......................DIP Switches Modes ........................ LED Functions ......................Bill of Materials MATLAB is a trademark of The MathWorks, Inc. ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback...

-

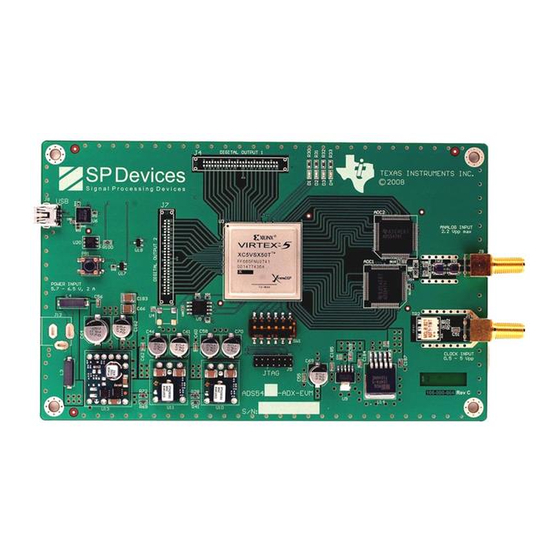

Page 3: Overview

The ADS-ADX EVM provides a platform for evaluating two interleaved ADS5474 analog-to-digital converters (ADC) with a combined sampling rate of 800 MSPS. The ADS5474 is a 14-bit, 400-MSPS ADC which is pinout compatible with the ADS5463, a 12-bit, 500-MSPS ADC. For a more in-depth theoretical description of ADC interleaving, consult the white paper Frequency-Response Mismatch Errors and Digital Correction in Time-Interleaved ADCs –... -

Page 4: Circuit And Operational Description

The output swing of the clock must be ±1 V. The clock frequency must not exceed 400 MSPS for the ADS5474. The single-ended clock input is converted into a differential signal by using a transformer. The 0° phase output of the transformer is used to clock ADC1 whereas the 180° phase output is used to clock ADC2. -

Page 5: Dip Switches

Fast blink – License error. On – New available dataset is stored in internal memory. Off – No new dataset is available. (This LED will blink when in continuous acquisition mode). SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 6: Digital Outputs

To install the software, run the ADCaptureLab-setup.exe file and follow the instructions for installation. Before continuing, you need to close any other application running to avoid the need of rebooting the system. ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... - Page 7 If you choose to install FTDI USB drivers from the installation program, the drivers are pre-installed on your hard disk, but are not activated until you connect a powered ADS-ADX EVM to the computer for the first time. SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback...

-

Page 8: View

View www.ti.com View SETTINGS/SETUP (5.1) Plot settings (7.1) Time-series plot of Connect & Capture (5.2) data Import & Export Plot tools (8) FFT plot Analysis window (7.2) ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 9: Capturing Data

Devices box. Status information on the enumeration of devices shows in Log window. 2. Select a compatible device board from the Devices list. The buttons Acquire data and Run are then activated. Acquire single batch data SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 10: Capture Single Batch

Select filename in dialog box, and press Save. Data can be exported on a text file format with a header, or a pure ASCII file for use with MATLAB™, for example. Data Analysis Analysis Settings 7.1.1 Type of Analysis Analysis type ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 11: Analysis Window Output

Code range read in batch and length of batch read. DC Power DC power in dBFS. Fundamental Single-tone Identified fundamental tones (power and frequency) tone(s) Two-tone Power maximum Other Identified power maximum (power and frequency) SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 12: Plot Tools

Returns to zoom setting before undo press Keyboard Commands Description Show version information for ADCaptureLab software Show version information for FPGA firmware and FPGA firmware status Refresh plots ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 13: Matlab Interface

Another filtered Agilent 8644B was used to provide a -1-dBFS single tone into the EVM. The results are displayed in Figure 2 through Figure f - Frequency - MHz Figure 2. 100-MHz f - Frequency - MHz Figure 3. 230-MHz SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 14: 491.5-Mhz

Figure 4. 491.5-MHz Image Offset SFDR 50 60 70 80 90 100 130 170 230 250 270 491 650 f - Frequency - Hz Figure 5. ADS5474-ADX ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 15: Troubleshooting

Devices retains all ownership rights in SP Devices IP and no license is granted under any patent right or other intellectual property right of SP Devices except for use for engineering development, demonstration, or evaluation purposes. SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 16: Printed-Circuit Board Layout, Bill Of Materials, And Schematic

Printed-Circuit Board Layout, Bill of Materials, and Schematic 14.1 Printed-Circuit Board Layout The following illustrations show the eight layers of the ADX evaluation board. Figure 6. Layer 1 ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... - Page 17 Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 7. Layer 2 Figure 8. Layer 3 SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback...

- Page 18 Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 9. Layer 4 Figure 10. Layer 5 ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback...

- Page 19 Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 11. Layer 6 Figure 12. Layer 7 SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback...

-

Page 20: 14.2 Bill Of Materials

Capacitor, 10 nF, 10%, 0402, X7R, 25V 0402 C44, C186 101-001-022 Capacitor, 100 nF, 10%, 0402, X7R, 16V 0402 C1–C12, C22–C33, C49, C50, C53, C54, C73–C85, C87–C92, C103, C123–C125, C135–C152, C154–C157, C160–C162, C190–C197 ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... - Page 21 Mounting hole, 3,5 mm 105-001-003 SP Devices logo 105-001-005 TI logo 106-000-004 PCB, ADS54xx-ADS-ADX EVM PCB1 107-000-000 SMD Pushbutton, Alps SKHUAD ALPS 107-000-001 DIP-switch, 6PST Taiway DM-06 SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback...

-

Page 22: 14.3 Schematic

Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com 14.3 Schematic Figure 14. Front End Schematic ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 23: Fpga I/O Schematic

Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 15. FPGA I/O Schematic SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 24: Usb And Logic Analyzer Connectors

Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 16. USB and Logic Analyzer Connectors ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... -

Page 25: Fpga System Schematic

Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 17. FPGA System Schematic SLAU247 – August 2008 ADS5474 ADX Evaluation Board for Interleaving Submit Documentation Feedback... -

Page 26: Power Supply Schematic

Printed-Circuit Board Layout, Bill of Materials, and Schematic www.ti.com Figure 18. Power Supply Schematic ADS5474 ADX Evaluation Board for Interleaving SLAU247 – August 2008 Submit Documentation Feedback... - Page 27 EVALUATION BOARD/KIT IMPORTANT NOTICE Texas Instruments (TI) provides the enclosed product(s) under the following conditions: This evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION, OR EVALUATION PURPOSES ONLY and is not considered by TI to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards.

- Page 28 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

Need help?

Do you have a question about the ADS5474 and is the answer not in the manual?

Questions and answers