Advertisement

Quick Links

1

U_FPGA

FPGA.SchDoc

A

U_SODIMM

SODIMM.SchDoc

U_CLOCK

CLOCK.SchDoc

U_POWER

POWER.SchDoc

B

U_CONN

CONN.SchDoc

U_CPLD

CPLD.SchDoc

C

PM1

PM2

PM3

FIDU-DOT - small

FIDU-DOT - small

FIDU-DOT - small

PM4

PM5

PM6

FIDU-DOT - small

FIDU-DOT - small

FIDU-DOT - small

D

LOGO1

Serial

TE Logo PRINT Layer

Serial

Serialnumber 6,3 x 6.3mm

LOGO PRINT

1

2

2

3

Title:

TEF1001 - MAIN

Number:

TEF1001

A4

Default

Date:

2017-02-14

Copyright:

Trenz Electronic GmbH

TEF1001.SchDoc

Filename:

3

4

A

B

C

D

Rev.

01

Page1

of

32

4

Advertisement

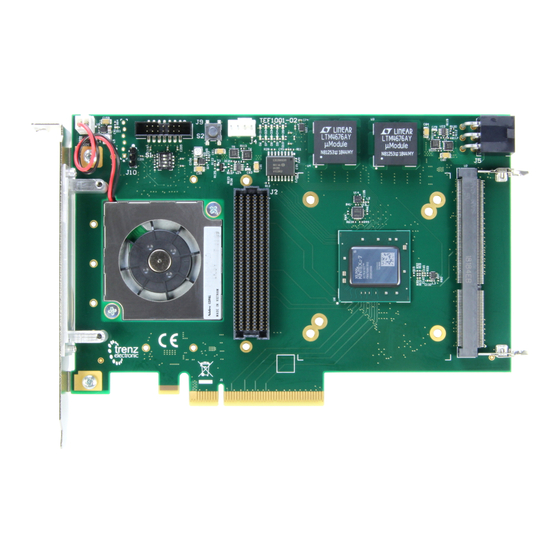

Summary of Contents for Trenz Electronic TEF1001

- Page 1 CLOCK.SchDoc U_POWER POWER.SchDoc U_CONN CONN.SchDoc U_CPLD CPLD.SchDoc FIDU-DOT - small FIDU-DOT - small FIDU-DOT - small Title: TEF1001 - MAIN FIDU-DOT - small FIDU-DOT - small FIDU-DOT - small Number: Rev. TEF1001 LOGO1 Default Serial TE Logo PRINT Layer Serial...

- Page 2 VID1_FMC_VADJ PR9C VID0_FMC_VADJ VCCIO3 PR9D FEX6 PG_FMC_VADJ PL10C PR10C FEX9 EN_FMC_VADJ PL10D PR10D FMC_SCL 10K7 FMC_SDA 10K7 C204 100nF Title: TEF1001 - CPLD C206 C207 Number: Rev. TEF1001 100nF 100nF Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page2 CPLD.SchDoc Filename:...

- Page 3 1K13 1K13 32K4 C160 DDR3_CLK_C_P DDR3_CLK_P 100nF OUT+ 200MHZCLK_EN ST/OE C132 100R 100R OUT- 470nF C161 6.3V DSC1123DL5-200.0000 DDR3_CLK_C_N DDR3_CLK_N 100nF 1K13 1K13 Title: TEF1001 - CLOCK Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page3 CLOCK.SchDoc Filename:...

- Page 4 CLK2B CLK2_P RSVD_GND CLK3A CLK2_N CLK3B SI5338A-B-GMR C108 MGTCLK_5338_C_P MGTCLK_5338_P 100nF PLL_CLK Remove R if not needed 100R C109 MGTCLK_5338_C_N MGTCLK_5338_N 100nF PLL_CLK Title: TEF1001 - CLK-SI5338 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page4 CLK-SI5338.SchDoc Filename:...

- Page 5 Wire to board, 2 pol. housing CPLD JTAG CONNECTOR JCT1 Crimp Terminal 4809, 22-30 AWG JCT2 Crimp Terminal 4809, 22-30 AWG JUMPER2.54-3 LTM_SCL LTM_SDA LTM I2C CONNECTOR Title: TEF1001 - CONN Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page5 CONN.SchDoc...

- Page 6 HB12_P LA15_P HB12_P LA15_N HB12_N LA15_N HB12_N LA16_P LA16_P LA16_N ASP-134486-01, CC-HPC-10 LA16_N LA17_P LA17_P_CC LA17_N LA17_N_CC Title: LA18_P LA18_P_CC TEF1001 - FMC LA18_N LA18_N_CC ASP-134486-01, CC-HPC-10 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page6 FMC.SchDoc Filename:...

- Page 7 GND (Black) VS2 | VS1 | VS0 | Output Voltage FAN 5VDC 45X5MM .7W 1.06CFM Title: ---------------------------------- TEF1001 - FMC_PWR 0 | 0 | 0 | 3.3V 0 | 0 | 1 | 2.5V Single FMC Con. Cooled BB Snap 0 | 1 | 0 | 1.8V...

- Page 8 PERp5 PER5_N PERn5 PET6_P PETp6 PET6_N PETn6 PER6_P PERp6 PER6_N PERn6 PET7_P PETp7 PET7_N PETn7 PER7_P PERp7 PCIE_PRSNTB PER7_N PRSNT2# PERn7 PCIe-8x-kurz Title: TEF1001 - PCIE CONNECTOR Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page8 PCIE_CONN.SchDoc Filename:...

- Page 9 U_FPGA_BANK_12 U_DDR_Banks U_FPGA_MGT_BANKS U_FPGA_POWER FPGA_BANK_12.SchDoc DDR_Banks.SchDoc FPGA_MGT_BANKS.SchDoc FPGA_POWER.SchDoc U_FPGA_BANK_13 U_FPGA_CFG FPGA_BANK_13.SchDoc FPGA_CFG.SchDoc U_FPGA_BANK_14 FPGA_BANK_14.SchDoc U_FPGA_BANK_15 FPGA_BANK_15.SchDoc U_FPGA_BANK_16 FPGA_BANK_16.SchDoc HS1582EB Heatsink Title: TEF1001 - FPGA Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page9 FPGA.SchDoc Filename:...

- Page 10 DXP_0 M2_0 DXN_0 DONE AGND DONE_0 GNDADC_0 330R LI0402E300R-10 PROGRAM_B PROGRAM_B_0 CFGBVS_0 FPGA_JTAG_TDI TDI_0 FPGA_JTAG_TDO TDO_0 FPGA_JTAG_TCK TCK_0 FPGA_JTAG_TMS TMS_0 INIT_B INIT_B_0 XC7K160T-2FBG676I Title: TEF1001 - FPGA_CFG Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page10 FPGA_CFG.SchDoc Filename:...

- Page 11 HA04_P AD25 HA03_P IO_L8P_T1_12 IO_L23P_T3_12 AE25 HA04_N HA03_N IO_L8N_T1_12 IO_L23N_T3_12 AB26 AE22 HA13_P HA06_P IO_L9P_T1_DQS_12 IO_L24P_T3_12 HA13_N AC26 AF22 HA06_N IO_L9N_T1_DQS_12 IO_L24N_T3_12 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_12 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page11 FPGA_BANK_12.SchDoc Filename:...

- Page 12 IO_L7P_T1_13 IO_L22P_T3_13 LA15_N LA16_N IO_L7N_T1_13 IO_L22N_T3_13 LA10_P LA14_P IO_L8P_T1_13 IO_L23P_T3_13 LA10_N LA14_N IO_L8N_T1_13 IO_L23N_T3_13 LA13_P LA12_P IO_L9P_T1_DQS_13 IO_L24P_T3_13 LA13_N LA12_N IO_L9N_T1_DQS_13 IO_L24N_T3_13 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_13 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page12 FPGA_BANK_13.SchDoc Filename:...

- Page 13 BR0 BR1 BR2 BR3 -------------------------------------- REV01 470nF 6.3V FPGA_IIC_SDA FLASH_QSPI_D00 FLASH_QSPI_D01 FPGA_IIC_SCL DNU/RESET FLASH_QSPI_D02 W/VPP/DQ2 FPGA_IIC_OE FLASH_QSPI_D03 HOLD/DQ3 FLASH_QSPI_CS Title: FPGA_CFG_CCLK TEF1001 - FPGA_BANK_14 N25Q256A11ESF40G Number: Rev. TEF1001 100K SPIFLASH Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page13 FPGA_BANK_14.SchDoc Filename:...

- Page 14 IO_L7P_T1_AD10P_15 IO_L22P_T3_A17_15 LA25_N LA30_N IO_L7N_T1_AD10N_15 IO_L22N_T3_A16_15 LA27_P LA33_P IO_L8P_T1_AD3P_15 IO_L23P_T3_FOE_B_15 LA27_N LA33_N IO_L8N_T1_AD3N_15 IO_L23N_T3_FWE_B_15 LA31_P LA32_P IO_L9P_T1_DQS_AD11P_15 IO_L24P_T3_RS1_15 LA31_N LA32_N IO_L9N_T1_DQS_AD11N_15 IO_L24N_T3_RS0_15 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_15 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page14 FPGA_BANK_15.SchDoc Filename:...

- Page 15 IO_L7P_T1_16 IO_L22P_T3_16 HB19_N HB11_N IO_L7N_T1_16 IO_L22N_T3_16 HB20_P HB03_P IO_L8P_T1_16 IO_L23P_T3_16 HB20_N HB03_N IO_L8N_T1_16 IO_L23N_T3_16 HB14_P HB09_P IO_L9P_T1_DQS_16 IO_L24P_T3_16 HB14_N HB09_N IO_L9N_T1_DQS_16 IO_L24N_T3_16 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_16 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page15 FPGA_BANK_16.SchDoc Filename:...

- Page 16 U_FPGA_BANK_32 FPGA_BANK_32.SchDoc U_FPGA_BANK_33 FPGA_BANK_33.SchDoc U_FPGA_BANK_34 FPGA_BANK_34.SchDoc Title: TEF1001 - DDR_BANKS Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page16 DDR_Banks.SchDoc Filename:...

- Page 17 DDR3_DM4 IO_L7N_T1_32 IO_L22N_T3_32 10nF DDR3_D41 AC14 DDR3_D35 IO_L8P_T1_32 IO_L23P_T3_32 AD14 DDR3_DM5 DDR3_D34 IO_L8N_T1_32 IO_L23N_T3_32 DDR3_DQS5_P DDR3_D39 IO_L9P_T1_DQS_32 IO_L24P_T3_32 DDR3_DQS5_N DDR3_D32 IO_L9N_T1_DQS_32 IO_L24N_T3_32 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_32 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page17 FPGA_BANK_32.SchDoc Filename:...

- Page 18 DDR3_CB0 IO_L7N_T1_33 IO_L22N_T3_33 10nF DDR3_A1 AE13 DDR3_CB3 IO_L8P_T1_33 IO_L23P_T3_33 AF13 DDR3_BA2 DDR3_CB2 IO_L8N_T1_33 IO_L23N_T3_33 AF10 DDR3_A7 DDR3_DM8 IO_L9P_T1_DQS_33 IO_L24P_T3_33 DDR3_CB1 IO_L9N_T1_DQS_33 IO_L24N_T3_33 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_33 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page18 FPGA_BANK_33.SchDoc Filename:...

- Page 19 IO_L22P_T3_34 DDR3_D14 DDR3_D0 IO_L7N_T1_34 IO_L22N_T3_34 10nF DDR3_D13 DDR3_D3 IO_L8P_T1_34 IO_L23P_T3_34 DDR3_D12 DDR3_D2 IO_L8N_T1_34 IO_L23N_T3_34 DDR3_DQS1_P DDR3_DM0 IO_L9P_T1_DQS_34 IO_L24P_T3_34 DDR3_DQS1_N DDR3_D1 IO_L9N_T1_DQS_34 IO_L24N_T3_34 XC7K160T-2FBG676I Title: TEF1001 - FPGA_BANK_34 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page19 FPGA_BANK_34.SchDoc Filename:...

- Page 20 DP2_M2C_P DP2_C2M_P MGTXRXP1_116 MGTXTXP1_116 DP2_M2C_N DP2_C2M_N MGTXRXN1_116 MGTXTXN1_116 DP1_M2C_P DP1_C2M_P MGTXRXP2_116 MGTXTXP2_116 DP1_M2C_N DP1_C2M_N MGTXRXN2_116 MGTXTXN2_116 DP0_M2C_P DP0_C2M_P MGTXRXP3_116 MGTXTXP3_116 DP0_M2C_N DP0_C2M_N MGTXRXN3_116 MGTXTXN3_116 XC7K160T-2FBG676I Title: TEF1001_FPGA_MGT_BANKS Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page20 FPGA_MGT_BANKS.SchDoc Filename:...

- Page 21 6.3V VCCAUX VCCAUX VCCAUX VCCAUX 4.7µF 4.7µF 4.7µF 4.7µF 47µF 47µF 47µF VCCAUX 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V VCCAUX_IO_G0 VCCAUX_IO_G0 VCCAUX_IO_G0 Title: TEF1001 - FPGA_POWER Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page21 FPGA_POWER.SchDoc Filename:...

- Page 22 DDR3_DM4 DDR3_DM3 DDR3_DM2 DDR3_DM1 DDR3_DM0 DDR3_CB[0..7] DDR3_D[56..63] DDR3_D[48..55] DDR3_D[40..47] DDR3_D[32..39] DDR3_D[24..31] DDR3_D[16..23] DDR3_D[8..15] DDR3_D[0..7] DDR3_ADDR_CMD 45 OHM Title: DDR3_ADDR_CMD TEF1001 - SODIMM DDR3_A0 DDR3_A4 DDR3_A8 DDR3_A12 DDR3_BA0 DDR3_ODT0 DDR3_RASN DDR3_CKE0 DDR3_CK0_P Number: Rev. TEF1001 DDR3_A1 DDR3_A5 DDR3_A9 DDR3_A13 DDR3_BA1 DDR3_ODT1...

- Page 23 C229 C230 C231 C232 C233 C234 C235 C236 C237 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF Title: TEF1001 - SODIMM_PWR Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page23 SODIMM_PWR.SchDoc Filename:...

- Page 24 U_PWR_4V_1V5 PWR_4V_1V5.SchDoc U_PWR_3V3 PWR_3V3.SchDoc U_PWR_1V PWR_1V.SchDoc U_PWR_MGT PWR_MGT.SchDoc U_PWR_1V8 PWR_1V8.SchDoc U_PWR_5V PWR_5V.SchDoc Title: TEF1001 - POWER Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page24 POWER.SchDoc Filename:...

- Page 25 Connect to load point R = 2.43K / 2 VOUT1CFG VOSNS1 VTRIM1CFG VORB1 Connect to load point SGND SGND SGND SGND LTM4676EY#PBF INTVCC Title: INTVCC TEF1001 - PWR_1V LTM_3V3 VDD33 Number: Rev. TEF1001 SNUB0 VDD25 SNUB1 Default LTM4676EY#PBF LTM4676EY#PBF Date: 2017-02-14 Copyright:...

- Page 26 Connect to load point VOUT1CFG VOSNS1 32K4 VTRIM1CFG VORB1 Connect to load point 3K24 SGND SGND SGND SGND LTM4676EY#PBF Title: INTVCC TEF1001 - PWR_4V_1V5 INTVCC LTM4676EY#PBF Number: Rev. TEF1001 LTM2_3V3 VDD33 SNUB0 Default VDD25 SNUB1 Date: 2017-02-14 Copyright: Trenz Electronic GmbH...

- Page 27 4.7µF 10nF 4.7µF 6.3V 6.3V 6.3V 6.3V U19 TPS79901DRV ClassName: Power MGTVCCAUX_FPGA C150 C240 C151 1.818V 4.7µF 47pF 4.7µF 6.3V 6.3V 143K GNDGND Title: TEF1001 - PWR_MGT Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page27 PWR_MGT.SchDoc Filename:...

- Page 28 EN_1V8 NC(SW) NC(SW) 143K NC(SW) LLM/SYNC RLLM NC(SW) NC(SW) NC(SW) C155 NC(SW) AGND 47nF NC(SW) PGND PGND PGND PGND PGND PGND PGND EN6347QI Title: TEF1001 - PWR_1V8 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page28 PWR_1V8.SchDoc Filename:...

- Page 29 AGND NC(SW) PGND PGND PGND PGND PGND PGND PGND EN6347QI ClassName: Power 3.34V 2,2µH C208 47µF 10K7 6.3V 22µF AGND AGND 4K22 TPS62170DSG Title: TEF1001 - PWR_3V3 Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page29 PWR_3V3.SchDoc Filename:...

- Page 30 ClassName: Power 2,2µH 24K3 47µF C159 6.3V 22µF AGND AGND TPS62170DSG Title: TEF1001 - PWR_5V Number: Rev. TEF1001 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page30 PWR_5V.SchDoc Filename:...

- Page 31 GBTCLK1_M2C MGT_BANK_116 MGTREFCLK1_116 CLK0_M2C BANK_15 SRCC (VCCO= VADJ) CONNECTOR CLK1_M2C BANK_15 SRCC (VCCO= VADJ) Title: CLK2_BIDIR BANK_13 TEF1001 - Clock Overview SRCC (VCCO= VADJ) Number: Rev. TEF1001 Default CLK3_BIDIR BANK_13 Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page31 SRCC (VCCO= VADJ) CLOCKS OVERVIEW.SchDoc...

- Page 32 FPGA - MGTAVCC 1.0V / 3A BIAS TPS74401RGW 1.2V FPGA - MGTAVTT 1.2V / 3A BIAS DDR3 VDD FPGA - BANK_32 Title: TEF1001 - Power Ens_PGs_COMMs FPGA - BANK_33 Number: Rev. TEF1001 FPGA - BANK_34 Default Date: 2017-02-14 Copyright: Trenz Electronic GmbH Page32 POWER_ENs_PGs OVERVIEW.SchDoc...

Need help?

Do you have a question about the TEF1001 and is the answer not in the manual?

Questions and answers