Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Intel MAX 10 FPGA

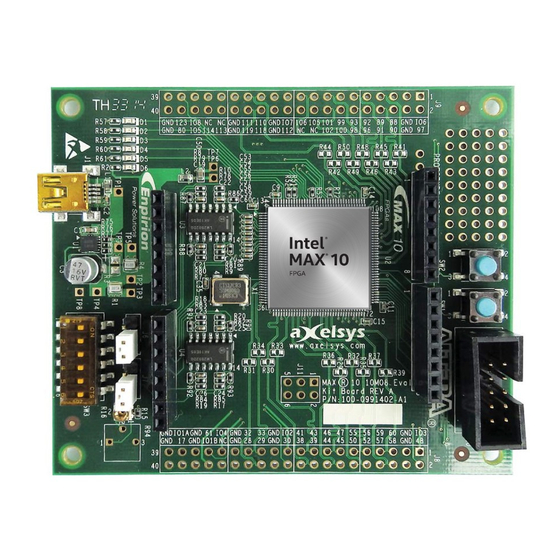

- Page 1 MAX 10 FPGA Device Overview M10-OVERVIEW 2017.02.21 Subscribe Send Feedback...

-

Page 2: Table Of Contents

1.11 Embedded Memory Blocks..................11 1.12 Clocking and PLL....................11 1.13 FPGA General Purpose I/O..................12 1.14 External Memory Interface................... 12 1.15 Configuration......................13 1.16 Power Management..................... 13 1.17 Document Revision History for MAX 10 FPGA Device Overview........13 MAX 10 FPGA Device Overview... -

Page 3: Max 10 Fpga Device Overview

Intel's standard warranty, but reserves the right to make changes to any products and services Registered at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. -

Page 4: Summary Of Max 10 Device Features

External memory interface (EMIF) Supports up to 600 Mbps external memory interfaces: continued... 1 EMIF is only supported in selected MAX 10 device density and package combinations. Refer to the External Memory Interface User Guide for more information. MAX 10 FPGA Device Overview... -

Page 5: Max 10 Device Ordering Information

153 : 153 pins, 8 mm x 8 mm Note: The –I6 and –A6 speed grades of the MAX 10 FPGA devices are not available by default in the Quartus Prime software. Contact your local Intel sales representatives for support. -

Page 6: Max 10 Device Feature Options

Dedicated Transmitter Emulated Transmitter Dedicated Receiver Internal Configuration Image — 2 The maximum possible value including user flash memory and configuration flash memory. For more information, refer to MAX 10 User Flash Memory User Guide. MAX 10 FPGA Device Overview... -

Page 7: Max 10 Devices I/O Resources Per Package

MAX 10 High-Speed LVDS I/O User Guide 1.6 MAX 10 Vertical Migration Support Vertical migration supports the migration of your design to other MAX 10 devices of different densities in the same package with similar I/O and ADC resources. MAX 10 FPGA Device Overview... -

Page 8: Max 10 I/O Vertical Migration Support

Dual ADC Device: Each ADC (ADC1 and ADC2) supports 1 dedicated analog input pin and 8 dual function pins. Single ADC Device: Single ADC that supports 1 dedicated analog input pin and 16 dual function pins. Single ADC Device: Single ADC that supports 1 dedicated analog input pin and 8 dual function pins. MAX 10 FPGA Device Overview... -

Page 9: Logic Elements And Logic Array Blocks

Register Chain Clock Enable Output Select labclk1 LE Carry-Out labclk2 labclkena1 labclkena2 1.8 Analog-to-Digital Converter MAX 10 devices feature up to two ADCs. You can use the ADCs to monitor many different signals, including on-chip temperature. MAX 10 FPGA Device Overview... -

Page 10: User Flash Memory

You can control the operation of the embedded multiplier blocks using the following options: • Parameterize the relevant IP cores with the Quartus Prime parameter editor • Infer the multipliers directly with VHDL or Verilog HDL System design features provided for MAX 10 devices: MAX 10 FPGA Device Overview... -

Page 11: Embedded Memory Blocks

— Suites of common video and image processing functions • Complete reference designs for end-market applications • DSP Builder for Intel FPGAs interface tool between the Quartus Prime software and the MathWorks Simulink and MATLAB design environments • DSP development kits 1.11 Embedded Memory Blocks... -

Page 12: Fpga General Purpose I/O

External Memory Interface Spec Estimator Provides a parametric tool that allows you to find and compare the performance of the supported external memory interfaces in Intel FPGAs. 3 The device hardware supports SRAM. Use your own design to interface with SRAM devices. -

Page 13: Configuration

• Reduces dynamic power consumption when certain applications are in standby mode controller scheme • Provides a fast wake-up time of less than 1 ms. 1.17 Document Revision History for MAX 10 FPGA Device Overview Date Version Changes February 2017 2017.02.21... - Page 14 Added memory initialization feature for Flash and Analog devices. • Added maximum data retention capacity of up to 20 years for UFM feature. • Added maximum operating frequency of 7.25 MHz for serial interface for UFM feature. September 2014 2014.09.22 Initial release. MAX 10 FPGA Device Overview...

Need help?

Do you have a question about the MAX 10 FPGA and is the answer not in the manual?

Questions and answers