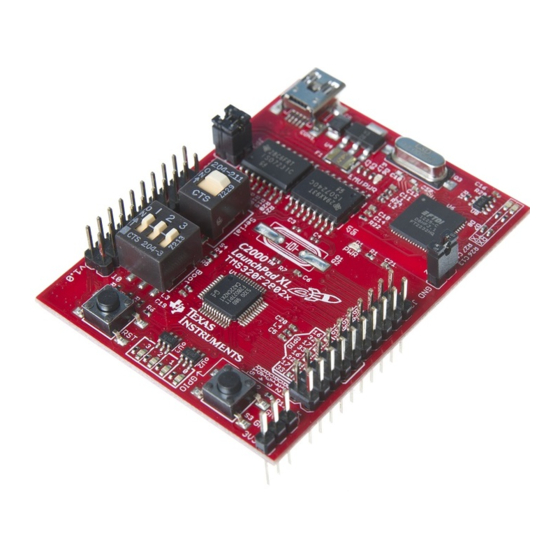

Texas Instruments TMS320 Series User Manual

Piccolo local interconnect network lin module

Hide thumbs

Also See for TMS320 Series:

- User manual (288 pages) ,

- User manual (126 pages) ,

- User manual (88 pages)

Summary of Contents for Texas Instruments TMS320 Series

- Page 1 Preliminary TMS320F2803x Piccolo Local Interconnect Network (LIN) Module User's Guide Literature Number: SPRUGE2A May 2009 – Revised June 2009...

- Page 2 Preliminary SPRUGE2A – May 2009 – Revised June 2009 Submit Documentation Feedback...

-

Page 3: Table Of Contents

Contents ............................Preface ..................... Introduction and Features ........................Purpose ........................Features ......................Block Diagram ......................... Standards .......................... Operation ......................Message Frame ......................Synchronizer ........................ Baud Rate ...................... Header Generation .................... Extended Frames Handling ......................Timeout Control .................... TXRX Error Detector (TED) .................. - Page 4 Preliminary www.ti.com ..................6.18 LIN Mask Register (LINMASK) ..................6.19 LIN Identification Register (LINID) ................6.20 LIN Transmit Buffer 0 Register (LINTD0) ................6.21 LIN Transmit Buffer 1 Register (LINTD1) ..............6.22 Maximum Baud Rate Selection Register (MBRS) ............... 6.23 I/O Design For Test Control (IODFTCTRL) Register ....................

- Page 5 Preliminary www.ti.com List of Figures ....................SCI/BLIN Block Diagram ........LIN Protocol Message Frame Format: Master Header and Slave Response ................Header Fields: Synch Break, Synch, and ID ................Response Format of LIN Message Frame ..................Message Header in Terms of T ........................

- Page 6 Preliminary www.ti.com List of Tables ............Response Length with SCIFORMAT(18–16) Programming ....................Timeout Values in T Units ......................SCI/BLIN Interrupts ....................... LIN Registers ............SCI Global Control Register 0 (SCIGCR0) Field Descriptions ............SCI Global Control Register (SCIGCR1) Field Descriptions ....................

-

Page 7: Preface

Preliminary Preface SPRUGE2A – May 2009 – Revised June 2009 Read This First This document describes the Local Interconnect Network (LIN) Module. About This Manual The TMS320C2000™ is part of the TMS320™ family. Notational Conventions This document uses the following conventions. •... - Page 8 Preliminary Related Documentation www.ti.com SPRUGE2— TMS320x2803x Piccolo Local Interconnect Network (LIN) Module Reference Guide describes the operation of the Local Interconnect Network (LIN) Module. SPRUFK8— TMS320x2803x Piccolo Enhanced Quadrature Encoder Pulse (eQEP) Reference Guide describes the operation of the Enhanced Quadrature Encoder Pulse (eQEP) . SPRUGL7—...

-

Page 9: Introduction And Features

Preliminary User's Guide SPRUGE2A – May 2009 – Revised June 2009 Local Interconnect Network (LIN) Module This document describes the buffered local interconnect network (BLIN) module. Since this module can also operate like a conventional serial communications interface (SCI) port, it is referred to as the SCI/BLIN module in this document. -

Page 10: Block Diagram

Preliminary Introduction and Features www.ti.com – Bit error – Bus error – No-response error – Checksum error – Synchronization field error – Parity error • 2 Interrupt lines with priority encoding for: – Receive – Transmit – ID, error, and status •... -

Page 11: Standards

Preliminary Introduction and Features www.ti.com Figure 1. SCI/BLIN Block Diagram READ DATA BUS WRITE DATA BUS ADDRESS BUS INTERFACE CHECKSUM CALCULATOR ID PARITY CHECKER BIT MONITOR TXRX ERROR DETECTOR (TED) TIMEOUT CONTROL COUNTER LINRX/ SCIRX COMPARE 8 RECEIVE MASK BUFFERS FILTER 8 TRANSMIT LINTX/... -

Page 12: Operation

Preliminary Operation www.ti.com Operation The SCI/BLIN module can be used in LIN mode or SCI (UART) mode. The enhancements for baud generation and additional receive/transmit buffers necessary for LIN mode operation are part of the enhanced buffered SCI/BLIN module. Note: To make a determination of the bit value, 16 samples for each bit are taken with majority vote on samples 8, 9, and 10. -

Page 13: Synchronizer

Preliminary Operation www.ti.com 2.1.2 Response The format of the response is as illustrated in Figure 4. There are two types of fields in a response: data and checksum. The data field consists of exactly one data byte, one start bit, and one stop bit, for a total of 10 bits. -

Page 14: Baud Rate

Preliminary Operation www.ti.com Baud Rate The LIN module is clocked at a frequency of one-half the CPU clock (SYSCLKOUT). i.e. LIN Module input clock (LM_CLK) = SYSCLKOUT/2. For a 60 MHz device, LM_CLK = 30 MHz. The transmission baud rate of any node is configured by the CPU in the beginning; this defines the bit time T . -

Page 15: Message Header In Terms Of T

Preliminary Operation www.ti.com – The synchronization break delimiter (SDEL) consists of a minimum of 1 (recessive) high bit to a maximum of 4 recessive bits. The delimiter marks the end of the synchronization break field. The synch break delimiter length depends on the 2-bit SDEL value in the LINCOMP register. •... -

Page 16: Measurements For Synchronization

Preliminary Operation www.ti.com 2.4.1 Event Triggered Frame Handling The LIN 2.0 protocol uses event-triggered frames that may occasionally cause collisions. Event-triggered frames have to be handled in software. If no slave answers to an event triggered frame header, the master node will set the NRE flag and a NRE interrupt will occur if enabled. -

Page 17: Synchronization Validation Process And Baud Rate Adjustment

Preliminary Operation www.ti.com Figure 8. Synchronization Validation Process and Baud Rate Adjustment LINRX = 1 Wait for falling edge On LINRX Increment Counter while LINRX = 0 Counter Reset Counter >= 11T LINRX = 0 Increment Counter On LINRX Save counter (SBRK_count) and reset it On 1st LINRX falling edge... -

Page 18: Extended Frames Handling

Preliminary Operation www.ti.com The BAUD_count value is shifted 3 times to the right and rounded using the first insignificant bit to obtain unit. If the ADPAT bit is set then, the detected baud rate is compared to the programmed baud rate. During the header reception processing as illustrated in Figure 8, if the measured BRK_count value is less... -

Page 19: Timeout Control

Preliminary Operation www.ti.com For the sending node, the automatic embedding of checksum should be possible when the SCIGCR2[16] bit is set. For the receiving node, a checksum comparison should be forced when the SCIGCR2[17] bit is set; see Figure Note: The LIN 2.0 enhanced checksum does not apply to the reserved identifiers. -

Page 20: Txrx Error Detector (Ted)

Preliminary Operation www.ti.com Table 2. Timeout Values in T Units (continued) DATA_FIELD FRAME_MIN FRAME_MAX Note: The length coding of the ID field does not apply to two extended frame identifiers, with ID fields 0x3E (62) and 0x3F (63). In these cases, the ID field can be followed by an arbitrary number of data byte fields. -

Page 21: Txrx Error Detector

Preliminary Operation www.ti.com Figure 11. TXRX Error Detector ID-Parity-Error Parity D-Parity-Error Flag Checker ID-Parity Interrupt (if enabled) Checksum Checksum-Error Flag VBAT Calculator Checksum-Error Int. (if enabled) SCIRXSHF Bit Monitor Bit-Error Flag Bit-Error Int. (if enabled) LIN Bus Bus-Error Flag Bus-Error Int. (if enabled) SCITXSHF 2.7.2 Physical Bus Errors... -

Page 22: Classic Checkbyte Generation At Transmitting Node

Preliminary Operation www.ti.com Figure 12. Classic Checkbyte Generation at Transmitting Node Response Checksum 1 to 8 Data Fields Field Checkbyte Invert Modulo-256 Sum Figure 13. LIN 2.0-Compliant Checkbyte Generation at Transmitting Node From Response Header Checksum ID Field 1 to 8 Data Fields Field Checkbyte Invert... -

Page 23: Message Filtering And Validation

Preliminary Operation www.ti.com Message Filtering and Validation Message filtering uses the entire identifier to determine which nodes will participate in a response, either receiving or transmitting a response. Therefore, two acceptance masks are used as shown in Figure Figure 14. ID Reception, Filtering and Validation Parity Enable Parity ID Parity Error... -

Page 24: Receive Buffers

Preliminary Operation www.ti.com Note: When the HGEN CTRL bit = 0, the LIN nodes compare the received ID to the ID-BYTE field in the LINID register, and uses the RX-ID MASK and the TX-ID MASK in the LINMASK register to filter the bits of the identifier that should not be compared. If there is an RX match with no parity error and the RXENA (SCIGCR1[24]) bit is set, there will be an ID RX flag and an interrupt will be triggered if enabled. -

Page 25: 2.10 Transmit Buffers

Preliminary Operation www.ti.com Figure 15. Receive Buffers RX Ready Flag SCIRXSHF Checksum Flag Calculator No Receive 3-Bit Errors Compare MBUF Mode 3-Bit Counter Not MBUF Mode The checkbyte following the data bytes should be validated by the checksum calculator in the TED logic. The checksum error flag indicates a checksum error and a CE interrupt will be generated if enabled in the SCISETINT register. -

Page 26: Interrupts

Preliminary Interrupts www.ti.com Figure 16. Transmit Buffers SCITXSHF Checksum CE Flag Calculator TX Ready Flag 3-Bit Compare MBUF Mode 3-Bit Counter Not MBUF Mode The checkbyte will be generated by the checksum calculator and sent after the data-fields transmission is finished. -

Page 27: General Interrupt Scheme

Preliminary Interrupts www.ti.com Figure 17. General Interrupt Scheme INT 1 INT0 Priority Encoder 1 INT1 INT2 INT3 Module INT4 INT5 INT 0 INT6 Priority Encoder 0 INT7 INT8 INT9 SCISETINT INT10 INT11 SCICLRINT INT12 SCISETINTL INT13 SCICLRL INT14 INT15 SCIINTFLR INT16 SCIINTVECT0 SCIINTVECT1... -

Page 28: Low-Power Mode

Preliminary Low-Power Mode www.ti.com For each of the interrupt sources FLAGx, the SCISETINT and SCICLRINT register pair is used to enable/ disable the interrupt. For each source, the interrupt line can be chosen to be INT0 or INT1 with the SCISETINTLVL and SCICLRINTLVL register pair. -

Page 29: Entering Sleep Mode

Preliminary Low-Power Mode www.ti.com Note: If the module needs to be able to wake up upon a wake-up request, the following sequence should be followed: Enable wakeup interrupt in the SCISETINT register (Section 6.4). Set the POWERDOWN bit. The SCI/BLIN module can be put in either local or global low-power mode. Global low-power mode is asserted by the system and is not controlled by the SCI/BLIN module. -

Page 30: Wakeup Timeouts

Preliminary Emulation Mode www.ti.com Figure 20. Wakeup Signal Generation Wakeup Signal SYNCH Break Bus in Sleep Mode Bus in Operational Mode WUSIG INITIALIZE Assuming a perfect bus with no noise or loading effects, a write of 0xF0 to TD0 will load the transmitter to meet the wakeup signal timing requirement for TWUSIG. -

Page 31: Sci/Blin Control Registers

Preliminary SCI/BLIN Control Registers www.ti.com SCI/BLIN Control Registers The SCI/BLIN module registers are based on the SCI registers, with added functionality registers enabled by the LIN MODE bit in the SCIGCR1 register. These registers are accessible in 8-, 16-, and 32-bit reads or writes. The SCI/BLIN is controlled and accessed through the registers listed in Table 4. -

Page 32: Sci Global Control Register 0 (Scigcr0)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Global Control Register 0 (SCIGCR0) Reserved Reserved RESET R/W-0 SCI Global Control Register (SCIGCR1) Reserved TXENA RXENA R/W-0 R/W-0 Reserved CONT LOOP BACK R/W-0 R/W-0 Reserved STOPEXT HGEN CTRL CTYPE MBUF MODE ADAPT SLEEP FRAME R/WL-0 R/WL-0... -

Page 33: Sci Clear Interrupt Register (Sciclearint)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Clear Interrupt Register (SCICLEARINT) CLR BE INT SET PBE INT CLR CE INT CLRISFE INT CLR RE INT CLR FE INT CLR OE INT CLR PE INT R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0 Reserved Reserved... -

Page 34: Sci Clear Interrupt Level Register (Sciclearintlvl)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Clear Interrupt Level Register (SCICLEARINTLVL) CLR BE INT CLR PBE INT CLR CE INT CLR ISFE INT CLR NRE INT CLR FE INT CLR OE INT CLR PE INT R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0... -

Page 35: Sci Format Control Register (Sciformat)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Format Control Register (SCIFORMAT) Reserved LENGTH R/W-0 Reserved CHAR R/WC-0 Baud Rate Selection Register (BRSR) Reserved R/W-0 R/W-0 R/W-0 Receiver Emulation Data Buffer (SCIED) Reserved Reserved Receiver Data Buffer (SCIRD) Reserved Reserved R/WC-0 Transmit Data Buffer Register (SCITD) Reserved Reserved R/W-0... -

Page 36: Lin Mask Register (Linmask)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Pin I/O Control Register 2 (SCIPIO2) Reserved Reserved TX IN RX IN Reserved LIN Compare Register (LINCOMPARE) Reserved Reserved SDEL Reserved SBREAK R/WL-0 R/WL-0 LIN Receive Buffer 0 Register (LINRD0) LIN Receive Buffer 1 Register (LINRD1) LIN Mask Register (LINMASK) Reserved RX ID MASK... -

Page 37: Lin Identification Register (Linid)

Preliminary SCI/BLIN Control Registers www.ti.com LIN Identification Register (LINID) Reserved RECEIVED ID ID-SlaveTask BYTE ID BYTE R/WL-0 R/WL-0 LIN Transmit Buffer 0 Register (LINTD0) R/W-0 R/W-0 R/W-0 R/W-0 LIN Transmit Buffer 1 Register (LINTD1) R/W-0 R/W-0 R/W-0 R/W-0 Maximum Baud Rate Selection Register (MBRS) Reserved Reserved R/WL-0... -

Page 38: I/O Design For Test Control (Iodftctrl) Register

Preliminary SCI/BLIN Control Registers www.ti.com I/O Design For Test Control (IODFTCTRL) Register Bit Error Enable Physical Bus Checksum Inconsistent Reserved Frame Error Parity Error Break Detect Error Enable Error Enable Synch Field Enable Enable Error Enable Error Enable R/W-0 R/W-0 R/W-0 R/W-0 R/W-0... -

Page 39: Sci Global Control Register 0 (Scigcr0)

Preliminary SCI/BLIN Control Registers www.ti.com SCI Global Control Register 0 (SCIGCR0) The SCI Global Control Register 0 (SCIGCR0) is shown in Figure 21 and described in Table Figure 21. SCI Global Control Register 0 (SCIGCR0) Reserved Reserved RESET R/W-0 LEGEND: R/W = Read/Write; R = Read only; -n = value after reset Table 5. -

Page 40: Sci Global Control Register (Scigcr1) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Table 6. SCI Global Control Register (SCIGCR1) Field Descriptions Field Value Description 31-26 Reserved Reads return zero and writes have no effect. TXENA Transmit enable. This bit is effective in LIN and SCI modes. Data is transferred from SCITD or the TDy (with y=0, 1,...7) buffers in LIN mode to the SCITXSHF shift out register only when the TXENA bit is set. - Page 41 Preliminary SCI/BLIN Control Registers www.ti.com Table 6. SCI Global Control Register (SCIGCR1) Field Descriptions (continued) Field Value Description HGEN CTRL LIN mode bit. This bit controls the type of Mask filtering comparison. ID filtering using ID-Byte. RECID and ID-BYTE fields in LINID register are used for detecting a match (using TX/RX MASK values).

- Page 42 Preliminary SCI/BLIN Control Registers www.ti.com Table 6. SCI Global Control Register (SCIGCR1) Field Descriptions (continued) Field Value Description LIN MODE LIN mode This bit controls the module mode of operation. LIN mode is disabled; SCI compatibility mode is enabled. LIN mode is enabled; SCI compatibility mode is disabled. CLK_MASTER SCI internal clock enable or LIN Master/Slave configuration.

- Page 43 Preliminary SCI/BLIN Control Registers www.ti.com Table 6. SCI Global Control Register (SCIGCR1) Field Descriptions (continued) Field Value Description COMM MODE SCI/BLIN communication mode bit. In compatibility mode, it selects the SCI communication mode. In LIN mode it selects length control option for ID-field bits ID4 and ID5.

-

Page 44: Bit

Preliminary SCI/BLIN Control Registers www.ti.com Table 7. SCI Receiver Status Flags SCI Flag Register Value After SW nRESET SCIFLR ISFE SCIFLR SCIFLR SCIFLR SCIFLR SCIFLR RXWAKE SCIFLR RXRDY SCIFLR BUSY SCIFLR IDLE SCIFLR WAKE UP SCIFLR BRKDT SCIFLR The flags are frozen with their reset value while SW nRESET = 0. Table 8. - Page 45 Preliminary SCI/BLIN Control Registers www.ti.com Table 9. SCI Global Control Register (SCIGCR2) Field Descriptions (continued) Field Value Description Compare Checksum. LIN mode only. This bit is used by the receiver for extended frames to trigger a checksum compare. The user will initiate this transaction by writing a one to this bit. In non multibuffer mode, once the CC bit is set, the checksum will be compared on the byte that is currently being received, expected to be the checkbyte.

-

Page 46: Sci Set Interrupt Register (Scisetint)

Preliminary SCI/BLIN Control Registers www.ti.com Figure 24. SCI Set Interrupt Register (SCISETINT) SET BE INT SET PBE INT SET CE INT SETISFE INT SET NRE INT SET FE INT SET OE INT SET PE INT R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0... - Page 47 Preliminary SCI/BLIN Control Registers www.ti.com Table 10. SCI Set Interrupt Register (SCISETINT) Field Descriptions (continued) Field Value Description SET ISFE INT Set inconsistent-synch-field-error interrupt. This bit is effective in LIN mode only. Setting this bit enables the SCI/BLIN module to generate an interrupt when there is an inconsistent synch field error.

- Page 48 Preliminary SCI/BLIN Control Registers www.ti.com Table 10. SCI Set Interrupt Register (SCISETINT) Field Descriptions (continued) Field Value Description SET ID INT LIN mode only. This bit is set to enable interrupt once a valid matching identifier is received see Section 2.8 more details.

- Page 49 Preliminary SCI/BLIN Control Registers www.ti.com Table 10. SCI Set Interrupt Register (SCISETINT) Field Descriptions (continued) Field Value Description SET TIMEOUT Set timeout interrupt. This bit is effective in LIN mode only. Setting this bit enables the SCI/BLIN to generate an interrupt when no LIN bus activity occurs for at least four seconds.

-

Page 50: Sci Clear Interrupt Register (Sciclearint)

Preliminary SCI/BLIN Control Registers www.ti.com Figure 25. SCI Clear Interrupt Register (SCICLEARINT) CLR BE INT SET PBE INT CLR CE INT CLRISFE INT CLR RE INT CLR FE INT CLR OE INT CLR PE INT R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0... - Page 51 Preliminary SCI/BLIN Control Registers www.ti.com Table 11. SCI Clear Interrupt Register (SCICLEARINT) Field Descriptions (continued) Field Value Description CLR ISFE INT Clear Inconsistent-Synch-Field-Error Interrupt. LIN mode only. This bit disables the ISFE interrupt when set. Normal and EALLOW mode (read): Interrupt is disabled Interrupt is enabled Normal and EALLOW mode (write):...

- Page 52 Preliminary SCI/BLIN Control Registers www.ti.com Table 11. SCI Clear Interrupt Register (SCICLEARINT) Field Descriptions (continued) Field Value Description CLR ID INT LIN mode only. This bit disables the ID interrupt when set. Normal and EALLOW mode (read): interrupt is disabled interrupt is enabled Normal and EALLOW mode (write): leaves the corresponding bit unchanged...

- Page 53 Preliminary SCI/BLIN Control Registers www.ti.com Table 11. SCI Clear Interrupt Register (SCICLEARINT) Field Descriptions (continued) Field Value Description CLR TIMEOUT Clear Timeout interrupt. LIN mode only. Setting this bit disables the timeout (LIN bus idle) interrupt. Normal and EALLOW mode (read): Interrupt is disabled Interrupt is enabled Normal and EALLOW mode (write):...

-

Page 54: Sci Set Interrupt Level Register (Scisetintlvl)

Preliminary SCI/BLIN Control Registers www.ti.com Figure 26. SCI Set Interrupt Level Register (SCISETINTLVL) SET BE INT SET PBE INT SET CE INT SET ISFE INT SET NRE INT SET FE INT SET OE INT SET PE INT Reserved Reserved SET ID INT Reserved SET RX INT SET TX INT... - Page 55 Preliminary SCI/BLIN Control Registers www.ti.com Table 12. SCI Set Interrupt Level Register (SCISETINTLVL) Field Descriptions (continued) Field Value Description SET ISFE INT Set Inconsistent-Synch-Field-Error Interrupt Level. LIN mode only. Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line Normal and EALLOW mode (write): Leaves the corresponding bit unchanged...

- Page 56 Preliminary SCI/BLIN Control Registers www.ti.com Table 12. SCI Set Interrupt Level Register (SCISETINTLVL) Field Descriptions (continued) Field Value Description SET RX INT LVL Set Receiver interrupt Level. Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line Normal and EALLOW mode (write): Leaves the corresponding bit unchanged Set interrupt level to line INT1...

-

Page 57: Sci Clear Interrupt Level Register (Sciclearintlvl)

Preliminary SCI/BLIN Control Registers www.ti.com Table 12. SCI Set Interrupt Level Register (SCISETINTLVL) Field Descriptions (continued) Field Value Description SET BRKDT INT Set Break-detect interrupt Level. Compatible mode only. Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line Normal and EALLOW mode (write): Leaves the corresponding bit unchanged... - Page 58 Preliminary SCI/BLIN Control Registers www.ti.com Table 13. SCI Clear Interrupt Level Register (SCICLEARINTLVL) Field Descriptions (continued) Field Value Description CLR PBE INT Clear Physical Bus Error Interrupt Level. LIN mode only. Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line Normal and EALLOW mode (write): Normal and EALLOW mode (write):...

- Page 59 Preliminary SCI/BLIN Control Registers www.ti.com Table 13. SCI Clear Interrupt Level Register (SCICLEARINTLVL) Field Descriptions (continued) Field Value Description CLR PE INT LVL Clear Parity Error Interrupt Level. Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line Normal and EALLOW mode (write): Leaves the corresponding bit unchanged Reset interrupt level to line INT0...

- Page 60 Preliminary SCI/BLIN Control Registers www.ti.com Table 13. SCI Clear Interrupt Level Register (SCICLEARINTLVL) Field Descriptions (continued) Field Value Description Reserved These bits are always read as 0. Writes have no effect. CLR TIMEOUT Clear Timeout interrupt Level. INT LVL LIN mode only Normal and EALLOW mode (read): Interrupt level mapped to INT0 line Interrupt level mapped to INT1 line...

-

Page 61: Sci Flags Register (Sciflr)

Preliminary SCI/BLIN Control Registers www.ti.com Figure 28. SCI Flags Register (SCIFLR) ISFE R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/WL-0 R/W-0 R/W-0 R/W-0 Reserved Reserved RX ID TX ID RX WAKE TX EMPTY TX WAKE RX RDY TX RDY R/WL-0 R/WL-0 R/WC-0 R/W-1 R/WC-0 R/W-0 R/W-1... - Page 62 Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description Checksum Error Flag. LIN mode only. This bit is set when there is checksum error detected by a receiving node. This is detected by the TED logic. See Section 2.7 , for more information.

- Page 63 Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description Overrun error flag. This bit is effective in LIN or SCI-compatible mode. This bit is set when the transfer of data from SCIRXSHF to SCIRD overwrites unread data already in SCIRD or the RDy buffers. Detection of an overrun error causes the LIN to generate an error interrupt if the SET OE INT bit is one.

- Page 64 Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description RXWAKE Receiver wakeup detect flag. Compatible mode only. The SCI sets this bit to indicate that the data currently in SCIRD is an address.

- Page 65 Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description TXRDY Transmitter buffer register ready flag. When set, this bit indicates that the transmit buffer(s) register (SCITD in compatibility mode and LINTDO, LINTD1 in MBUF mode) is/are ready to get another character from a CPU write. In compatibility mode writing data to SCITD automatically clears this bit.

- Page 66 Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description TIMEOUT LIN Bus IDLE timeout flag. LIN mode only. This bit is set if there is no LIN bus activity for at least 4 seconds. LIN bus activity being a transition from recessive to dominant.

-

Page 67: Sci Interrupt Vector Offset 0 (Sciintvect0)

Preliminary SCI/BLIN Control Registers www.ti.com Table 14. SCI Flags Register (SCIFLR) Field Descriptions (continued) Field Value Description BRKDT SCI break-detect flag. Compatible mode only This bit is set when the SCI detects a break condition on the LINRX pin. A break condition occurs when the LINRX pin remains continuously low for at least 10 bits after a missing first stop bit, that is, after a framing error. -

Page 68: Sci Interrupt Vector Offset 1 (Sciintvect1)

Preliminary SCI/BLIN Control Registers www.ti.com Figure 30. SCI Interrupt Vector Offset 1 (SCIINTVECT1) Reserved Reserved INTVECT1 LEGEND: R/W = Read/Write; R = Read only; -n = value after reset Table 16. SCI Interrupt Vector Offset 1 (SCIINTVECT1) Field Descriptions Field Value Description 31-5... -

Page 69: Baud Rate Selection Register (Brsr)

Preliminary SCI/BLIN Control Registers www.ti.com Table 17. SCI Format Control Register (SCIFORMAT) Field Descriptions (continued) Field Value Description 18-16 LENGTH Frame length control bits. In LIN mode, these bits indicate the number of bytes in the response field from 1 to 8 bytes. In buffered SCI mode, these bits indicate the number of characters. -

Page 70: Receiver Emulation Data Buffer (Scied)

Preliminary SCI/BLIN Control Registers www.ti.com Table 18. Baud Rate Selection Register (BRSR) Field Descriptions Field Value Description 31-28 Reserved Reads return zero and writes have no effect. 27-24 0-3h SCI/BLIN 4-bit Fractional Divider Selection. These bits are effective in LIN or SCI asynchronous mode. These bits are used to select a baud rate for the SCI/BLIN module, and they are a fractional part for the baud rate specification. -

Page 71: Receiver Data Buffer (Scird)

Preliminary SCI/BLIN Control Registers www.ti.com Table 20. Receiver Emulation Data Buffer (SCIED) Field Descriptions Field Value Description 31-8 Reserved Reads return zero and writes have no effect. 0–FFh Receiver Emulation Data. This bit is effective in SCI-compatible mode only. Reading SCIED(7–0) does not clear the RXRDY flag. -

Page 72: Transmit Data Buffer Register (Scitd) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Figure 35. Transmit Data Buffer Register (SCITD) Reserved Reserved R/W-0 LEGEND: R/W = Read/Write; R = Read only; W = Write in SCI-compatible mode only; -n = value after reset Table 22. Transmit Data Buffer Register (SCITD) Field Descriptions Field Value Description... -

Page 73: Lin Compare Register (Lincompare) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Table 23. SCI Pin I/O Control Register 2 (SCIPIO2) Field Descriptions (continued) Field Value Description RX IN Receive data in. . This bit is effective in LIN or SCI-compatible mode. This bit contains the current value on the SCIRX pin The SCIRX pin is at logic low (0). -

Page 74: Lin Receive Buffer 0 Register (Linrd0) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Table 24. LIN Compare Register (LINCOMPARE) Field Descriptions (continued) Field Value Description SBREAK 3-bit Synch Break Extend. LIN mode only. These bits are used to configure the number of T for the synch break to extend bits the minimum 13 T in the Synch Field to a maximum of 20 T... -

Page 75: Lin Receive Buffer 1 Register (Linrd1) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com 6.17 LIN Receive Buffer 1 Register (LINRD1) The LIN Receive Buffer 1 Register (LINRD1) is shown in Figure 39 and described in Table Figure 39. LIN Receive Buffer 1 Register (LINRD1) LEGEND: R/W = Read/Write; R = Read only; -n = value after reset Table 26. -

Page 76: Lin Identification Register (Linid) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Table 27. LIN Mask Register (LINMASK) Field Descriptions (continued) Field Value Description 23-16 RX ID MASK 0–FFh Receive ID mask. LIN mode only. This 8-bit mask is used for filtering an incoming ID message and compare it to the ID-byte. -

Page 77: Lin Transmit Buffer 0 Register (Lintd0) Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Figure 42. LIN Transmit Buffer 0 Register (LINTD0) R/W-0 R/W-0 R/W-0 R/W-0 LEGEND: R/W = Read/Write; R = Read only; -n = value after reset Table 29. LIN Transmit Buffer 0 Register (LINTD0) Field Descriptions Field Value Description... -

Page 78: 6.23 I/O Design For Test Control (Iodftctrl) Register

Preliminary SCI/BLIN Control Registers www.ti.com 6.22 Maximum Baud Rate Selection Register (MBRS) The Maximum Baud Rate Selection Register (MBRS) is shown in Figure 44 and described in Table Figure 44. Maximum Baud Rate Selection Register (MBRS) Reserved Reserved R/WL-0 LEGEND: R/W = Read/Write; R = Read only; -n = value after reset Table 31. -

Page 79: I/O Design For Test Control (Iodftctrl) Register Field Descriptions

Preliminary SCI/BLIN Control Registers www.ti.com Figure 45. I/O Design For Test Control (IODFTCTRL) Register Bit Error Enable Physical Bus Checksum Inconsistent Reserved Frame Error Parity Error Break Detect Error Enable Error Enable Synch Field Enable Enable Error Enable Error Enable R/W-0 R/W-0 R/W-0... - Page 80 Preliminary SCI/BLIN Control Registers www.ti.com Table 32. I/O Design For Test Control (IODFTCTRL) Register Field Descriptions (continued) Field Value Description 20-19 PIN SAMPLE These bits define the sample number at which the TX Pin value that is being transmitted will be MASK inverted to verify the receive pin samples correctly with the majority detection circuitry.

-

Page 81: Blin Sci Vs. Standard Sci

Preliminary BLIN SCI vs. Standard SCI www.ti.com BLIN SCI vs. Standard SCI Table 33 compares the BLIN/SCI with the standalone-SCI ("standard" SCI) available in all C2000 devices. Table 33. SCI vs. LIN-SCI Programming Standard SCI BLIN SCI CCS Register Structure SciaRegs.REGISTER LinaRegs.REGISTER Example Configurations... - Page 82 Preliminary BLIN SCI vs. Standard SCI www.ti.com Table 33. SCI vs. LIN-SCI Programming (continued) Standard SCI BLIN SCI FIFO Buffer Depth: Depth: 8 bits x 16 8 bits x 8 Fill: Fill: for(iter = 0; iter < depth; iter++) LinaRegs.LINTD0.bit.TD0 = data[0]; LinaRegs.LINTD0.bit.TD1 = data[1];...

- Page 83 Preliminary BLIN SCI vs. Standard SCI www.ti.com Table 33. SCI vs. LIN-SCI Programming (continued) Standard SCI BLIN SCI LinaRegs.SCIINTVECT1.all; if(LinL1IntVect == TXVect) //do TX stuff if(LinL1IntVect == RXVect) //do RX stuff //Acknowledge PIE PieCtrlRegs.PIEACK.all = PIEACK_GROUP9; SPRUGE2A – May 2009 – Revised June 2009 Local Interconnect Network (LIN) Module Submit Documentation Feedback...

-

Page 84: Appendix A Revision History

Preliminary Appendix A www.ti.com Appendix A Revision History The technical changes to this document are detailed in . Table A-1. Revision A Changes Location Additions/Changes/Deletions Global Changed SW_nRESET to SWnRST Section 1 Inserted definition for SCI, serial communications interface Section 1.1 Changed communications area network (CAN) to controller area network (CAN). - Page 85 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.