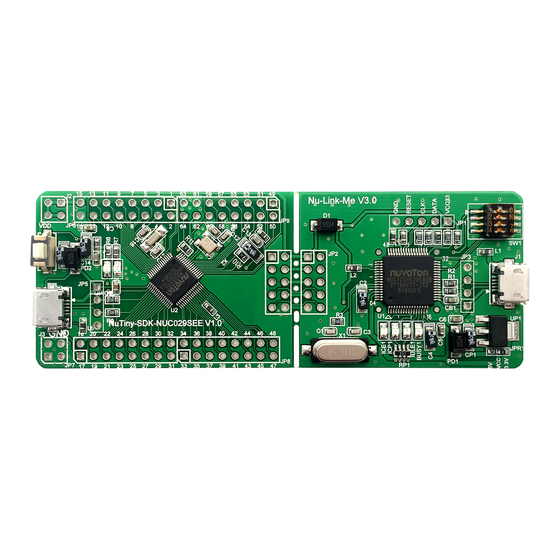

Nuvoton NuMicro NUC029 Series Manuals

Manuals and User Guides for Nuvoton NuMicro NUC029 Series. We have 1 Nuvoton NuMicro NUC029 Series manual available for free PDF download: Technical Reference Manual

Nuvoton NuMicro NUC029 Series Technical Reference Manual (497 pages)

32-bit Arm Cortex-M0 Microcontroller

Brand: Nuvoton

|

Category: Microcontrollers

|

Size: 5 MB

Table of Contents

Advertisement