Mips Technologies R4000 Design Manuals

Manuals and User Guides for Mips Technologies R4000 Design. We have 1 Mips Technologies R4000 Design manual available for free PDF download: User Manual

Mips Technologies R4000 User Manual (754 pages)

Microprocessor

Brand: Mips Technologies

|

Category: Computer Hardware

|

Size: 2 MB

Table of Contents

-

Introduction

32 -

-

-

-

Branch Delay78

-

Load Delay78

-

-

-

-

CP0 Registers114

-

TLB Misses127

-

TLB Instructions127

-

-

Mode Bits137

-

-

Exception Types149

-

Reset Exception154

-

TLB Exceptions158

-

Trap Exception166

-

Watch Exception172

-

-

-

-

Overview182

-

FPU Features183

-

-

-

-

-

Exception Types218

-

Flags220

-

FPU Exceptions222

-

-

-

-

Power-On Reset246

-

Cold Reset247

-

Warm Reset247

-

-

Warm Reset251

-

Clock Interface

257-

-

Masterclock259

-

Masterout259

-

Syncin/Syncout259

-

Pclock259

-

Sclock260

-

Tclock260

-

Rclock260

-

-

-

-

Cache States285

-

-

-

Noncoherent295

-

Sharable295

-

Uncached295

-

Update295

-

Exclusive296

-

-

Strong Ordering297

-

-

-

Invalidate300

-

Update300

-

Snoop300

-

Intervention301

-

-

-

-

System Model306

-

Load308

-

Store308

-

Processor Write309

-

-

-

Counter318

-

LL and SC319

-

System Interface323

-

System Interface

324-

Terminology324

-

-

Interface Buses325

-

Issue Cycles326

-

-

-

-

Load Miss348

-

Store Miss351

-

Store Hit356

-

CACHE Operations357

-

-

-

-

-

-

Scdchk Bus411

-

SCTAG Bus411

-

JTAG Interface

419 -

-

-

ECC Check Bits444

-

Delay Times720

-

Cpu Board721

-

-

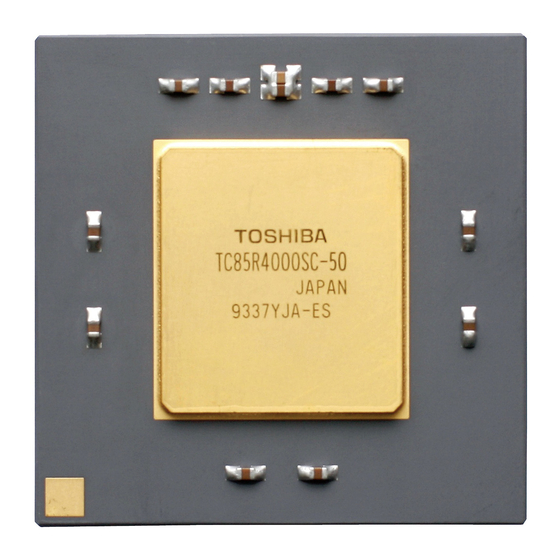

R4000 Pinouts

732

Advertisement