Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Epson SR3225SAA

- Page 1 ETM54E-07 Application Manua RF Transmitter Module SR3225SAA...

- Page 2 Seiko Epson Corporation (“Seiko Epson”). The information contained in this material is for reference only. Seiko Epson assumes no liability whatsoever associated with the use or misuse of such information. This material does not grant license to any patent or intellectual property rights.

-

Page 3: Table Of Contents

SR3225SAA Table of Contents 1. Overview ........................1 2. Part Number ........................ 2 3. Block Diagram ......................3 4. Pin Assignments ......................4 4.1. Pin Assignments ..........................4 Pin Descriptions ..........................4 4.2. 5. Electrical Characteristics ....................5 5.1. Absolute Maximum Rating ......................5 DC Characteristics ........................ - Page 4 SR3225SAA PLL Fractional Setting: Frequency Channel 3 ................36 7.5. PLL Fractional Setting: Frequency Channel 4 ................36 7.6. PLL Integer Setting: Frequency Channel 3 and 4 ................ 36 7.7. FSK Deviation Setting, Output Divider Setting, and CKOUT Slew Rate Control Setting .... 37 7.8.

-

Page 5: Overview

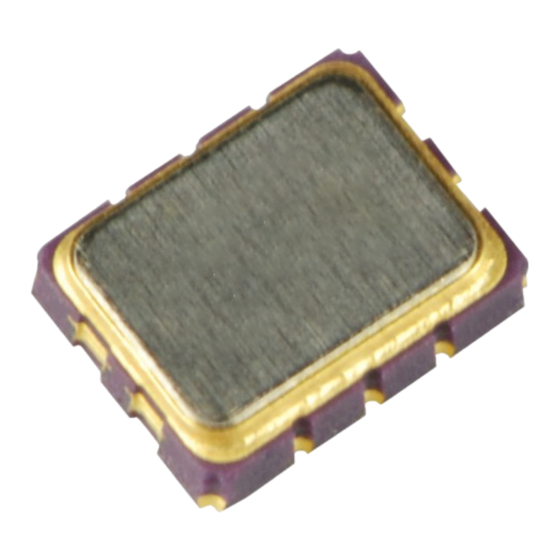

PLL, and a Power Amp in a 3.2 mm x 2.5 mm ceramic package. The crystal resonator is optimally matched with the IC at the factory. The SR3225SAA is ideal for small wireless transmitters because wireless transmission can be achieved simply by combining it with an external controller. -

Page 6: Part Number

SR3225SAA 2. Part Number SR3225SAA A Model name Crystal resonator frequency A: 32 MHz Page - 2 ETM54E-07... -

Page 7: Block Diagram

SR3225SAA Block Diagram Figure 3.1 Block Diagram Page - 3 ETM54E-07... -

Page 8: Pin Assignments

SR3225SAA 4. Pin Assignments 4.1. Pin Assignments (Top View) 4.2. Pin Descriptions Table 4.1 Pin Descriptions Pin Name Type Function TEST1 Input/Output Pull-down Test pin/ TxDATA input / SPI interface pin Leave floating and make no external connections to this pin if the function of this pin is unused. -

Page 9: Electrical Characteristics

SR3225SAA 5. Electrical Characteristics 5.1. Absolute Maximum Rating Standard Item Symbol Condition Unit Min. Typ. Max. Supply voltage VSS = 0 V -0.3 VSS – 0.3 Input voltage VSS = 0 V VDD + 0.3 Storage temperature Tstg Store as bare product +125 °C... -

Page 10: Dc Characteristics

SR3225SAA 5.2. DC Characteristics Table 5.1 Power Supply, Operating Temperature VSS = 0 V, Ta = -40°C to +85°C Standard Item Symbol Condition Unit Min. Typ. Max. Supply voltage Supply current Powerdown VDD = 3.0 V, Ta = 25°C DDPD Mode VDD = 3.6 V, Ta = 85°C... - Page 11 SR3225SAA Table 5.2 Logic I/O VDD = 1.8 V to 6 V, VSS = 0 V, Ta = -40 °C to 5 °C Standard Item Symbol Condition Unit Min. Typ. Max. High level input voltage EN, SCK, SDIO, TEST1 VDD x 0.8 VDD + 0.3...

-

Page 12: Ac Characteristics

SR3225SAA 5.3. AC Characteristics Table 5.4 Transmitter Characteristics VDD = 1.8 V to 3.6 V, VSS = 0 V, Ta = -40 °C to +85 °C Standard Item Symbol Condition Unit Min. Typ. Max. Carrier frequency bands Modulation types ASK / OOK / FSK... - Page 13 SR3225SAA Table 5.5 PA Characteristics VSS = 0 V Standard Item Symbol Condition Unit Min. Typ. Max. 1, 2, 3 Nominal output power* Ta = 25°C, VDD = 3.0 V, F = 315 MHz, HPWR = 1, PADUTY = 10b AM* = 0x3F 10.0...

- Page 14 SR3225SAA Inductor: TDK MLG1005S series Capacitor: TDK C1005C0G1 series 0.1 μF 315 MHz 560 pF 7 pF 82 pF 10 pF 100 nH 39 nH 0.1 μF 433 MHz 560 pF 7 pF 22 pF 10 pF 82 nH 27 nH 0.1 μF...

- Page 15 SR3225SAA Table 5.6 SPI Interface Characteristics VDD = 1.8 V to 3.6 V, VSS = 0 V, Ta = -40°C to +85°C Standard Item Symbol Condition Unit Min. Typ. Max. t SCK SCK clock cycle SCK H pulse width t WH...

-

Page 16: Function Description

PLL, and a Power Amp in a 3.2 mm x 2.5 mm ceramic package. The crystal resonator is optimally matched with the IC at the factory. The SR3225SAA is ideal for small wireless transmitters because wireless transmission can be achieved simply by combining it with an external controller. -

Page 17: Spi Interface Mode Change

The SPI interface mode is changed by setting IFSEL[1:0], which is assigned to SFR address 0x15. (See Table 6.1 and Figure 6.1.) When connecting SR3225SAA with MCU in 4-wire SPI mode, you can write data without setting IFSEL[1:0]. To read data, set IFSEL[1:0]. -

Page 18: Sfr Access Command

SR3225SAA 6.2.2. SFR access command You can access SFR using 3-wire and 4-wire SPI mode. Figure 6.2 depicts the timing for writing access in 3-wire and 4-wire SPI modes, Figure 6.3 shows the timing for read access in 3-wire SPI mode, and Figure 6.4 shows the timing for read access in 4-wire SPI mode. - Page 19 Transmit command SR3225SAA supports burst write and read. Figure 6.5 depicts the timing for burst write access in 3-wire and 4-wire SPI modes, Figure 6.6 shows the timing for burst read access in 3-wire SPI mode, and Figure 6.7 shows the timing for burst read access in 4-wire SPI mode.

-

Page 20: Spi Checksum

SR3225SAA 6.2.3. SPI checksum SPI checksum is available (Figure 6.8). The XOR arithmetic calculation of command + address 8 bits and data 8 bits is operated during SFR write access. The checksum result is stored in 0x16 SFR address. The checksum is reset by transiting to Powerdown mode or writing any data to checksum register (address 0x16). -

Page 21: Transmit Command

SR3225SAA 6.2.4. Transmit command The Transmit command is activated when the SPI command bit is set to 11b. The six bits (A to F) that follow the command bit specify the transmit function structure. (See Table 6.4) The Transmit command is available only in PLL-Standby mode described in section 6.3.1. - Page 22 SR3225SAA Figure 6.9 Asynchronous Transmission Timing Synchronous transmission mode Synchronous transmission timing is shown in Figure 6.10. In synchronous transmission mode, SDIO signals are latched by the bitrate signals, and the latched signals are transmitted. The bitrate signal for latch is formed by dividing the frequency for the internal crystal oscillator, thus the bitrate signal has same accuracy as the internal crystal oscillator.

- Page 23 SR3225SAA Figure 6.11 shows synchronous transmission example in the following settings: Synchronous transmission (bit "A" = 1), PA is OFF (bit "B" = 0) when EN falls, transmission sign is Manchester code (bit "C" = 1), CKSRC [2:0] = 010b, ASC [2:0] = 1. See section 6.8 for CKOUT settings and details.

- Page 24 SR3225SAA Transmission data input process Transmission signal input method is selected by IFSEL[1:0] setting. Both pins are available in both the synchronous transmission mode and the asynchronous transmission mode. See Figure 6.12 for transmission signal input timing details through the SDIO pin and Figure 6.13 for transmission signal input timing details through the TEST1 pin.

-

Page 25: Operating Modes

6.3. Operating Modes 6.3.1. State transition SR3225SAA has 4 modes, and you can control state transition using pins or SPI command. The state diagram is shown in Figure 6.14. See the section below for details of each mode. Powerdown mode In Powerdown mode, minimum required circuits are powered on, and the current consumption is lowest. -

Page 26: Control Signal Timing

SR3225SAA Figure 6.14 State Diagram 6.3.2. Control signal timing An example of control signal timing is shown in Figure 6.15.Figure 6.15 shows a wireless transmission sequence that starts from and goes back to Powerdown mode. First, the mode is changed from Powerdown mode to ATOSC-Active mode when the EN pin rises. In this example, initial SFR data writing is being performed during the crystal oscillator start-up time. -

Page 27: Output Frequency Setting

SR3225SAA Powerdown ATOSC-Active Transmitter Powerdown -Standby -Active -Standby Crys tal oscillator PLL s tabilization time XTAL Cl ocks s ta rt-up time >t ≒8.2 ms >t = 100 μs = 500 μs FSTE XTAL SFR_Init (Write PLL_EN=1) Transmit command Tx DATA... - Page 28 SR3225SAA Table 6.5 f and FnODIV [MHz] ODIV FnODIV (SFR address 0x0A) 300 to 465 600 to 930 VCO frequency (F ) is determined by the reference frequency (F ), which is supplied from crystal oscillator, and the division ratio of feedback divider (N). The division ratio of feedback divider is determined by the integral...

-

Page 29: Fsk Modulator

SR3225SAA Table 6.6 N and SFR Parameters FnINT[3:0] (SFR address 0x04, 0x09) 6.5. FSK Modulator 6.5.1. FSK deviation setting You can set FSK deviation in SFR address 0x0B. FSK modulation (F ) is calculated by formula (7). F is the reference frequency of crystal oscillator. -

Page 30: Soft-Fsk

SR3225SAA 6.5.2. Soft-FSK Soft-FSK function is implemented to reduce FSK modulation bandwidth. In Soft-FSK, modulation is applied in ramp shape shown in Figure 6.16. FMRC Figure 6.16 Soft-FSK Modulation Wave shown in Figure 6.16 is calculated by formula (9). The FMRC in formula (9) determines the inclination of FMRC ramp shape and is assigned to SFR address 0x10. - Page 31 SR3225SAA HPWRn HPWRn switches output power range (n = 0/1, HPWR0 or HPWR1). See Table 6.8 for details. Table 6.8 HPWRn Settings HPWRn Output power range -15 dBm to 0 dBm -5 dBm to 11 dBm AMHn[5:0] AMHn[5:0] is output power setting in H level data transmission for ASK (n = 0/1, AMH0[5:0] or AMH1[5:0]). It is also output power setting for FSK.

-

Page 32: Soft-Ask

SR3225SAA 6.6.2. Soft-ASK Soft-ASK function is implemented to reduce the ASK modulation bandwidth. In Soft-ASK, modulation is applied in ramp shape shown in Figure 6.17. AMRC Figure 6.17 Soft-ASK Modulation Wave shown in Figure 6.17 is calculated by formula (10). The AMRC of formula (10) determines the inclination AMRC of ramp shape and is assigned to SFR address 0x0F. -

Page 33: Fail-Safe Function

SR3225SAA 6.7. Fail-safe Function SR3225SAA has three kinds of fail-safe functions. If a fail is detected, the PA is turned off according to fail-safe settings. This function detects PLL loss of lock, VCO auto-calibration errors, and under voltage. Error results are stored in SFR address 0x14 and can be read out. - Page 34 SR3225SAA Figure 6.18 Reset of Under Voltage Detection Results by SFR Write Clear Figure 6.19 Reset of Under Voltage Detection Results by Transition to Powerdown Mode Page - 30 ETM54E-07...

-

Page 35: Clock Output (Ckout) Function

SR3225SAA 6.8. Clock Output (CKOUT) Function 6.8.1. Frequency divider The frequency divider structure for CKOUT/bitrate signal is shown in Figure 6.20. The frequency divider for CKOUT/bitrate signal consists of three programmable dividers and two fixed dividers. You can select signals output from the CKOUT using CKSRC[2:0] in SFR address 0x12h. The detail of CKSRC[2:0] is shown in Table 6.11. -

Page 36: Frequency Divider Setting

SR3225SAA 6.8.2. Frequency divider setting The settings for "Prescaler" shown in Figure 6.20 is made in PSC[2:0] in SFR address 0x12. See Table 6.12 for details. Table 6.12 PSC[2:0] Setting PSC[2:0] Division ratio 1/16 1/32 1/64 1/128 The settings for "Comparator" shown in Figure 6.20 is made in BRS[7:0] in SFR address 0x11. See Table 6.13. -

Page 37: Output Cmos Driver

6.9.2. Oscillation status monitor SR3225SAA has a circuit that detects crystal oscillator amplitude. Detection results are stored in the OSCDET in SFR address 0x14. This function enables stable output clock signals by controlling the start of output from the CKOUT pin based on the detection results. -

Page 38: Sfr (Special Function Register)

SR3225SAA 7. SFR (Special Function Register) 7.1. SFR List Name Description Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Reset Value F1FRAC1 Freq1 Fractional setting 1 0x00 F1FRAC[15:8] xxxx xxxx b F1FRAC0 Freq1 Fractional setting 0 0x01 F1FRAC [7:0]... -

Page 39: Pll Fractional Setting: Frequency Channel 1

SR3225SAA 7.2. PLL Fractional Setting: Frequency Channel 1 Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 F1FRAC1 F1FRAC[15:8] 0x00 F1FRAC[7:0] 0x01 F1FRAC0 Type Default Name Function F1FRAC[15:8] Fractional portion of the feedback divider (N ) of frequency channel 1... -

Page 40: Pll Fractional Setting: Frequency Channel 3

SR3225SAA 7.5. PLL Fractional Setting: Frequency Channel 3 Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 F3FRAC1 F3FRAC[15:8] 0x05 F3FRAC[7:0] 0x06 F3FRAC0 Type Default Name Function F3FRAC[15:8] Fractional portion of the feedback divider (N ) of frequency channel 3... -

Page 41: Fsk Deviation Setting, Output Divider Setting, And Ckout Slew Rate Control Setting

SR3225SAA 7.8. FSK Deviation Setting, Output Divider Setting, and CKOUT Slew Rate Control Setting Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 ODIV FDEV4X FDEV2X SR[1:0] F1ODIV F2ODIV F3ODIV F4ODIV 0x0A Type Default Name Function FDEV4X FSK deviation setting ��... -

Page 42: Ask Modulation Control 0

SR3225SAA 7.10. ASK Modulation Control 0 Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 ASKMC0 ASK0 HPWR0 AMH0[5:0] 0x0C Type Default Name Function ASK0 Modulation type HPWR0 PA output power range -15 dBm to 0 dBm -4 dBm to 11 dBm... -

Page 43: Ask Modulation Control 2

SR3225SAA 7.12. ASK Modulation Control 2 Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 ASKMC2 PADUTY[1:0] AML[5:0] 0x0E Type Default Name Function PADUTY[1:0] Output signal duty cycle setting Nominal duty cycle PADUTY[1:0] = 300 MHz to 465 MHz... -

Page 44: Soft-Fsk Modulation Setting

SR3225SAA 7.14. Soft-FSK Modulation Setting Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 FSKRAMP FMRC[7:0] 0x10 Type Default Name Function FMRC[7:0] Soft-FSK Modulation setting You can set FMRC calculated as follows. See section 6.5.2 for details. ��... -

Page 45: Ckout / Bitrate Signal Divider Setting 2

SR3225SAA 7.16. CKOUT / Bitrate Signal Divider Setting 2 Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 BRS2 CKSRC[2:0] PSC[2:0] ASC[1:0] 0x12 Type Default Name Function CKSRC[2:0] Clock source setting 000b Fref / 16 001b Prescaler clock PAON: 0 "Low"... -

Page 46: Under Voltage Detection / Antenna Tuning Setting

SR3225SAA 7.17. Under Voltage Detection / Antenna Tuning Setting Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 ATUNE VDET[1:0] ATT[4:0] 0x13 Type Default Name Function VDET[1:0] Under voltage detection/release setting Detection Release threshold threshold 1.8 V 2.0 V 2.0 V... -

Page 47: Error Detection Status

SR3225SAA 7.18. Error Detection Status Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 TXSTAT TXCOUNT[3:0] OSCDET VDETER VCOCER PLLDER 0x14 Type Default Name Function TXCOUNT[3:0] Function for counting the number of transitions to Transmitter-Active mode The value is reset to zero when the counter overflows. -

Page 48: Transmitter Control

3-wire SPI mode TEST1 Invalid PLLEN Transition to PLL-Standby mode If PLLEN is set to 1 in ATOSC-Active mode, SR3225SAA transits to PLL-Standby mode. If PLLEN is set to 0 in PLL-Standby mode, SR3225SAA transits to ATOSC-Active mode. Page - 44 ETM54E-07... -

Page 49: Spi Checksum

SR3225SAA 7.20. SPI Checksum Register Address name Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SPICKSUM SPICKSUM[7:0] 0x16 Type Default Name Function SPICKSUM SPI checksum calculation result The XOR result of SPI transmission address and data is stored. Page - 45... -

Page 50: Dimensions

SR3225SAA 8. Dimensions Unit: mm Page - 46 ETM54E-07... -

Page 51: Marking

SR3225SAA 9. Marking This figure shows letters and their rough positions, but does not show their fonts and sizes. Page - 47 ETM54E-07... -

Page 52: Soldering Pattern

SR3225SAA 10. Soldering Pattern Unit: mm Page - 48 ETM54E-07... -

Page 53: Application Note

Especially the quality of telecommunication equipment could be affected by this phenomenon. Although Epson products are designed to minimize the effect of mechanical vibration, it is recommended to check them in advance. - Page 54 SR3225SAA Output power was evaluated using Epson's evaluation board and test circuit shown in Figure 5.1. Optimum circuit parameters may differ by board's wire trace pattern. Please check the optimum parameters. 10. If signals are continuously outputted with maximum output power (AM* = 0x3F, P = approximately 11 dBm) for a long time, output power may be lower.

-

Page 55: Application Manual Revision History

SR3225SAA 12. Application Manual Revision History Model name: SR3225SAA Specification control No. Revision History ETM54E Revision Date of Change Description of changes Revision (p. XX) Reason Feb. 4, 2016 Newly established Apr. 22, 2016 correction of errors See Table 5.4 See Table 5.5... - Page 56 SR3225SAA Model name: SR3225SAA Specification control No. Revision History ETM54E Revision Date of Change Description of changes Revision (p. XX) Reason State diagram State diagram Feb. 16, 2017 correction of errors Page - 52 ETM54E-07...

- Page 57 Unit 715-723 7/F Trade Square, 681 Cheung Sha Wan Road, Kowloon, Hong Kong Phone: (86) 755-2699-3828 (Shenzhen Branch) Fax: (86) 755-2699-3838 (Shenzhen Branch) http://www.epson.com.hk EPSON TAIWAN TECHNOLOGY & TRADING LTD. 14F, No.7, Song Ren Road, Taipei 110 Phone: (886) 2-8786-6688 Fax: (886) 2-8786-6660 http://www.epson.com.tw/ElectronicComponent...

Need help?

Do you have a question about the SR3225SAA and is the answer not in the manual?

Questions and answers