Texas Instruments TPS6594-Q1 Series User Manual

Powering dra829v and tda4vm with the pmics

Hide thumbs

Also See for TPS6594-Q1 Series:

- User manual (28 pages) ,

- User manual (48 pages) ,

- User manual (51 pages)

Table of Contents

Advertisement

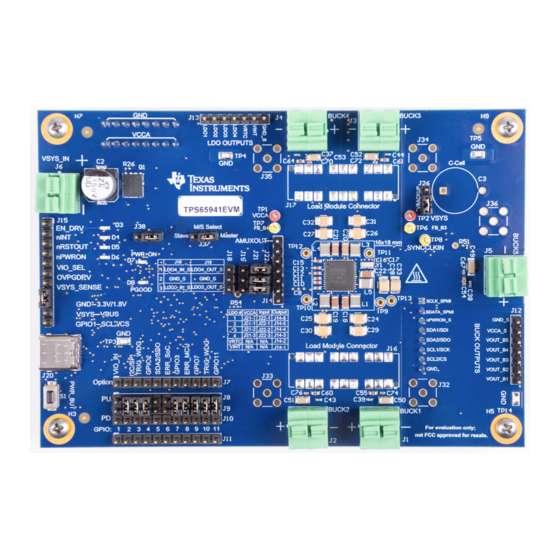

User's Guide for Powering DRA829V and TDA4VM with the

This User's Guide can be used as a guide for integrating the TPS6594-Q1 power management integrated

circuit (PMIC) into a system powering the DRA829V or TDA4VM device. This document provides the

default non-volatile memory (NVM) settings, state transitions, and power sequencing for the system

solution.

...................................................................................................................

1

2

3

4

5

6

7

1

2

3

4

5

6

7

8

9

10

11

1

2

3

4

5

6

7

8

9

10

11

12

13

SLVUBR0 - December 2019

Submit Documentation Feedback

..............................................................................................................

.......................................................................................................

...................................................................................

.........................................................................................................

......................................................................................................

List of Figures

..........................................................................................

................................................................................................

........................................................................................

.......................................................................................

.......................................................................................

....................................................................................................

........................................................................................................

..................................................................................

..................................................................................

.............................................................................................

......................................................................................

.......................................................................................................

.........................................................................................................

.......................................................................................................

........................................................................................................

.........................................................................................................

....................................................................................................

............................................................................................

.............................................................................................

User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1

Copyright © 2019, Texas Instruments Incorporated

TPS6594-Q1 PMICs

Contents

.............................................................

........................................................

........................................................

......................................................................

..............................................................

List of Tables

......................................................

User's Guide

SLVUBR0 - December 2019

3

3

3

7

9

25

42

4

6

25

28

30

32

34

36

37

39

41

3

5

7

9

10

10

12

13

14

16

17

21

22

1

PMICs

Advertisement

Table of Contents

Summary of Contents for Texas Instruments TPS6594-Q1 Series

-

Page 1: Table Of Contents

......................FSM NVM Settings ....................Interrupt NVM Settings .................... POWERGOOD NVM Settings ..................... Miscellaneous NVM Settings SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 2 State Transition Triggers ..................... Additional Documents Trademarks All trademarks are the property of their respective owners. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 3: Introduction

LDO1 voltage without the need for the MCU of the processor to establish I2C communication with the PMICs during boot from SD card operations. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 4: Power Connections With Tps659413-Q1 And Tps659411-Q1

1.8V TPS22965-Q1 3.3V 3.3V (load switch, 4A max) Figure 1. Power Connections with TPS659413-Q1 and TPS659411-Q1 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 5: Power Connections By System Feature

GPIO pins will remain operational. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 6: Digital Connections With Tps659413-Q1 And Tps659411-Q1

VIO t 1.8V or 3.3V GPIO_11 (GPO) ENABLE MAIN I/O TPS22965-Q1 Figure 2. Digital Connections with TPS659413-Q1 and TPS659411-Q1 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 7: Supporting Functional Safety Systems

Independent Power Control of MCU and Main Rails • Independent Monitoring and Reset for MCU and Main Rails • Input Supply Monitoring SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 8 For ASIL-C or ASIL-D systems, there are additional features to the ones described in Section 4.1 that can be utilized. These features include: User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 9: Static Nvm Settings

These settings are used to distinguish which device is detected in a system. These settings cannot be changed after device startup. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 10: Device Identification Nvm Settings

5.5 A Note that this NVM default value can change when the device transitions to ACTIVE mode. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 11 BUCK5_VOUT_1 BUCK5_VSET1 10110010b 1.8 V 01000001b 0.85 V BUCK5_VOUT_2 BUCK5_VSET2 00000000b 0.3 V 00000000b 0.3 V SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 12: Ldo Nvm Settings

Note that this NVM default value can change when the device transitions to ACTIVE mode. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 13: Vcca Nvm Settings

GPIOx_CONF and GPIO_OUT_x registers are applicable. To understand which NVM fields apply to each GPIOx_SEL option, see the "Digital Signal Descriptions" section in the TPS6594x-Q1 datasheet. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 14: Gpio Nvm Settings

GPIO5_PU_PD_EN Pull-up/pull-down Pull-up/pull-down resistor disabled resistor disabled GPIO5_DEGLITCH_EN No deglitch, only No deglitch, only synchronization. synchronization. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 15 GPIO10_PU_PD_EN Pull-up/pull-down Pull-up/pull-down resistor enabled resistor enabled GPIO10_DEGLITCH_EN No deglitch, only No deglitch, only synchronization. synchronization. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 16: Fsm Nvm Settings

SOC rail group BUCK3_GRP_SEL MCU rail group SOC rail group BUCK4_GRP_SEL MCU rail group SOC rail group User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 17: Interrupt Nvm Settings

GPIO8_FSM_MASK Masked Masked GPIO8_FSM_MASK_POL Masking sets signal Masking sets signal value to '0' value to '0' SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 18 LDO1_ILIM_MASK Interrupt not Interrupt not generated. generated. LDO2_ILIM_MASK Interrupt not Interrupt not generated. generated. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

- Page 19 Interrupt not generated. generated. GPIO7_RISE_MASK Interrupt generated Interrupt not generated. GPIO8_RISE_MASK Interrupt generated Interrupt not generated. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

- Page 20 Interrupt generated NRSTOUT_READBACK_ Interrupt generated Interrupt not MASK generated. NRSTOUT_SOC_ Interrupt generated Interrupt not READBACK_MASK generated. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 21: Powergood Nvm Settings

PGOOD_WINDOW Both undervoltage Both undervoltage and and overvoltage are overvoltage are monitored monitored SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 22: Miscellaneous Nvm Settings

1111b 16ms 1111b 16ms LDO_RV_TIMEOUT_ LDO3_RV_TIMEOUT 1111b 16ms 1111b 16ms REG_2 LDO4_RV_TIMEOUT 1111b 16ms 1111b 16ms User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 23 These settings detail whether the device is a operating as a master or slave in the system. These settings cannot be changed after device startup. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

- Page 24 ENABLE_DRV bit to 1 ENABLE_DRV bit to 1 if all other interrupt status bits are cleared User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 25: Pre-Configurable Finite State Machine (Pfsm) Settings

STANDBY state. EN_DRV is forced low in this state. The processor is in the Off State, no voltage domains are energized. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 26 NSLEEP1 and NSLEEP2 can be accessed through GPIO pin or through a register bit. If either the register bit or the GPIO pin is pulled high, the NSLEEPx value will read as a "high" logic level. User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs SLVUBR0 – December 2019 Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

- Page 27 PMICs in case of over voltage on VCCA or thermal shutdown. The MCU error will keep the BUCKs switching until they are disabled. The sequence for these triggers is shown in Figure SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 28: To_Safe_Severe Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 4. TO_SAFE_SEVERE Sequence User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 29 SAFE state. The power sequence for both of these events is shown in Figure SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 30: To_Safe_Moderate And To_Standby Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 5. TO_SAFE_MODERATE and TO_STANDBY Sequence User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 31 ACTIVE state. Note that the GPIOs do not reset during the warm reset event. The sequence is shown in Figure SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 32: Warm_Reset Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 6. WARM_RESET Sequence User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 33 MCU state. Note that the GPIOs do not reset during the MCU warm reset event. The sequence is shown in Figure SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 34: Mcu_Warm_Reset Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 7. MCU_WARM_RESET Sequence User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 35 NVM revision (NVM_REV = 0x08) orderable part number. SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 36: To_Mcu Sequence With I2C_7=0

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 8. TO_MCU Sequence with I2C_7=0 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 37: To_Mcu Sequence With I2C_7=1

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 9. TO_MCU Sequence with I2C_7=1 SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 38 When a trigger causes the TO_ACTIVE sequence to execute, all rails of the PMICs will power up in the processor's recommended power up sequence as shown in Figure User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 39: To_Active Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 10. TO_ACTIVE Sequence SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 40 Any event that triggers this sequence will disable all power rails and GPIOs that are not supplying the DDR to enter suspend-to-RAM state (S2R). The sequence is shown in Figure User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated...

-

Page 41: To_S2R Sequence

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com Figure 11. TO_S2R Sequence SLVUBR0 – December 2019 User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... -

Page 42: Additional Resources

Request through Safety Manual DRA829V, TDA4VM Processors mySecure Request through TPS6594x-Q1 Schematic Checklist Application Note TPS6594x-Q1 mySecure User's Guide for Powering DRA829V and TDA4VM with the TPS6594-Q1 SLVUBR0 – December 2019 PMICs Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated... - Page 43 TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated...

Need help?

Do you have a question about the TPS6594-Q1 Series and is the answer not in the manual?

Questions and answers