Table of Contents

Advertisement

Advertisement

Table of Contents

Summary of Contents for AMLOGIC S905D3

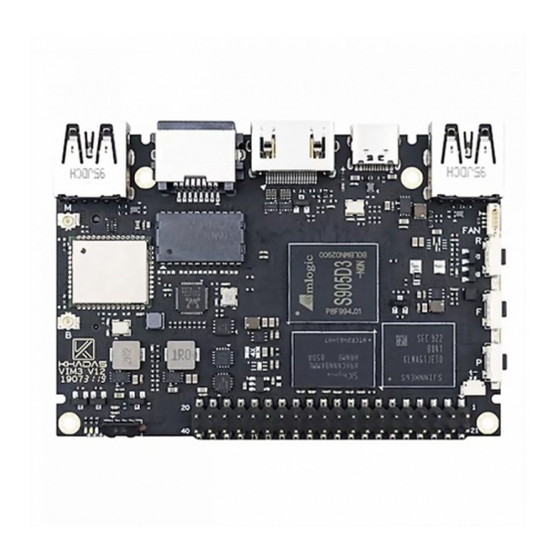

- Page 1 S905D3 Quick Reference Manual Revision: 0.6 Release Date: 2019–07–25...

- Page 2 This product is not intended for use in medical, life saving, or life sustaining applications. Circuit diagrams and other information relating to products of Amlogic are included as a means of illus- trating typical applications. Consequently, complete information sufficient for production design is not necessarily given.

-

Page 3: Revision History

Compare with last version the following topic is new added: ● ● Version 0.3(2019-03-10) This is the third release. Compare with last version the following part has been modified: Section Change Description , Correct typo Add note Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 4 This is the first release. Compare with last version the following part has been modified: Section Change Description 5.5.1 Correct typo Preliminary Version(2019-01-30) This is the preliminary release. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 5: Table Of Contents

5.8 Power On Config .........................62 5.9 Power On Reset ........................63 5.10 Recommended Power on sequence...................64 5.11 Power Consumption......................65 5.12 Storage and Baking Conditions ..................66 6 Mechanical Dimensions ......................67 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 6: About This Document

S905D3 Quick Reference Manual 1 About This Document 1 About This Document This document is applicable to S905D3 SoC series, please contact your Amlogic sales representative for more detail. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 7: General Description

(DMIC) inputs. It also has build-in Voice Activity Detection(VAD)module for ultra-low power operations during system standby. S905D3 also integrates a set of functional blocks for digital TV broadcasting streams. The built-in two demux can process the TV streams from the serial and paralleltransport stream input interface, which can connect to external tuner/demodulator. -

Page 8: Features Summary

4-wide warps, dual texture pipe, 2x 4-wide execution engines (EE) ● ● Concurrent multi-core processing ● ● OpenGL ES 3.2, Vulkan 1.1 and OpenCL 2.0 support ● ● Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 9 Built-in hardware True Random Number Generator (TRNG), CRC and SHA-1/SHA-2/HMAC ● ● SHA engine Video/Picture CODEC Amlogic Video Engine (AVE) with dedicated hardware decoders and encoders ● ● Support multi-video decoder up to 4x1080P@60fps ● ● Supports multiple “secured” video decoding sessions and simultaneous decoding and encoding ●...

- Page 10 S905D3 Quick Reference Manual 3 Features Summary 8th Generation Advanced Amlogic TruLife Image Engine optional Supports Dolby Vision , HDR10+, HDR10, HLG and Technicolor HDR processing ● ● Motion compensated noise reduction and 3D digital noise reduction for random noise ●...

- Page 11 Pre-region/ID memory security control and electric fence ● ● Hardware based Trusted Video Path (TVP) , video watermarking and secured contents (needs ● ● SecureOS software) Secured IO and secured clock ● ● Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 12 S905D3 Quick Reference Manual 3 Features Summary Package FCBGA, 16.1mmx14.3mm, 0.6mm ball pitch, RoHS compliant ● ● Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 13: Pinout Specification

S905D3 Quick Reference Manual 4 Pinout Specification 4 Pinout Specification 4.1 Pin-Out Diagram (top view) Figure 4-1 Pinout Diagram(topview) 4.2 Pin Order Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 14 GPIOA_13 DDR_DQM3 GPIOC_0 DVSS DVSS GPIOA_14 GPIOC_6 GPIOA_4 DVSS PCIE_CLK_p VDDIO_A HCSL_REXT PCIE_RXN GPIOA_11 DVSS PCIE_TXN GPIOA_10 DVSS DVSS GPIOH_0 GPIOC_7 USBHOST_A_DM GPIOH_3 USB_TXRTUNE USBOTG_B_DP HDMITX_CKN HDMI_REXT ENET_TXN Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 15 DDR_RSTn AE11 AC_12 AVSS_HCSL DVSS AE36 CSI_CLKA_N DVSS REFP AE38 CSI_D1N AVDD0V8_USB_PCIE CVBS_RSET AE40 CSI_D1P AVDD0V8_HDMI CVBS_VREF AE42 DSI_CLKN AVDD18_HDMI AC_21 AE44 DSI_CLKP AVSS_CVBS DVSS AF14 DVSS AC_25 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 16 AC_18 DVSS AW14 DVSS DDR_DQM1 AK13 DVSS AW16 VDDCPU DDR_DQ15 AK15 VDDQ AW18 VDDCPU AK17 DVSS AP11 AC_1 AW20 VDDCPU AK19 VDDCPU AP27 VDD_EE AW22 VDDCPU AK21 VDDCPU Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 17 GPIOX_1 DDR_DQ4 DVSS BK34 GPIOX_2 DVSS BC36 GPIOZ_1 DVSS BK38 GPIOX_5 BC38 SARADC_CH2 BOOT_1 BK40 GPIOX_6 BC40 SARADC_CH3 BH11 BOOT_3 BK42 GPIOZ_2 DDR_DQ8 BH13 BOOT_4 BK44 GPIOZ_5 DDR_DQ7 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 18: Pin Description

BM28 DVSS DDR_DQ0 BM32 GPIOX_0 BM11 DVSS BM36 GPIOX_4 4.3 Pin Description The S905D3 application processor pin assignment is described in the following table. Net Name Type Default Description Power Pull UP/ Domain Unused Table 4-1 GPIOZ - Refer to for functional multiplex information. - Page 19 General purpose input/output bank BOOT VDDIO_ signal 8 BOOT BOOT_9 General purpose input/output bank BOOT VDDIO_ signal 9 BOOT BOOT_10 General purpose input/output bank BOOT VDDIO_ signal 10 BOOT Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 20 General purpose input/output bank X signal 8 VDDIO_X GPIOX_9 General purpose input/output bank X signal 9 VDDIO_X GPIOX_10 General purpose input/output bank X signal VDDIO_X GPIOX_11 General purpose input/output bank X signal VDDIO_X Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 21 General purpose input/output bank AO signal VDDIO_AO GPIOAO_4 Down General purpose input/output bank AO signal VDDIO_AO GPIOAO_5 General purpose input/output bank AO signal VDDIO_AO GPIOAO_6 Down General purpose input/output bank AO signal VDDIO_AO Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 22 To 1.8V SARADC CVBS OUT CVBS_ CVBS external compensation capacitor AVDD18_ COMP connection CVBS CVBS_IOUT Video DAC output AVDD18_ CVBS CVBS_ CVBS output strength setting resistor AVDD18_ RSET CVBS Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 23 DDR PHY address/command/control signal VDDQ bit 4 AC_5 DDR PHY address/command/control signal VDDQ bit 5 AC_6 DDR PHY address/command/control signal VDDQ bit 6 AC_7 DDR PHY address/command/control signal VDDQ bit 7 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 24 DDR PHY address/command/control signal VDDQ bit 30 AC_31 DDR PHY address/command/control signal VDDQ bit 31 AC_32 DDR PHY address/command/control signal VDDQ bit 32 AC_33 DDR PHY address/command/control signal VDDQ bit 33 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 25 DRAM data bus bit 15 VDDQ DRAM DDR_DQ16 DRAM data bus bit 16 VDDQ DDR_DQ17 DRAM data bus bit 17 VDDQ DDR_DQ18 DRAM data bus bit 18 VDDQ Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 26 DRAM data strobe 3 complementary VDDQ DQSN3 DRAM reference pin for ZQ calibration,to VDDQ To GND GND by 240ohm 240ohm PVREF DRAM reference voltage VDDQ To GND by ca- pacitor Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 27 MIPI DSI clock positive output AVDD18_ DSI_D0N MIPI DSI data0 negative output or Bidirec- AVDD18_ tional in LP mode DSI_D0P MIPI DSI data0 positive output or Bidirection- AVDD18_ al in LP mode Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 28 Audio LORP Audio DAC line-out right channel positive AVDD18_ signal Audio REFP Audio DAC positive reference voltage AVDD18_ Audio VMID Audio DAC external filter cap connection AVDD18_ Audio Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 29 Ground of Ethernet PLL To GND ENETPLL AVSS_ Ground of DDR AM_ PLL To GND AMPLL AVSS_HPLL Ground of HDMI PLL To GND AVSS_PLL Ground of System PLL To GND Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 30: Pin Multiplexing Tables

As a result, some of the features share the same pin. Most of the multiple usage pins can be used as a GPIO pin as well. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 31 Func2 Func3 Func4 GPIOA_0 MCLK_0 TDMB_D7 GPIOA_1 TDMB_SCLK TDMB_SLV_SCLK GPIOA_2 TDMB_FS TDMB_SLV_FS GPIOA_3 TDMB_D0 TDMB_DIN0 GPIOA_4 TDMB_D1 TDMB_DIN1 PWM_D Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 32 BOOT_15 NAND_CE1 Table 4-4 GPIOC_x Multi-Function Pin Pin Name Func1 Func2 Func3 Func4 Func5 GPIOC_0 SDCARD_D0 JTAG_B_TDO PDM_DIN0 SPI_A_MOSI GPIOC_1 SDCARD_D1 JTAG_B_TDI PDM_DIN1 SPI_A_MISO Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 33 UART_EE_ A_RX GPIOX_14 UART_EE_ A_CTS GPIOX_15 UART_EE_ A_RTS GPIOX_16 PWM_E Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 34 GPIOAO_4 CLK_32K_ PWMAO_C PWMAO_ TDMB_D0 TDMB_ REMOTE_ C_HIZ DIN0 GPIOAO_5 PWMAO_D REMOTE_ INPUT GPIOAO_6 JTAG_A_ PWMAO_C TSIN_A_ TDMB_D2 TDMB_ DIN2 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 35 CAA3 WE_N AC_10 CAA1 CAA1 AC_11 CAA4 CAA0 AC_12 CAA5 CAA5 AC_13 CAA6 CAA4 AC_14 CAA0 AC_15 CAA3 AC_16 CAA9 CLK0_T CLK0_T AC_17 CAA8 CLK0_C CLK0_C AC_18 ODTA Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 36: Signal Description

Signal Name Type Description SDCARD_D0 SD Card data bus bit 0 signal SDCARD_D1 SD Card data bus bit 1 signal SDCARD_D2 SD Card data bus bit 2 signal Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 37 UART Port B data input in EE domain UART_EE _C_TX UART Port C data output in EE domain UART_EE _C_RX UART Port C data input in EE domain Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 38 PWM channel E output signal PWM_F PWM channel F output signal PWMAO_A / PWMAO_A_ PWM A output signal in Always On domain, or extended HiZ function of PWMAO_A Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 39 5 signal EMMC_D6 eMMC/NAND data bus bit 6 signal EMMC_D7 eMMC/NAND data bus bit 7 signal EMMC_CLK eMMC clock signal EMMC_CMD eMMC command signal EMMC_NAND_DQS eMMC/NAND data strobe Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 40 Table 4-23 SPDIF Interface Signal Description Signal Name Type Description SPDIF_IN SPDIF input signal SPDIF_OUT SPDIF output signal Table 4-24 PCIE Interface Signal Description Signal Name Type Description PCIECK_REQN PCIE clock request input Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 41 Data input/output 1 of TDM port B TDMB_D2 Data input/output 2 of TDM port B TDMB_D3 Data input/output 3 of TDM port B TDMB_D4 Data input/output 4 of TDM port B Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 42 JTAG_A_TDO JTAG data output channel A JTAG_A _TDI JTAG data input channel A JTAG_A_TMS JTAG Test mode select input channel A JTAG_A_CLK JTAG Test clock input channel A Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 43 World clock sync input, to sync clock of multi devices GEN_CLK_EE General clock output for EE domain clock, for debug GEN_CLK_AO General clock output for AO domain clock, for debug Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 44: Operating Conditions

1.05 1.89 AVDD33 3.3V AVDD for USB 3.15 3.45 VDDIO LV mode 1.71 1.80 1.89 HV mode 3.45 Operating Junction Temperature — °C Operating Ambient Temperature — °C Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 45: Ripple Voltage Specifications

Ripple specification is only a reference spec, customer should run stress/performance/reliability test (high/low temperature test, damp and hot test, function test, etc...) on their product to confirm the system stability. 5.4 Thermal Resistance Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 46: Dc Electrical Characteristics

3 Low-level input -0.3 IOVREF/2-0.3 voltage Built-in pull up resistor Built-in pull down 130K resistor IoL/IoH(DS=0) GPIO driving capability IoL/IoH(DS=1) GPIO driving capability IoL/IoH(DS=2) GPIO driving capability Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 47: Open Drain Gpio Specifications (For Dio_Od)

2. Maximal GPIO loading is 6mA for application such as driving LED, which does not care about Vol spec 3. The V of OD PAD is irrelevant to VDDIO voltage. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 48: Ddr3/Ddr3L/Ddr4/Lpddr3/Lpddr4 Sdram Specifications

Typ. Max. Unit VdlVW_total Rx Mask voltage-p-p total DC output logic 0.9*VDDQ high DC output logic 0.1*VDDQ Input termination resistance to VDDQ Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 49: Recommended Oscillator Electrical Characteristics

The SoC requires the 24MHz oscillator for generating the main clock source. Symbol Description Min. Typ. Max. Unit Notes Nominal Frequency Δf/f Frequency At 25 ℃ Tolerance At -20~85 ℃ Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 50: Timing Information

● ● >2*0.45V; 5.7 Timing Information 5.7.1 I2C Timing Specification The I2C master interface Fast/Standard mode timing specifications are shown below. Figure 5-1 I2C Interface Timing Diagram, FS mode Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 51: Emmc/Sd Timing Specification

Note Open drain does not support driver strength adjustment. ● ● 5.7.2 EMMC/SD Timing Specification Timing specification for EMMC and SDIO are shown as below. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 52 Slew rate 1.125 V/ns tCKDCD Duty cycle distortion tCKMPW Minimum pulse width tISU input set-up time input hold time tISUddr input set-up time tIHddr input hold time Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 53 Table 5-3 HS200 Timing Specification Symbol Parameter Unit tPERIOD Cycle time data transfer mode tISU output set-up time output hold time Figure 5-4 EMMC HS400 Data Intput Timing Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 54 Cycle time data transfer mode Slew rate 1.125 V/ns tCKDCD Duty cycle distortion tCKMPW Minimum pulse width Input skew tRQH input hold skew Figure 5-5 EMMC HS200 Data Input Timing Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 55 Table 5-6 SDIO (SDR104) Clock Timing Specification Symbol Parameter (SDR104 Unit Mode) tCLK clock period Data Transfer Mode (PP) Duty Clock Duty clock rise time 0.96 clock fall time 0.96 Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 56: Nand Timing Specification

Note SD card interface uses SDIO protocol. 5.7.3 NAND Timing Specification Nand timing specifications are shown as below. Figure 5-8 Async Waveform for Command/Address/Data Output Timing Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 57 Figure 5-10 Async Waveform for Sequential Data Read Cycle(After Read)-EOD Mode Table 5-8 Nand Timing Specifications Symbol Parameter (- Unit Asynchronous) (- mode 5) tCLS CLE setup time tCLH CLE hold time tALS ALE setup Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 58: Spicc Timing Specification

Table 5-9 SPICC Master Timing Specification Symbol Description Min. Max. Unit fCLK Clock Frequency Clock high time Clock low time TLS1 CS fall to First Rising CLK Edge TSET Data input Setup Time Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 59: Spifc Timing Specification

Figure 5-13 SPIFC Out Timing Diagram Table 5-10 SPIFC Master Timing Specification Symbol Parameter (Clock Unit 41.7MHz) fRSCLK Clock Frequency for READ instructions Clock High Time Clock Low Time Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 60: Ethernet Timing Specification

Table 5-11 Management Data Timing Specification Symbol Description Min. Typ. Max. Unit Notes tMDC MDC clock From MAC Period tMDCSU Setup time to rising edge of tMDCHD Hold time to rising edge of Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 61 RMII clock tIHD RXD & DV From PHY hold time to rising edge of RMII clock Figure 5-16 RGMII Receive Timing Diagram Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 62 RGMII TX_ 125MHz to CLK clock period tOSU TXD & TX_ From PHY EN setup time to rising edge of RGMII clock (no clock delay added) Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 63: Audio Timing Specification

5.7.7 Audio Timing Specification There are two modes for the audio I2S/TDM interface: Master mode and Slave mode, as shown below. Figure 5-18 I2S/TDM Timing Diagram, Master Mode Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. - Page 64 Measure Pointrefers to VIH, ViL parameter of Normal GPIO Specifications. Figure 5-19 2S/TDM Timing Diagram, Slave Mode Transmitter (slave mode) Symbol Parameter unit T(out) Clock period T(in) Clock period Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

- Page 65 Setup time of WS/Din thd in Hold time of WS/ tdly Delay between SCLK and Dout Note Measure Pointrefers to VIH, ViL parameter of Normal GPIO Specifications. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

-

Page 66: Pdm Timing Specification

PDM Data setup tSETUP time PDM Data hold tHOLD time Sys clock period tSYSCLK Note 1. Default PDM_SYS_CLOCK=133MHz. 2. For Sample position, please refer to PDM register PDM_CHAN_CTRL, PDM_CHAN_ CTRL1. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 67: Uart Timing Specification

SPI NAND First SPI NAND boot first Default sequence POC_1 Boot_5 USB First USB boot first Default sequence POC_2 Boot_6 SPI NOR First SPI NOR first Default sequence Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 68: Power On Reset

Force SOC enter reset mode via key to GND serial 100R resitor. Note 1. Place 1nF capacitors on RESET_N Pin. 2. VDDIO_AO power pin is only support 3.3V,not allow to power off in sleep mode. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 69: Recommended Power On Sequence

Figure 5-22 POR Wave Diagram Table 5-20 POR Specifications Parameter Symbol Min. Typ. Max. Unit Reset threshold voltage Reset delay time tDELAY 5.10 Recommended Power on sequence Example power on sequence: Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 70: Power Consumption

AVDD18_ENET 35.5mA 40mA AVDD18_AUDIO 6.6mA AVDD18_PCIE 31.6mA 40mA At 5 Gbps mode(WIFI module) AVDD18_HDMI 9.3mA 15.3mA AVDD18_SARADC 2.1mA 2.5mA AVDD18_CVBS 39.8mA 48mA AVDD18_MIPIDSI 29.6mA 40mA AVDD18_MIPICSI 16.4mA 20mA Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 71: Storage And Baking Conditions

Mounted with 168 hours of factory conditions ≤30°C/60% RH, or b. Stored per J-STD-033 3. Devices require bake, before mounting, if Humidity Indicator Card reads >10%. 4. If baking is required, refer IPC/JEDEC J-STB-033 for baking process. Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved. -

Page 72: Mechanical Dimensions

The SoC comes in a 52x46 ball matrix FCBGA RoHS package. The mechanical dimensions are given in millimeters as the following figures. Figure 6-1 Dimensions Figure 6-2 Dimension Specification Amlogic Proprietary and Confidential 0.6 (2019–07–25) Copyright © Amlogic. All rights reserved.

Need help?

Do you have a question about the S905D3 and is the answer not in the manual?

Questions and answers