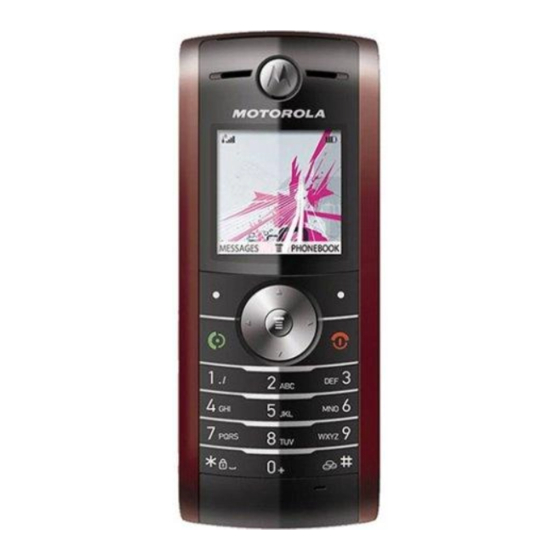

Motorola W208 Manual

Hide thumbs

Also See for W208:

- Service manual (40 pages) ,

- Manual (28 pages) ,

- Getting to know manual (8 pages)

Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Motorola W208

- Page 1 W208 Level 3 Circuit Description 22 September 2006 V1.0...

-

Page 2: Table Of Contents

W208 Level 3 Circuit Description Index Receive ....................4 1.1 Band selection................... 4 Demodulation.................... 5 Audio Codec....................6 1.3.1 Voice Downlink Patch....................7 Earpiece Receiver ..................7 Headset ....................7 Speaker Phone ..................7 Data Download Receive Path ..............8 Transmit ....................8 2.1 Audio (Voice uplink Patch)................ - Page 3 W208 Level 3 Circuit Description 13.1 Low-Dropout Voltage Regulators............... 13.2 Power Down Methods ................14 Sleep Module ..................22 14.1 Sleep Up Sequence.................. 14.2 Sleep off Sequence .................. 15 Power Tree .....................24 16 Charging Circuit and External Power .............24 16.1 Battery Support ..................

-

Page 4: Receive

W208 Level 3 Circuit Description 1 Receive 1.1 Band selection The radio frequency signal is received from internal PIFA-type antenna. Received GSM RF signal enters to PCB through the RF switch JP201. At this moment the T/R switch SW201 is switched to RX mode to let the signal input to next stage. Then the signal goes... - Page 5 W208 Level 3 Circuit Description 1.2 Locosto RX Mode Figure 2: Locosto RX Signal Process As described in Figure 2, when the RF signal is input to Locosto, it will be amplified by a differential LNA in advance, in order to obtain a better NF in the last receiving stage.

-

Page 6: Audio Codec

W208 Level 3 Circuit Description Figure 3: Baseband Downlink Block Diagram Figure 3: Audio Codec Block Diagram 1.3 Audio Codec The Audio codec consist of a voice codec dedicated to GSM application and an audio stereo line. The voice codec circuitry processes analog audio components in the uplink path and Service Engineering &... -

Page 7: Voice Downlink Patch

W208 Level 3 Circuit Description applies this signal to the voice signal interface for eventual baseband modulation. In the downlink path, the codec circuitry changes voice component data received from the voice serial interface into analog audio. The voice codec support an 8/16 kHz sampling frequency. -

Page 8: Data Download Receive Path

W208 Level 3 Circuit Description 1.7 Data Download Receive Path The External download cable is connected to the Earphone Jack J602, the headset connector of the mobile phone. The download path is routed from J602 Pin 2 via U602 Pin 1 and U607 Pin C1 to RX_Modem. The... -

Page 9: Data Download Transmit Path

W208 Level 3 Circuit Description controlled by the Baseband serial port (BSP) or the MCU serial port (USP) via the serial interfaces. The VUL path can be powered down by Program. Figure 5: Voice Uplink Paths 2.2 Data Download Transmit Path... -

Page 10: Modulation

W208 Level 3 Circuit Description The volume control is performed in the audio digital filter. Volume control is performed in steps of 1 dB from 0 dB to -30 dB. In mute state, attenuation is higher than 40 dB. The gain is independently programmable on the Left and Right channels, using the same register VAUSCTRL. - Page 11 W208 Level 3 Circuit Description main TX oscillator in Locosto. DCO stands for “digitally controlled oscillator”, which uses some digital switched capacitances to do frequency tuning, but it should be noticed that the oscillator core is still analog. And Locosto DRP uses ADPLL (all digital phase lock loop) architecture to design a digital synthesizer, and its reference frequency is provided by 26MHz DXCO.

-

Page 12: Rf Tx Pa

W208 Level 3 Circuit Description Figure 80: DCXO Block Diagram The DCXO system is shown in Figure 10 including the power management. VR2 (from Triton/Triton-Lite) is used to power this system. At the heart of the DCXO system is the DCXO core that consists of a Colpitts oscillator with an 8-bit current DAC that can be used to change the loop gain of the DCXO core. -

Page 13: Tx Pa Power Control In Sky77318

W208 Level 3 Circuit Description impedance-matching circuitry for 50 Ω input and output impedances, and a Power Amplifier Control (APC SKY77318 Pin 20) block with an internal current-sense resistor. The amplified RF output signal feeds out of SKY77318 from Pin 15 for high-band and Pin 11 for low-band. -

Page 14: Triton-Lite Monitoring Adc

W208 Level 3 Circuit Description Figure 12: Skyworks 77318 Function Block Diagram 3 Triton-Lite Monitoring ADC The monitoring section includes a 10-bit ADC and 10-bit/9-word RAM. The ADC monitors: Four internal analog values: – Battery voltage (VBAT) – Battery charger voltage (VCHG) –... -

Page 15: Microcontroller Serial Port (Usp)

W208 Level 3 Circuit Description read and write access of all internal registers under the arbitration of the internal bus controller. But its transmit path is allocated to the BDL path during burst reception for I and Q data transmissions. -

Page 16: Tft Lcd Display

8. Outline Dimension (HxVxT) : 35.4 x 40.3 x 2.95 mm 9. Weight : 5.85 +/- 0.5 g For W208, the 65K TFT LCD display is controlled by the micro wire (uWire) and GPIO interface of Locosto-Plus. Figure shows the pin connections between TFT LCD and Locosto-Plus. -

Page 17: Display Backlights

W208 Level 3 Circuit Description Figure 14: The pin connections of TFT LCD and U101 Locosto-Plus 7.1 Display Backlights The Display backlights are provided by the control signal LEDLCM_EN Locosto-Plus A5. After LEDLCM_EN Locosto-Plus Pin A5 control signal turned on, Charge Pump U701 will charge the flying capacitor (C702) to supply 5V for two shunt LEDs in LCM. -

Page 18: Sim Card Supply Voltage Generation

W208 Level 3 Circuit Description VRSIM From Triton-Lite SIM-IO SIMIO SIM-CLK SIMCK SIM-RST SIMRST SIM Connecter Locost-Plus Figure 15: SIM interface 9.1 SIM Card Supply Voltage Generation To accommodate the 1.8V or 2.9V SIM cards, the Triton-Lite includes an LDO voltage regulator that delivers supply voltage Pin A3 to the SIM module. -

Page 19: Keypad Matrix

2.7V and drain current is around 80mA. 12 Memory The W208 portable will be using the stacked combination memory parts that include flash die and PSRAM die. The Flash memory is 64Mbit size and the PSRAM memory is 16Mbit Service Engineering &... -

Page 20: Power

W208 Level 3 Circuit Description size. ADD [1:23] – Address Bus for Flash memory/PSRAM. DATA [0:15] – Data Bus for Flash memory/PSRAM F1_VCC – This is provided Flash memory I/O voltage. – Read and Write allows information to be written or read from the memory devices. -

Page 21: Power Down Methods

W208 Level 3 Circuit Description voltage (1.3 V) Triton-Lite U101. The sixth LDO (VRMMC Triton-Lite Pin T10) is a programmable regulator that generates the supply an external MMC device voltages (2.8V). The seventh LDO (VRSIM Triton-Lite Pin A3) is a programmable regulator for supply SIM-card and SIM-card device (2.8V). -

Page 22: Sleep Up Sequence

W208 Level 3 Circuit Description 14.1 Sleep Up Sequence 14.2 Sleep off Sequence Service Engineering & Optimization - 22 -... -

Page 23: Power Tree

W208 Level 3 Circuit Description 15 Power Tree Figure 119: Power Distribution Tree 16 Charging Circuit and External Power We can obtain power from battery and external charger. Power source via the accessory connector are not supported. 16.1 Battery Support... - Page 24 W208 Level 3 Circuit Description (P-MOSFET) will be turned off and stop charging. Service Engineering & Optimization - 24 -...