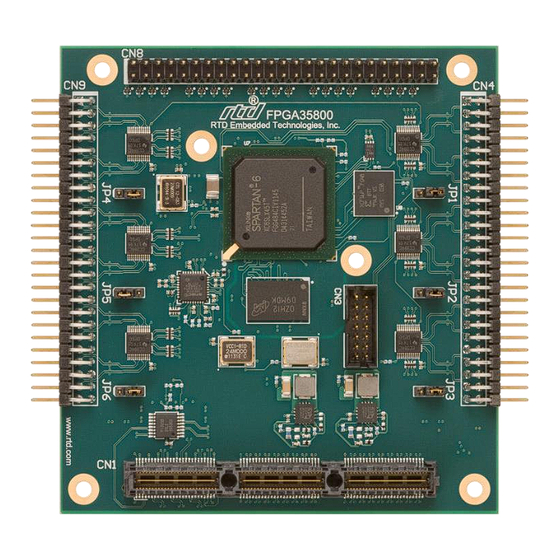

rtd FPGA35S6045HR Xilinx Spartan-6 FPGA Manuals

Manuals and User Guides for rtd FPGA35S6045HR Xilinx Spartan-6 FPGA. We have 1 rtd FPGA35S6045HR Xilinx Spartan-6 FPGA manual available for free PDF download: User Manual

Rtd FPGA35S6045HR User Manual (31 pages)

FPGA Module

Brand: Rtd

|

Category: Computer Hardware

|

Size: 1 MB

Table of Contents

Advertisement

Advertisement