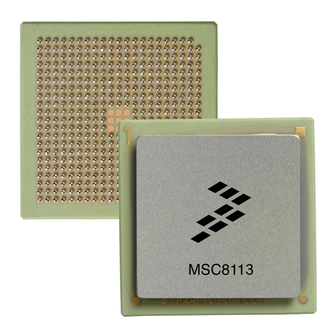

NXP Semiconductors MSC8113 Manuals

Manuals and User Guides for NXP Semiconductors MSC8113. We have 1 NXP Semiconductors MSC8113 manual available for free PDF download: Reference Manual

NXP Semiconductors MSC8113 Reference Manual (1202 pages)

Tri Core 16-Bit Digital Signal Processor

Brand: NXP Semiconductors

|

Category: Computer Hardware

|

Size: 16 MB

Table of Contents

-

-

Features30

-

Architecture37

-

-

SC140 Core39

-

M1 Memory40

-

Qbus System42

-

M2 Memory44

-

Timers51

-

Gpios52

-

-

-

-

-

Architecture58

-

-

-

Reserved Signals104

-

-

Architecture106

-

Hard Reset142

-

Soft Reset142

-

-

Boot Program

151-

Boot Basics152

-

-

Procedure Flow166

-

I 2 C System167

-

-

-

Clocks

169 -

Memory Map

181-

DSI Address Map241

-

Notes259

-

Extended Core

261-

SC140 DSP Core262

-

-

-

Memory Groups264

-

Errors266

-

Exceptions266

-

-

-

-

Architecture268

-

Fetch Unit269

-

Qbus Banks271

-

Bank Addressing272

-

Bank Registers272

-

-

-

-

Debugging289

-

-

Commands294

-

Modes294

-

Reads295

-

Restrictions295

-

Icache Registers296

-

-

-

-

Data Pipelining319

-

SDRAM Machine321

-

SDRAM Refresh328

-

Requests354

-

Clock Timing357

-

RAM Array358

-

RAM Words359

-

Last Word (LAST)367

-

Wait Mechanism368

-

-

System Bus

421-

-

Address Start425

-

Address Bus425

-

Data Arbitration429

-

Data Transfer430

-

-

-

Memory Coherency439

-

Pipeline Control455

-

-

-

-

Data Bus463

-

Address Bus466

-

-

-

Burst Transfers472

-

DSI Access Modes473

-

-

-

Status Registers495

-

-

-

-

DMA Access Modes506

-

-

Simple Buffer519

-

Cyclic Buffer520

-

Chained Buffer522

-

Data Transfers524

-

-

Architecture548

-

-

GIC Stop Mode552

-

DMA Interrupts557

-

-

-

Overview592

-

TAP Controller594

-

-

-

-

TDM Interface615

-

Gpios616

-

Timers616

-

Uart616

-

-

Stop Options618

-

-

-

TDM Interface

623-

TDM Basics628

-

Serial Interface637

-

TDM Local Memory643

-

TDM Power Saving653

-

Loopback Support654

-

-

Status Registers684

-

Uart

693-

Transmitter698

-

Break Characters701

-

Idle Characters702

-

Receiver702

-

Data Sampling704

-

Framing Error709

-

Parity Error710

-

Break Characters710

-

-

Run Mode714

-

Loop Operation715

-

Stop Mode715

-

-

-

Status Registers741

-

-

Gpio

745 -

-

Ethernet Basics771

-

-

MII Mode777

-

RMII Mode777

-

SMII Mode777

-

Special Modes778

-

Loopback Mode778

-

Echo Mode779

-

-

-

External Signals780

-

-

MII783

-

MII Receive Flow784

-

Rmii784

-

Smii786

-

-

-

Flow Control808

-

Error-Handling811

-

-

MAC Registers854

-

MIIGSK Registers866

-

RMON Support793

-

-

-

Interrupts923

Advertisement

Advertisement

Related Products

- NXP Semiconductors PowerQUICC MPC8308_RDB

- NXP Semiconductors MIMXRT1170HDUG

- NXP Semiconductors MIMXRT1170

- NXP Semiconductors MX93AUD-HAT-UM

- NXP Semiconductors MX93AUD-HAT

- NXP Semiconductors MCIMX93-EVKCM

- NXP Semiconductors MIMXRT1180-EVK

- NXP Semiconductors MCXN947VNLT

- NXP Semiconductors PowerQUICC MPC857T

- NXP Semiconductors MCXN546VNLT