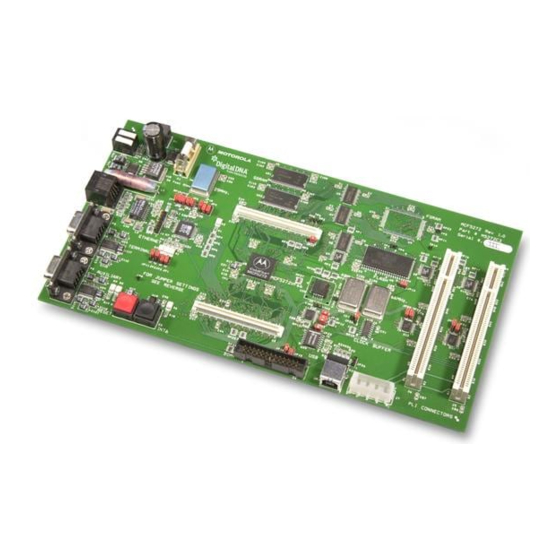

NXP Semiconductors MCF5272 ColdFire Manuals

Manuals and User Guides for NXP Semiconductors MCF5272 ColdFire. We have 1 NXP Semiconductors MCF5272 ColdFire manual available for free PDF download: User Manual

NXP Semiconductors MCF5272 ColdFire User Manual (545 pages)

Brand: NXP Semiconductors

|

Category: Computer Hardware

|

Size: 5 MB

Table of Contents

-

Number

14 -

Chapter 1

65-

UART Module66

-

Timer Module67

-

-

-

SRAM Overview104

-

ROM Overview107

-

-

Overview119

-

PSTCLK Timing120

-

-

CPU Halt134

-

-

-

BDM Command Set137

-

-

-

-

Features161

-

-

-

-

Overview191

-

SDRAM Registers196

-

Performance200

-

SDRAM Interface204

-

-

-

Overview219

-

Features219

-

-

Module Operation219

-

-

CAM Interface224

-

-

Reception Errors227

-

-

-

-

Introduction259

-

Module Operation260

-

-

Clock Generator262

-

-

-

USB Memory Map265

-

-

-

-

-

-

Endpoint Fifos288

-

Registers288

-

-

-

Data Flow290

-

IN Endpoints291

-

OUT Endpoints291

-

IN Endpoints292

-

OUT Endpoints292

-

Line Interface294

-

-

-

Introduction297

-

GCI/IDL Block299

-

-

Clock Synthesis307

-

-

PLIC Registers311

-

-

-

-

Overview339

-

Features339

-

Operation341

-

Qspi Ram342

-

QSPI RAM Model343

-

Receive RAM343

-

Command RAM344

-

Transmit RAM344

-

-

Transfer Delays345

-

Transfer Length346

-

Data Transfer346

-

-

SPI Modes Timing349

-

-

-

Overview361

-

-

Operation379

-

-

Receiver384

-

-

Receiver Timing384

-

Transmitter FIFO385

-

Receiver FIFO385

-

Looping Modes386

-

Multidrop Mode388

-

Remote Loop-Back388

-

-

Bus Operation389

-

Programming390

-

-

-

-

Overview395

-

-

-

Signal List413

-

SDRAM Controller429

-

-

Read/Write (R/W)431

-

Hi-Z432

-

Bypass432

-

-

-

-

Features449

-

-

Bus Sizing452

-

-

Interrupt Cycles467

-

20.10 Bus Errors467

-

-

-

Overview475

-

TAP Controller477

-

Restrictions482

-

Bypass Register482

-

-

-

Pinout483

-

Maximum Ratings485

-

IDL Slave Timing509

-

QSPI Timing515

-

PWM Timing516

-

-

Advertisement

Advertisement

Related Products

- NXP Semiconductors MCIMX8M-AUD

- NXP Semiconductors MCU-Link Pro

- NXP Semiconductors MCIMX7SABRE

- NXP Semiconductors MCUXpresso IDE MQX RTOS

- NXP Semiconductors MCIMX93-EVKCM

- NXP Semiconductors MCX-N5 EVK Series

- NXP Semiconductors MCX-MCXN546-EVK

- NXP Semiconductors MCX-MCXN547-EVK

- NXP Semiconductors MCXN546VDFT

- NXP Semiconductors MCXN546VNLT