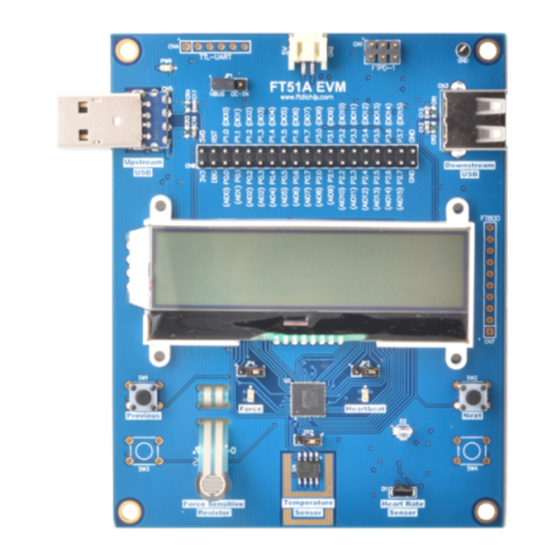

FTDI FT51A Manuals

Manuals and User Guides for FTDI FT51A. We have 1 FTDI FT51A manual available for free PDF download: Application Note

FTDI FT51A Application Note (171 pages)

Brand: FTDI

|

Category: Control Unit

|

Size: 4 MB

Table of Contents

-

-

Overview8

-

Features8

-

Scope8

-

Pin_Config20

-

Mtp_Control20

-

SPI Master26

-

Use Cases34

-

SPI Slave37

-

I2Cmsa42

-

I2C Master42

-

I2Cmcr43

-

I2Cmsr44

-

I2Cmbuf44

-

Use Case45

-

I2Cmtp45

-

I2C Slave48

-

I2Csoa48

-

I2Cscr49

-

I2Cssr49

-

Use Case50

-

I2Csbuf50

-

Uart52

-

Uart_Tx_Data53

-

Uart_Rx_Data53

-

Uart_Control53

-

Uart_Tx_Ien54

-

Uart_Tx_Int54

-

Uart_Rx_Ien55

-

Uart_Rx_Int55

-

Uart_Baud57

-

Gpios60

-

Iomux64

-

Use Cases70

-

Aio_Control71

-

AIO ADC Mode75

-

Global Mode80

-

General Commands106

-

Pwm_Control109

-

Pwm_Int_Ctrl110

-

Pwm_Prescaler110

-

Pwm_Cnt16_Lsb110

-

Pwm_Cnt16_Msb111

-

Use Cases112

-

Pwm_Init112

-

Pwm_Ctrl_Bl_Cmp8112

-

Pwm_Out_Clr_En112

-

Timers116

-

Timer_Control117

-

Timer_Control_3118

-

Timer_Control_1118

-

Timer_Control_2118

-

Timer_Control_4119

-

Timer_Int119

-

Timer_Write_Ls120

-

Timer_Presc_Ls120

-

Timer_Write_Ms120

-

Timer_Wdg120

-

Timer_Select120

-

Timer_Read_Ms121

-

Timer_Read_Ls121

-

Timer_Presc_Ms121

-

Use Cases122

-

Dma128

-

Dma_Control_X131

-

Dma_Irq_Ena_X132

-

Dma_Enable_X132

-

Dma_Irq_X133

-

Dma_Io_Addr_L_X134

-

Dma_Fifo_Data_X135

-

Dma_Curr_Cnt_L_X135

-

Use Cases136

-

Libraries138

-

USB Library139

-

DMA Library142

-

UART Library143

-

AIO Library146

-

IOMUX Library147

-

Watchdog Library147

-

DFU Library148

-

LCD Library149

-

TMC Library149

-

USB Applications151

-

Descriptors152

-

Call-Backs158

-

Main Function159

Advertisement

Advertisement