Table of Contents

Advertisement

Quick Links

Application Note

AN_289

FT51A Programming Guide

Version 1.0

Issue Date: 2015-12-21

This document provides a guide for using FT51A firmware libraries supplied

by FTDI and writing applications.

Use of FTDI devices in life support and/or safety applications is entirely at the user's risk, and the

user agrees to defend, indemnify and hold FTDI harmless from any and all damages, claims, suits

or expense resulting from such use.

Future Technology Devices International Limited (FTDI)

Unit 1, 2 Seaward Place, Glasgow G41 1HH, United Kingdom

Tel.: +44 (0) 141 429 2777

Fax: + 44 (0) 141 429 2758

Web Site:

http://ftdichip.com

Copyright © 2015 Future Technology Devices International Limited

Advertisement

Chapters

Table of Contents

Summary of Contents for FTDI FT51A

- Page 1 This document provides a guide for using FT51A firmware libraries supplied by FTDI and writing applications. Use of FTDI devices in life support and/or safety applications is entirely at the user’s risk, and the user agrees to defend, indemnify and hold FTDI harmless from any and all damages, claims, suits or expense resulting from such use.

-

Page 2: Table Of Contents

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Table of Contents 1 Introduction .............. 7 1.1 Overview ................7 1.2 Features ................7 1.3 Scope .................. 7 2 Hardware Reference ..........9 2.1 Hardware Access ............... - Page 3 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3.8 SPI_MASTER_DATA_DELAY ................31 2.3.9 SPI_MASTER_SS_SETUP ................32 2.3.10 SPI_MASTER_TRANSFER_SIZE ............... 32 2.3.11 SPI_MASTER_TRANSFER_PENDING..............33 2.3.12 Use Cases ....................33 2.4 SPI Slave ................36 2.4.1...

- Page 4 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.10 UART_BAUD ....................56 2.7.11 UART Baud Rate Example ................57 2.7.12 UART_FLOW_CTRL ..................57 2.7.13 UART_FLOW_STAT..................58 2.8 GPIOs ................59 2.8.1 Digital GPIO Pads ..................59 2.8.2...

- Page 5 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.12.1 PWM_CONTROL ................... 108 2.12.2 PWM_INT_CTRL ................... 109 2.12.3 PWM_PRESCALER ..................109 2.12.4 PWM_CNT16_LSB ..................109 2.12.5 PWM_CNT16_MSB ..................110 2.12.6 PWM_CMP16_0_LSB - PWM_CMP16_7_LSB ............ 110 2.12.7...

- Page 6 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.7 DMA_DEST_MEM_ADDR_L_x ................ 132 2.14.8 DMA_DEST_MEM_ADDR_U_x ................ 133 2.14.9 DMA_IO_ADDR_L_x ..................133 2.14.10 DMA_SRC_MEM_ADDR_U_x ..............133 2.14.11 DMA_TRANS_CNT_L_x ................134 2.14.12 DMA_TRANS_CNT_U_x ................134 2.14.13...

- Page 7 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 4 Contact Information ..........161 Appendix A – References ........... 162 Document References ............. 162 Acronyms and Abbreviations ........... 163 Appendix B – List of Tables & Figures ......164 List of Tables ................

-

Page 8: Introduction

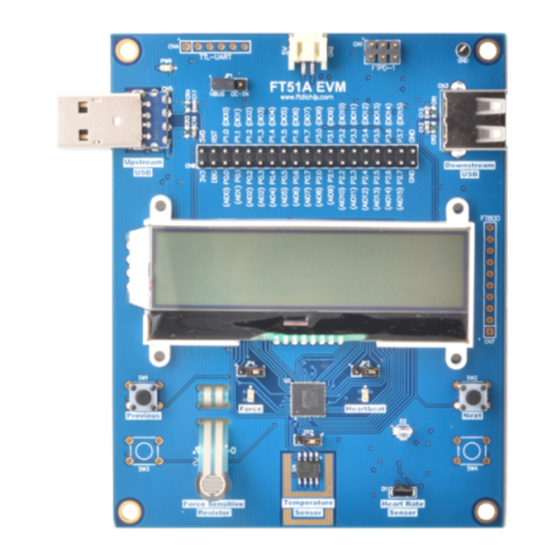

FT51A by FTDI. 1.1 Overview The FT51A series of devices provides a USB device interface, a built-in USB hub and an 8051 compatible microcontroller. The 8051 compatible component is referred to as the ‘core’. - Page 9 AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The FT51A Tools are currently only available for Microsoft Windows, and are tested on Windows 7 and Windows 8.1. The following diagram shows the overall system structure: Product Page Document Feedback Copyright ©...

-

Page 10: Hardware Reference

Clearance No.: FTDI# 483 2 Hardware Reference The FT51A has an 8051 compatible core. There are extended Special Function Registers (SFRs) to enable access to the registers of all the peripherals and modules. Certain registers are accessed directly through SFRs and others are accessed through I/O ports addressed though SFRs. -

Page 11: Hardware Access

There are 10 sets of I/O ports that permit access to the registers of the ADC, PWM, SPI Master, SPI Slave, UART FTDI, 245 FIFO, DMA, Timers, Watchdog and IOMUX. Table 2.2 summarises the methods required to access each module. -

Page 12: Register Descriptions

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 #define WRITE_IO_REG(address, data) IO_ADDR_9_H = (unsigned char)((unsigned int)(address) >> 8); \ IO_ADDR_9_L = (unsigned char)(address); IO_DATA_9 = (data); while #define READ_IO_REG(address, data) IO_ADDR_9_H = (unsigned char)((unsigned int)(address) >>... -

Page 13: Device Control Registers

AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2 Device Control Registers These registers control and provide status on the FT51A device. They are collectively referred to as the ‘top-level’ registers. Address Register Name Description... -

Page 14: Device_Control_Register

Table 2.5 Device Control Register The Device Control register provides top-level write enable and reset functions for all top-level registers on the FT51A device. This encompasses only the registers described in this chapter and not any 8051 core registers or other module’s registers. -

Page 15: System_Clock_Divider

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2.2 SYSTEM_CLOCK_DIVIDER Bit Field Name Type Reset Description Position 7..5 Reserved Set to reset the 8051 core. This will cause the 8051 state and registers to be reset. - Page 16 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 PMM is entered and exited by setting the PMM bit (PCON.0). In addition, use of the switchback feature is possible to affect a return from PMM to the full speed mode. This allows both hardware and software to cause an exit from PMM.

-

Page 17: Top_Usb_Enable

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2.3 TOP_USB_ENABLE Bit Field Name Type Reset Description Position 7..6 Reserved Controls the way the hub module identifies itself during enumeration : 1 – Hub is part of a compound... -

Page 18: Peripheral_Int0

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2.4 PERIPHERAL_INT0 Bit Field Name Type Reset Description Position 7..5 Reserved R/W1C Set when the memory contents have been successfully copied. dma3_irq Write '1' to clear interrupt. -

Page 19: Peripheral_Int1

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2.6 PERIPHERAL_INT1 Bit Field Name Type Reset Description Position R/W1C Set when the 245 FIFO has generated an interrupt. Write '1' to fifo_245_irq clear interrupt. -

Page 20: Peripheral_Ien1

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.2.7 PERIPHERAL_IEN1 Bit Field Name Type Reset Description Position Set to enable the 245 FIFO fifo_245_irq_ien interrupt. Set to enable the TIMER interrupt. timer_irq_ien Set to enable the PWM interrupt. -

Page 21: Mtp_Addr_L, Mtp_Addr_U And Mtp_Prog_Data

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Bit Field Name Type Reset Description Position When set to 1 this shall copy the contents of MTP block in to Shadow RAM. The core is held in RESET and... -

Page 22: Mtp_Crc_Ctrl, Mtp_Crc_Result_L And Mtp_Crc_Result_U

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Bit Field Name Type Reset Description Position 7..6 Reserved 5..0 Data High bytes of MTP Address Table 2.15 MTP Address (Upper) Register Bit Field Name... -

Page 23: Pin_Package_Config

Table 2.20 Pin Package Type Register 2.2.13 TOP_ SECURITY_LEVEL There are 3 security levels built into the FT51A. Security Level 0 (SL0) – No security. Reads and writes possible from Program Memory. Security Level 1 (SL1) – Reads are blocked via debugger to certain address sectors. -

Page 24: Table 2.21 Top Level Security Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Bit Field Name Type Reset Description Position 7..5 Reserved Set to protect sector: Start Address: 0x0000 End Address: 0x3FBF Global_Bit 0= Sector level security applied as per bits[3:0]. - Page 25 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The security bits are categorised as write forward, as once a particular level has been set it is not possible to go back to a lower security level.

-

Page 26: Spi Master

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3 SPI Master The Serial Peripheral Interface Bus is an industry standard communications interface. Devices communicate in Master / Slave mode, with the Master initiating the data transfer. -

Page 27: Table 2.22 Spi Master Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Register Name Description Address 0x50 SPI Master top level control register SPI_MASTER_CONTROL 0x51 Transmit data register SPI_MASTER_TX_DATA 0x52 Receive data register SPI_MASTER_RX_DATA 0x53 Interrupt Enable register... -

Page 28: Spi_Master_Control

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 transfer_size_done_int interrupt in SPI_MASTER_INT. The SPI_MASTER_DATA_DELAY register must be non-zero to use this method. Data transfers can also be controlled by DMA: more details can be found in the DMA section of this document. -

Page 29: Spi_Master_Ien

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3.4 SPI_MASTER_IEN Bit Field Name Type Reset Description Position 7..6 Reserved When set will enable transfer_size_done_ien transfer_size_done_int When set will enable rx_oe_int rx_oe_ien When set will enable rx_full_int... -

Page 30: Spi_Master_Int

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3.5 SPI_MASTER_INT Bit Field Name Type Reset Description Position 7..6 Reserved Indicates when a transmission of the SPI_MASTER_TRANSFER_SIZE bytes has R/W1C transfer_size_done_int completed. Indicates an Rx overrun error when data is received and SPI_MASTER_RX_DATA is still full. -

Page 31: Spi_Master_Setup

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3.6 SPI_MASTER_SETUP Bit Field Name Type Reset Description Position 7..4 Reserved SPI Slave Select. Used when the CPU wishes to control a SS# signal. When... -

Page 32: Spi_Master_Clk_Div

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The SPI Slave Select signal is enabled or disabled with the spi_ss_n bit. The spi_ss_n bit should NOT be used in conjunction with SPI Transfer Size register. -

Page 33: Spi_Master_Ss_Setup

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.3.9 SPI_MASTER_SS_SETUP Bit Field Name Type Reset Description Position 7..3 Reserved SPI Slave Select Route. Two bits set 2..1 the active slave select out of the 4 ss_route different slave selects. -

Page 34: Spi_Master_Transfer_Pending

WRITE_IO_REG(0x0050, 0x01); // Reset to a known state WRITE_IO_REG(0x0050, 0x02); // Enable SPI Master device before any setup not after. WRITE_IO_REG(0x0056, 0x60); // Divide the FT51A system clock by 0x60 WRITE_IO_REG(0x0058, 1 << 0x00 // Set SS Idle State to High, | 0 <<... - Page 35 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 | 1 << 0x03); // Set SS high, i.e. deactivate it 2.3.12.2 Polled Interface The SPI Master device is used as a polled interface sending a command to an SPI slave and reading a response.

- Page 36 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 SPIM_MISO_buf++; WRITE_IO_REG(0x54, 0x1<<3); //Clear RX_FULL interrupt if(SPIM_interrupt & 0x1) // Check for TX_HOLD interrupt if(SPIM_num_bytes_tx > 1) WRITE_IO_REG(0x51, *SPIM_MOSI_buf); //SPI_MASTER_DATA_TX_ADDR_1 SPIM_MOSI_buf++; WRITE_IO_REG(0x54, 0x1); //Clear TX_HOLD interrupt...

-

Page 37: Spi Slave

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.4 SPI Slave The Serial Peripheral Interface Bus is an industry standard communications interface. Devices communicate in Master or Slave modes, with the Master initiating the data transfer. -

Page 38: Spi_Slave_Control

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 is followed by a data byte being clocked out with the master driving CLK. The master always supplies the first byte, which is called a command byte. After this the desired number of data bytes are transferred before the transaction is terminated by the master de-asserting slave select. -

Page 39: Spi_Slave_Rx_Data

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.4.3 SPI_SLAVE_RX_DATA Bit Field Name Type Reset Description Position Byte of data received by the SPI 7..0 Data Slave module Table 2.39 SPI Slave Receive Register This register contains data that was sent from the SPI Master. -

Page 40: Spi_Slave_Int

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.4.5 SPI_SLAVE_INT Bit Field Name Type Reset Description Position 7..6 Reserved Indicates the module is busy tx_busy processing a transfer Indicates a RX overrun error when... -

Page 41: Spi_Slave_Setup

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.4.6 SPI_SLAVE_SETUP Bit Field Name Type Reset Description Position 7..3 Reserved When HIGH, data is transferred LSB first. When LOW, data is transferred lsbfirst MSB first. -

Page 42: I2C Master

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.5 I C Master The I C is an industry standard communications interface. Devices communicate in Master or Slave mode, with the Master initiating the data transfer. -

Page 43: I2Cmcr

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.5.2 I2CMCR The I C Master Control register is accessed only during a write. If this register is read then it will return the status value of the I2CMSA register. -

Page 44: I2Cmsr

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.5.3 I2CMSR The I C Master Status register is accessed only during a read operation. Bit Field Name Type Reset Description Position Reserved Reserved Indicates that the Bus is Busy, and access is not possible;... -

Page 45: I2Cmtp

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.5.5 I2CMTP Bit Field Name Type Reset Description Position Set to select the timer period register for HIGH speed I C Master. HS_TIMER_SELECT Clear for timer period register for STANDARD, FAST and FAST+. - Page 46 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.5.6.2 Send Data To send data to an I C Slave the following procedure is used: For a single cycle: Write the slave address to the I2CMSA register and set bit R/S to 0.

- Page 47 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Read the I2CMSA register until the BUSY bit is clear. Read the first byte of data from the I2CMBUF register. For the remaining bytes (except the last byte): Write to the Control Register I2CMCR with HS=0, ACK=1, STOP=0, START=1, ...

-

Page 48: I2C Slave

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.6 I C Slave The I C Slave is an industry standard communications interface. Devices communicate in Master or Slave mode, with the Master initiating the data transfer. -

Page 49: I2Cscr

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The Own Address register sets the address that the I C Slave will respond to. The most significant 7 bits of the address are set in this register. The least significant bit is ‘1’ for a read by the I Master or ‘0’... -

Page 50: I2Csbuf

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The I C Slave has been addressed for a read operation by the I C Master TREQ and must send a byte of data. This bit is automatically cleared by a write to I2CSBUF. - Page 51 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.6.5.3 Receive Data To receive data from an I C Master the following procedure is used: For each byte of data: If I2CSCR register bit RREQ set to ‘1’: Read byte of data from I2CSBUF.

-

Page 52: Uart

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7 UART The UART block provides: Full RS232 support; Baud Rate Generator; Optional hardware flow control via RTS / CTS and DTR / DSR;... -

Page 53: Uart_Control

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.1 UART_CONTROL Bit Field Name Type Reset Description Position 7..2 Reserved Reserved Write 1 to Enable UART uart_dev_en Write 1 to Reset UART uart_soft_reset Table 2.56 UART Control Register... -

Page 54: Uart_Tx_Ien

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.5 UART_TX_IEN Bit Field Name Type Reset Description Position 7..6 Reserved Reserved Interrupt enable bit for dcd_int dcd_ien Interrupt enable bit for ri_int ri_ien... -

Page 55: Uart_Rx_Ien

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.7 UART_RX_IEN Bit Field Name Type Reset Description Position 7..5 Reserved Reserved Enable bit for break_rcvd_int break_rcvd_ien interrupt Enable bit for stop_error_int stop_error_ien interrupt... -

Page 56: Uart_Line_Ctrl

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.9 UART_LINE_CTRL Bit Field Name Type Reset Description Position 7..6 Reserved Reserved When set, the txd line goes into a ‘spacing’ state which causes a break set_break in the receiving UART. -

Page 57: Uart_Baud

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.10 UART_BAUD Bit Field Name Type Reset Description Position 7..0 0x88 Lower byte of the baud rate setting uart_baud_0 Table 2.65 UART Baud Rate 0 Register... -

Page 58: Uart Baud Rate Example

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.11 UART Baud Rate Example Baud Rate Example The Baud Rate is defined by the value programmed into registers UART_BAUD_0, UART_BAUD_1 and UART_BAUD_2. This value is used as a divisor of the system clock frequency. -

Page 59: Uart_Flow_Stat

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.7.13 UART_FLOW_STAT Bit Field Name Type Reset Description Position 7..4 Reserved Reserved Status of the Ring Indicator signal ri_reg Status of the Data Carrier Detect... -

Page 60: Gpios

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.8 GPIOs GPIOs are divided into Digital and Analogue pads. Digital inputs and outputs should be mapped to the digital pads but can be mapped to analogue pads if required. Analogue inputs and outputs must be mapped to the analogue pads. -

Page 61: Analogue Gpio Pads

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.8.1.1 DIGITAL_CONTROL_GPIO_0 to DIGITAL_CONTROL_GPIO_15 Bit Field Name Type Reset Description Position 7..6 Reserved Slew Rate Control. When sr=0 slew RATE is NORMAL. When sr=1 slew RATE is SLOW Schmitt Trigger Enable. -

Page 62: Table 2.72 Gpio Aio Digital Control Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Register Name Description Address 0x0A Control register for AIO 0 in digital DIGITAL_CONTROL_AIO_0 mode 0x0B Control register for AIO 1 in digital DIGITAL_CONTROL_AIO_1 mode... -

Page 63: Table 2.73 Gpio Aio Digital Control Registers

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.8.2.1 DIGITAL_CONTROL_AIO_0 to DIGITAL_CONTROL_AIO_15 Bit Field Name Type Reset Description Position 7..4 Reserved Pull down Enable. When this signal is set, a weak internal pull down is enabled to hold the pdena pad in a "low"... -

Page 64: Iomux

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.9 IOMUX The IOMUX allows any peripheral interface input or output signal to be assigned to any of the available IO pins. There are however some limitations: ... -

Page 65: Iomux_Output_Pad_Sel

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.9.2 IOMUX_OUTPUT_PAD_SEL Bit Field Name Type Reset Description Position Pad to be used for an output 7..0 0x00 op_pad_sel mapping. Table 2.76 IOMUX Output Pad Select Register This register selects the output pad for a signal mapping. -

Page 66: Iomux_Input_Pad_Sel

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.9.5 IOMUX_INPUT_PAD_SEL Bit Field Name Type Reset Description Position 7..0 0x00 Pad to be used for an input mapping. ip_pad_sel Table 2.79 IOMUX Input Pad Select Register This register selects the input pad for a signal mapping. -

Page 67: Iomux Output Signal Mapping Values

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IOMUX Pad Value IOMUX Pad Value AIO_0 DIO_0 AIO_1 DIO_1 AIO_2 DIO_2 AIO_3 DIO_3 AIO_4 DIO_4 AIO_5 DIO_5 AIO_6 DIO_6 AIO_7 DIO_7 AIO_8 DIO_8... - Page 68 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IOMUX Output Signals Value IOMUX Output Signals Value I2C_MASTER_SDA PWM_OUT_13 I2C_MASTER_SCL PWM_OUT_03 HUB_P2_PWREN I2C_MASTER_SCLH GPIO_PORT3O_7 I2C_SDA GPIO_PORT3O_6 I2C_SCL GPIO_PORT3O_5 SPI_SLAVE_MOSI_OUT GPIO_PORT3O_4 SPI_SLAVE_MISO GPIO_PORT3O_3 SPI_MASTER_SS_N_0...

-

Page 69: Iomux Input Signal Mapping Values

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IOMUX Output Signals Value IOMUX Output Signals Value PWM_OUT_5 GPIO_PORT0O_3 PWM_OUT_44 GPIO_PORT0O_2 PWM_OUT_34 GPIO_PORT0O_1 PWM_OUT_24 GPIO_PORT0O_0 Table 2.81 IOMUX Output Signal Mapping Values 2.9.8 IOMUX Input Signal Mapping Values Table 2.82 contains the input signal selection values to map to input pads. -

Page 70: Use Cases

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IOMUX Input Signals Value IOMUX Input Signals Value FIFO_245_DATA_WRITE_6 GPIO_PORT0I_3 FIFO_245_DATA_WRITE_5 GPIO_PORT0I_2 FIFO_245_DATA_WRITE_4 GPIO_PORT0I_1 FIFO_245_DATA_WRITE_3 GPIO_PORT0I_0 FIFO_245_DATA_WRITE_2 Table 2.82 IOMUX Input Signal Mapping Values 2.9.9... -

Page 71: Analogue Io Ports

Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10 Analogue IO Ports The FT51A has up to 16 Analogue IO pads available, depending on package type. The number of pads for each package type is shown in Table 2.83. Package... -

Page 72: Implementation

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.2 Implementation Analogue-to-digital conversion is implemented using a DAC to successively approximate (in hardware) the output of a sample-and-hold circuit. Physically, there are four DACs, each shared by four AIO ports, as illustrated below. -

Page 73: Table 2.86 Aio Mode Control Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Address Register Name Description 0x102 Selects AIO ports 0 - 3 AIO_MODE_0 0x103 Selects AIO ports 4 - 7 AIO_MODE_1 0x104 Selects AIO ports 8 - 11... -

Page 74: Table 2.89 Aio Mode Control 1 Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.3.2 AIO_MODE_1 Bit Field Name Type Reset Description Position Analogue mode of operation for 7..6 AIO_7_MODE AIO_7 port. See Table 2.87 Analogue mode of operation for 5..4... -

Page 75: Aio Adc Mode

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.4 AIO ADC Mode During ADC the incoming analogue signal to the AIO pad is sampled to provide a digital representation of the wave. - Page 76 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Address Register Name Description 0x108 Sample AIO ports 0 – 7 AIO_SAMPLE_0 0x109 Sample AIO ports 8 – 15 AIO_SAMPLE 1 0x13E AIO_0_ADC_DATA_L Lower byte of AIO_0 ADC data...

-

Page 77: Table 2.92 Aio Adc Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 0x15B AIO_14_ADC_DATA_U Upper 2 bits of AIO_14 ADC data 0x15C AIO_15_ADC_DATA_L Lower byte of AIO_15 ADC data 0x15D AIO_15_ADC_DATA_U Upper 2 bits of AIO_15 ADC data Table 2.92 AIO ADC Register Addresses... -

Page 78: Aio Interrupts

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.4.3 AIO_x_ADC_DATA_L Bit Field Name Type Reset Description Position Digital representation of the LOWER DATA analogue value (lower). 7..0 Discard bits 0..1 Table 2.95 AIO ADC Sample Result (Lower) Registers 2.10.4.4 AIO_x_ADC_DATA_U... -

Page 79: Table 2.98 Aio Interrupts 0-7 Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.5.1 AIO_INTERRUPTS_0_7 Bit Field Name Type Reset Description Position AIO_7_INT AIO_6_INT AIO_5_INT Set when an A-D conversion is AIO_4_INT complete for that particular Analogue Cell. -

Page 80: Global Mode

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.5.3 AIO_INTERRUPT_ENABLES_0_7 Bit Field Name Type Reset Description Position AIO_7_IEN AIO_6_IEN AIO_5_IEN Interrupt Enable bit. AIO_4_IEN Write a 1 to enable the corresponding interrupt bit in register... -

Page 81: Table 2.102 Aio Global Mode Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Address Register Name Description 0x101 Interrupt enables and status bits AIO_GLOBAL_CTRL Used to include ports 0-7 in the global AIO_GLOBAL_PORT_SELECT_0_7 0x10B list Used to include ports 8-15 in the global... -

Page 82: Table 2.103 Aio Global Mode Select 0-7 Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.6.2 AIO_GLOBAL_PORT_SELECT_0_7 Bit Field Name Type Reset Description Position Write 1 to include Port in Global List aio_port_7_active Write 1 to include Port in Global List... -

Page 83: Differential Mode

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 AIO Port DAC Used Recommendation AIO_0 DAC_0 For this shared DAC, use no AIO_1 DAC_0 more than two ports in Global AIO_2 DAC_0 mode... -

Page 84: Settling Times

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.7.1 AIO_DIFFERENTIAL_ENABLE Bit Field Name Type Reset Description Position Write 1 to configure AIO Pads 14 diff_14_15 and 15 as a differential pair Write 1 to configure AIO Pads 12... -

Page 85: Table 2.108 Aio Settling Times Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Address Register Name Description This register allows the user to change the amount of time that the AIO block will wait for the Sample and Hold circuit to complete its function. -

Page 86: Table 2.111 Clock Divider Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.8.2 Settling Time Examples (for optimal performance) The ADC function has the following characteristics: DAC max settling time 0.245µs Sample & Hold, max settling time 11.8µs... -

Page 87: Adc Programming Flow

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.10.9 ADC Programming Flow Single Sample Write to the appropriate mode register (AIO_MODE_0, AIO_MODE_1, AIO_MODE_2, AIO_MODE_3) select mode (see AIO_MODE Control AIO_0_MODE AIO_15_MODE for more details) ... -

Page 88: Usb Full Speed Device Controller

Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11 USB Full Speed Device Controller The FT51A contains USB Full Speed device controller based on the FT122 technology. The registers to access the device are shown in Table 2.112. -

Page 89: Table 2.114 Endpoint Configuration For Ep2

USB bus and the FT51A core. For example, for EP2 IN endpoint (EPI5), the USB host can read data from Buffer 0 while the FT51A core is writing to Buffer 1. The USB host can subsequently read from Buffer 1 without waiting for it to be filled. Buffer switching is handled automatically by the USB Full Speed device controller. -

Page 90: Table 2.115 Example Buffer Configuration

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Configuration 0 Configuration 1 Configuration 2 Buffer Buffer Buffer (ISO) (128 bytes) (ISO) (128 bytes) (ISO) (448 bytes) (ISO) (192 bytes) (ISO) (448 bytes) -

Page 91: Table 2.116 Endpoint Maximum Packet Size

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Endpoint buffer size register Non-isochronous Isochronous setting (binary) endpoint endpoint 0000 8 bytes 16 bytes 0001 16 bytes 32 bytes 0010 32 bytes 48 bytes... -

Page 92: Command Summary

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.2 Command Summary Command Name Target Code (hex) Data phase Initialization Commands Set Address Enable Device 0xD0 Write 1 byte Set Endpoint Enable Device... -

Page 93: Table 2.117 Default Command Set

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Command Name Target Code (hex) Data phase Validate Buffer Selected Endpoint 0xFA None General Commands Read Current Frame Device 0xF5 Read 1 or 2 bytes... - Page 94 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Command Name Target Code (hex) Data phase Initialization Commands Set Address Enable Device 0xD0 Write 1 byte Set Endpoint Enable Device 0xD8 Write 1 byte...

- Page 95 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Command Name Target Code (hex) Data phase Endpoint 6 IN 0x0D Read 1 byte (optional) Endpoint 7 OUT 0x0E Read 1 byte (optional) Endpoint 7 IN...

-

Page 96: Table 2.118 Enhanced Command Set

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Command Name Target Code (hex) Data phase Write Buffer Selected Endpoint 0xF0 Write n bytes Set Endpoint Status Endpoint 0 OUT 0x40 Write 1 byte... -

Page 97: Initialization Commands

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.3 Initialization Commands 2.11.3.1 Set Address Enable Command : 0xD0 Data : Write 1 byte Symbol Reset Description USB assigned device address. A bus reset will reset all 6..0... -

Page 98: Table 2.121 Configuration Register (Byte 1)

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Symbol Reset Description Reserved Reserved, write to 0 0: CLKOUT switches to 30 kHz during USB suspend 1: CLKOUT remains unchanged during USB suspend... -

Page 99: Table 2.122 Clock Division Factor Register (Byte 2)

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Symbol Reset Description The Clock Division Factor value (CDF) determines the output clock frequency on the CLKOUT pin. Frequency = 48 MHz / (CDF +1), where CDF ranges 1-12 or the allowed CLKOUT frequency is 4-24 MHz. -

Page 100: Data Flow Commands

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.4 Data Flow Commands 2.11.4.1 Read Interrupt Register Command : 0xF4 Data : Read 1 or 2 bytes (Default Mode); Read 1-4 bytes (Enhanced Mode) -

Page 101: Table 2.126 Interrupt Register Byte 3 (For Enhanced Mode)

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Symbol Reset Description Interrupt for endpoint 3 OUT buffer. Cleared by Read Endpoint 3 Out Last Transaction Status command. Interrupt for endpoint 3 IN buffer. Cleared by Read Last Endpoint 3 In Transaction Status command. -

Page 102: Table 2.128 Endpoint Status Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.4.2 Select Endpoint Command : 0x00-0x05 (0x00-0x0F for Enhanced Mode) Data : Optional Read 1 byte Symbol Reset Description 0: selected endpoint buffer is empty... -

Page 103: Table 2.130 Transaction Error Code

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Error Code Result 0000 No error 0001 PID encoding error 0010 PID unknown 0011 Unexpected packet 0100 Token CRC error 0101 Data CRC error... -

Page 104: Table 2.131 Endpoint Buffer Status Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.4.4 Read Endpoint Status Command : 0x80-0x85 (0x80-0x8F for Enhanced Mode) Data : Read 1 byte Symbol Reset Description 1..0 Reserved Reserved 0: indicates packet is not a setup packet... -

Page 105: Table 2.132 Endpoint Control Register

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.4.7 Clear Buffer Command : 0xF2 Data : None Following a Read Buffer command, the Clear Buffer command should be issued after all data has been read out from the endpoint buffer. -

Page 106: General Commands

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.11.5 General Commands 2.11.5.1 Read Current Frame Number Command : 0xF5 Data : Read One or Two Bytes Symbol Reset Description Frame number for last received SOF, byte 1 (least 7..0... -

Page 107: Pulse Width Modulation

2.12 Pulse Width Modulation The Pulse Width Modulation (PWM) module provides a number of PWM outputs individually controlled by the FT51A CPU. The main purpose is to generate PWM signals which can be used to control motors, DC/DC converters, AC/DC supplies, etc. -

Page 108: Table 2.135 Pwm Register Addresses

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 0x92 PWM comparator MSB register 6 PWM_CMP16_6_MSB 0x93 PWM comparator LSB register 7 PWM_CMP16_7_LSB 0x94 PWM comparator MSB register 7 PWM_CMP16_7_MSB 0x95 PWM out toggle enable register 0... -

Page 109: Pwm_Control

Real world applications of PWM include lamp brightness, electric motor control and servo control. The FT51A has 8 independent PWM channels. The following describes all registers used to control these PWM channels. -

Page 110: Pwm_Int_Ctrl

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.12.2 PWM_INT_CTRL Bit Field Name Type Reset Description Position 7..6 Reserved Reserved PWM interrupt pwm_int PWM interrupt enable pwm_int_ien PWM busy pwm_busy PWM trigger enable: 00 disabled,... -

Page 111: Pwm_Cnt16_Msb

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.12.5 PWM_CNT16_MSB Bit Field Name Type Reset Description Position 7..0 MSB of a 16-bit counter value cnt16_msb Table 2.140 PWM Counter MSB Register This is a MSB part of a programmable counter that determines the period of the PWM signal. -

Page 112: Pwm_Out_Clr_En

The following section describes an example of how to generate a 4-pulse PWM waveform using the FT51A, which toggles at the following counter states: 7, 8, 12, 14, 15, 16, 19, and 22. Figure 2.9 Pulse Waveform generated by 8 comparators In this example there are eight toggle events and all eight comparators are used. -

Page 113: Table 2.147 Programming 8 Ft51A Comparators To Generate Above Waveform

Pre-scale by 1 to get the PWM Clock equalling to a half of the FT51A System Clock. Pre-scale by 255 to get the PWM Clock equalling to the FT51A System Clock divided by 256, etc. Therefore to get the required PWM Clock frequency use the following formula and code:... -

Page 114: Table 2.149. Pwm Ranges

PWM pulse is influenced by two parameters: PWM Clock and PWM Counter, giving two extreme situations (min and max): 1 - (assuming the 48MHz FT51A System Clock) Set the PWM Clock to its maximum value of 48MHz and increment PWM counter only by one to get the PWM pulse of roughly 20ns. - Page 115 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 // Assign PWM output pad WRITE_IO_REG (0x41, 12); // IOMUX_OUTPUT_PAD_SEL, pad number AIO_12 WRITE_IO_REG (0x42, 38);// IOMUX_OUTPUT_SIG_SEL, PWM_OUT_03 WRITE_IO_REG(0x16, 1); // DIGITAL_CONTROL_AIO_12 //Set PWM Comparator 0 WRITE_IO_REG(0x86, 0x00);...

-

Page 116: Timers

The FT51A is equipped with two types of timers: standard 8051 timers and FTDI timers. Standard timers are Timer 0, 1 and 2 which are accessed through SFRs, while the FTDI timers comprise 16- bit Timers A, B, C and D and are controlled by means of I/O registers. . -

Page 117: Timer_Control

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Register Name Description Address 0x70 Timers top level control register TIMER_CONTROL 0x71 Timer start/stop control register TIMER_CONTROL_1 0x72 Timer pre-scaler and watchdog TIMER_CONTROL_2 0x73... -

Page 118: Timer_Control_1

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.13.2 TIMER_CONTROL_1 Bit Field Name Type Reset Description Position Stop the timer D stop_D Stop the timer C stop_C Stop the timer B stop_B... -

Page 119: Timer_Control_4

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.13.5 TIMER_CONTROL_4 Bit Field Name Type Reset Description Position Pre-scaler clear. presc_clear Clear Timer D. clear_D Clear Timer C. clear_C Clear Timer B. clear_B Clear Timer A. -

Page 120: Timer_Select

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.13.7 TIMER_SELECT Bit Field Name Type Reset Description Position Timer read select bits. - 00 for timer A 3..2 - 01 for timer B... -

Page 121: Timer_Presc_Ms

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.13.12 TIMER_PRESC_MS Bit Field Name Type Reset Description Position 7..0 Bits 15 to 8 of the pre-scale value. timer_presc_15_8 Table 2.162 Timer Prescaler MSB Register 2.13.13... -

Page 122: Use Cases

Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.13.15 Use Cases The table below presents normal operation of FTDI timers along with pre-scaler and watchdog. FTDI timers Prescaler Watchdog Select the timer to initialise by writing Write an initial value... - Page 123 Clearance No.: FTDI# 483 2.13.15.1 Timers Below is a comparison of steps necessary to setup a standard 8051 Timer 0 versus the FTDI Timer Standard 8051 Timer 0 //Set the Timer 0 prescaler to 0 (0 – divide-by-12, 1 – divide-by-4) //Note: CKCON bit 3 relates to Timer 0, bit 4 Timer 1 CKCON &= 0xF7;...

-

Page 124: Table 2.166 Available Timer Ranges (In Seconds)

WRITE_IO_REG (0x71, 0x01); //TIMER_CONTROL_1, START_A FTDI Timers A, B, C and D require 1 cycle per instruction, whereas standard timers 0, 1 or 2 require either 12 (default) or 4 cycles per instruction. Additionally, the clock for Timers A, B, C and D can also be pre-scaled, which changes the available time range. -

Page 125: Figure 2.10 Timer Range For Uint32_T Timer

TIMER_WDG register) to verify proper software execution. If a hardware or software failure prevents feeding the watchdog within the minimum timeout period, the FT51A reset is forced. Once the system has undergone the reset, it is possible to check with the wdg_int bit of the TIMER_CONTROL_2 register whether the reset was caused by a watchdog overflow or normal reset. - Page 126 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 CLEAR_WDG); // Start the watchdog. WRITE_IO_REG(TIMER_CONTROL_2, MSTART_WDG); @brief Watchdog Feed @details The function feeds the watchdog in order to prevent it from resetting the system.

- Page 127 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 return 0; @brief Main @details Main program entry point. @return No! Returning from main() is undefined! int main() RESET_REASON reset_reason = WATCHDOG_RESET; Once the cause of the reset is known, the behaviour of the app can be changed accordingly.

-

Page 128: Dma

Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14 DMA The DMA relieves the CPU from performing a data/memory transfer. Below is a list of registers associated with FTDI DMA feature. There are 4 DMA engines available. Register Name Description Address... - Page 129 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IO Peripheral DMA enable/reset 0xC1 DMA_ENABLE_2 register IO Peripheral DMA interrupts enable 0xC2 DMA_IRQ_ENA_2 register IO Peripheral DMA Interrupts 0xC3 DMA_IRQ_2 register IO Peripheral DMA source memory...

- Page 130 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 address LSB register IO Peripheral DMA source memory 0xD5 DMA_SRC_MEM_ADDR_U_3 address MSB register IO Peripheral DMA destination 0xD6 DMA_DEST_MEM_ADDR_L_3 memory address LSB register IO Peripheral DMA destination...

-

Page 131: Dma_Control_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 IO Peripheral DMA IO Address LSB 0xE8 DMA_IO_ADDR_L_4 Register IO Peripheral DMA IO Address MSB 0xE9 DMA_IO_ADDR_U_4 Register IO Peripheral DMA Transfer Byte 0xEA... -

Page 132: Dma_Enable_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.2 DMA_ENABLE_x Bit Field Name Type Reset Description Position 7..2 Reserved Reserved IO Peripheral DMA Stop dma_stop IO Peripheral DMA Start dma_start Table 2.169 DMA Enable/Reset Register 2.14.3 DMA_IRQ_ENA_x... -

Page 133: Dma_Irq_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.4 DMA_IRQ_x Bit Field Name Type Reset Description Position 7..3 Reserved Reserved IO Peripheral DMA FIFO Data dma_fifo_davail_int Available IRQ dma_fifo_full_int IO Peripheral DMA FIFO Full IRQ... -

Page 134: Dma_Dest_Mem_Addr_U_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.8 DMA_DEST_MEM_ADDR_U_x Bit Field Name Type Reset Description Position IO Peripheral DMA Destination Memory Address Increment/decrement: dma_dest_mem_addr_id 0 == inc mem addr, 1 == dec mem addr IO Peripheral DMA Destination 6..0... -

Page 135: Dma_Trans_Cnt_L_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.11 DMA_TRANS_CNT_L_x Bit Field Name Type Reset Description Position IO Peripheral DMA Transfer Byte 7..0 dma_trans_cnt_l Count Register [7..0] Table 2.178 IO Peripheral DMA Transfer Byte Count LSB Register 2.14.12... -

Page 136: Dma_Afull_Trigger_X

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 2.14.16 DMA_AFULL_TRIGGER_x Bit Field Name Type Reset Description Position IO Peripheral DMA Almost Full Trigger 5..0 dma_afull_trigger Value Table 2.183 IO Peripheral DMA Almost Full Trigger Value 2.14.17... - Page 137 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 // Check what engine interrupted void INT0_ISR(void) __interrupt (0) uint8_t events = 0; READ_IO_REG(TOP_INT0, events); events &= (DMA0_IRQ | DMA1_IRQ | DMA2_IRQ | DMA3_IRQ);...

-

Page 138: Application Guide

The filename containing the function is noted along with any other files that the function requires. 3.1.1 Configuration Library This library contains functions or macros to properly initialise the FT51A, query or set the system clock frequency (6, 12, 24 or 48 MHz) and determine the IC package. Source Folder: general_configuration 3.1.1.1 device_initialise() -

Page 139: Usb Library

3.1.2 USB Library The USB library is designed to manage the interface from the FT51A device to the host. The library invokes call-back functions in the application code when certain events happen, such as the host issuing a standard request, or resetting the bus. - Page 140 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The function will initialise memory structures for control IN and OUT endpoints and register an interrupt handler for peripheral interrupts from the USB device. The hub will be configured as requested and the USB Full Speed device controller device will be enabled ready to be discovered by the host.

- Page 141 This is the routine that handles interrupts from the USB Full Speed device controller device on the FT51A. It will check and clear interrupt status bits and call handler routines accordingly. When USB_initialise is called, it will register this function as the handler for USB interrupts.

-

Page 142: Dma Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.1.3 DMA Library The UART, 245 FIFO and SPI interfaces can send/receive data directly to/from RAM without the intervention of the 8051 core using the DMA controller. It can also send data around RAM without using a peripheral interface. -

Page 143: Uart Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 The FIFO mode is always paired with a pull DMA engine. Flow control can be enabled for certain peripherals such as the UART to activate and deactivate flow control depending on the amount of data stored in a FIFO buffer. -

Page 144: Spi Master Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Requires: ft51_general_config_get_system_clock.c This function will calculate the baud rate divisor values for the UART_BAUD_0, UART_BAUD_1 UART_BAUD_2, taking into account the speed of the system clock. -

Page 145: I2C Master Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.1.5.1 SPIM_configure_slave File: ft51_spim_configure_slave.c This function is used to configure the SPI Master to connect to a slave device with the required communication properties. The master’s bit order, clock speed, clock mode and slave select idle and polarity matched to the slave device. -

Page 146: I2C Slave Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.1.6.3 I2C_master_get_status File: ft51_i2c_master.c This function returns the value of the I2CMSR register. 3.1.6.4 I2C_master_write File: ft51_i2c_master.c This will perform an I C write to a specified slave address. The first byte sent is designated to be a command byte and is passed separately from the optional data packet in the function parameters. -

Page 147: Iomux Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.1.8.1 AIO_intialise File: ft51_aio_initialise.c Set up the AIO Cell Controller. 3.1.8.2 AIO_read File: ft51_aio_read.c Perform an ADC operation on one analogue pad and wait for the result. -

Page 148: Dfu Library

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.1.10.2 watchdog_feed File: ft51_watchdog_feed.c Feed the watchdog and therefore restore the start value to the watchdog timer. 3.1.10.3 reset_cause File: ft51_watchdog_reset_cause.c Get the reason for the last reset of the device. This can be a normal reset or a watchdog reset. -

Page 149: Lcd Library

The LCD library provides functions and methods for using an ST7036 LCD display and compatibles. It requires the I C Master library to provide the communication between the FT51A and the LCD display. This library is in a single file Source Folder: lcd File: ft51_lcd_st7036.c... - Page 150 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Requires: ft51_usb_transfer.c, ft51_usb_endpoint_features.c 3.1.13.1 tmc_initialise Initialise the library and setup callback functions. 3.1.13.2 tmc_class_req_capabilities Returns a response to a USB class request for the TMC capabilities (GET_CAPABILITIES).

-

Page 151: Usb Applications

Clearance No.: FTDI# 483 3.2 USB Applications An application which implements a USB device with the FTDI USB Library on the FT51A must include the following parts of the FT51A libraries: Include the ft51_interrupt.c file from the top-level of the library. This is required to implement the interrupt handler for the USB device. -

Page 152: Descriptors

The idVendor and idProduct values (the USB VID and PID) must be unique to the application. FTDI applications for the FT51A use the FTDI VID and an example PID. FTDI can assign a valid PID on request. FT51A applications assign PIDs in the range 0x0FE0 to 0x0FEF. - Page 153 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 __code struct config_descriptor USB_configuration_descriptor configuration; USB_interface_descriptor interface; USB_hid_descriptor hid; USB_endpoint_descriptor endpoint; struct config_descriptor config_descriptor = .configuration.bLength = 0x09, .configuration.bDescriptorType = USB_DESCRIPTOR_TYPE_CONFIGURATION, .configuration.wTotalLength = sizeof(struct config_descriptor_keyboard), .configuration.bNumInterfaces = 0x01,...

-

Page 154: Standard Requests

// END OF STRINGS 0x00 FTDI applications will place the string descriptors in a block of 256 bytes starting at offset 0x80 in the program code. This is achieved using the following code. // String descriptors - allow a maximum of 256 bytes for this... - Page 155 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 status = USB_set_configuration(req); break; case USB_REQUEST_CODE_GET_CONFIGURATION: status = USB_get_configuration(); break; case USB_REQUEST_CODE_SET_ADDRESS: status = USB_set_address(req); break; default: case USB_REQUEST_CODE_GET_INTERFACE: case USB_REQUEST_CODE_SET_INTERFACE: // Unknown or unsupported request.

- Page 156 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 USB_transfer(USB_EP_0, USB_DIR_IN, buf, 2); return FT51_OK; return FT51_FAILED; The endpoint status may only return a valid status for endpoint zero when the device is not configured.

- Page 157 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 A simple handler for device, configuration and string descriptors would be as follows. It is assumed that the byte arrays “config_descriptor”, “device_descriptor” and “string_descriptor” are defined.

-

Page 158: Class And Vendor Requests

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 3.2.4 Class and Vendor Requests Like the standard request handler, class and vendor request handlers must return FT51_OK if the request was handled by the application or FT51_FAILED if not. -

Page 159: Main Function

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Endpoint creation is best placed in this function, as the host will reset a USB device during enumeration. This allows us to disable and then re-enable an endpoint during a reset or when the device is first powered up. -

Page 160: Sending And Receiving Data

The USB Full Speed device controller is capable of acknowledging LPM transaction. Furthermore, the FT51A sees the link state change as an interrupt in the ISR. Below is an extract of an example ISR that can be used to detect a LPM state transition, plus a function that can be invoked whenever a LPM transition occurred. - Page 161 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 LPM_L1 = 1; // Set this bit to indicate LPM-triggered transition from L0 (Active) to L1 (Sleep). if (first_time) first_time = 0; FT122_CMD = READ_LPM_STATUS;...

-

Page 162: Contact Information

FTDI disclaims all liability for system designs and for any applications assistance provided by FTDI. Use of FTDI devices in life support and/or safety applications is entirely at the user’s risk, and the user agrees to defend, indemnify and hold harmless FTDI from any and all damages, claims, suits or expense resulting from such use. -

Page 163: Appendix A - References

AN_344 FT51A DFU Sample http://www.ftdichip.com/Support/Documents/AppNotes/AN_344_FT51A_DFU_Sample.pdf AN_345 FT51A Keyboard Sample http://www.ftdichip.com/Support/Documents/AppNotes/an_345_ft51a_keyboard_sample. AN_346 FT51A Mouse Sample http://www.ftdichip.com/Support/Documents/AppNotes/AN_346_FT51A_Mouse_Sample.p AN_347 FT51A Test and Measurement Sample http://www.ftdichip.com/Support/Documents/AppNotes/AN_347_FT51A_Test_and_Measur ement_Sample.pdf AN_348 FT51A FT800 Sensors Sample http://www.ftdichip.com/Support/Documents/AppNotes/AN_348_FT51A_FT800_Sensors_S ample.pdf AN_349 FT51A FT800 Spaced Invaders Sample http://www.ftdichip.com/Support/Documents/AppNotes/AN_349_FT51A_FT800_Spaced_In... -

Page 164: Acronyms And Abbreviations

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Acronyms and Abbreviations Terms Description Universal Serial Bus USB-IF USB Implementers Forum Multiple Time Program – non-volatile memory used to store program code on the FT51A. -

Page 165: Appendix B - List Of Tables & Figures

Clearance No.: FTDI# 483 Appendix B – List of Tables & Figures List of Tables Table 2.1 FT51A SFR Map ....................9 Table 2.2 FT51A Peripherals ....................10 Table 2.3 Register Bit Type Definitions ................. 11 Table 2.4 Device Control Register Addresses ................ 12 Table 2.5 Device Control Register .................. - Page 166 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Table 2.36 SPI Slave Register Addresses ................36 Table 2.37 SPI Slave Control Register .................. 37 Table 2.38 SPI Slave Transmit Register ................37 Table 2.39 SPI Slave Receive Register .................

- Page 167 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Table 2.75 IOMUX Control Register ..................63 Table 2.76 IOMUX Output Pad Select Register ..............64 Table 2.77 IOMUX Output Signal Select Register ..............64 Table 2.78 IOMUX Input Signal Select Register ..............

- Page 168 Table 2.146 PWM Initialisation Register ................111 Table 2.147 Programming 8 FT51A comparators to generate above waveform ......112 Table 2.148 Programming 2 FT51A comparators for 50 % duty cycle ........112 Table 2.149. PWM Ranges ....................113 Table 2.150 Timer Register Addresses ................116 Table 2.151 Timer Control Register ..................

-

Page 169: List Of Figures

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Table 2.153 Timer Control 2 Register ................. 117 Table 2.154 Timer Control 3 Register ................. 117 Table 2.155 Timer Control 3 Register ................. 118 Table 2.156 Timer Control 3 Register ................. - Page 170 Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Figure 2.7 Square wave with 50 % duty cycle..............107 Figure 2.8 Square wave with 20 % duty cycle..............108 Figure 2.9 Pulse Waveform generated by 8 comparators ............111 Figure 2.10 Timer range for uint32_t timer .................

-

Page 171: Appendix C - Revision History

Application Note AN_289 FT51A Programming Guide Version 1.0 Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Appendix C – Revision History Document Title: AN_289 FT51A Programming Guide Document Reference No.: FT_000962 Clearance No.: FTDI# 483 Product Page: http://www.ftdichip.com/FTProducts.htm Document Feedback:...

Need help?

Do you have a question about the FT51A and is the answer not in the manual?

Questions and answers