Summary of Contents for Artison Astronics Talon Instruments T940 64-Channel Digital Resource Module

- Page 1 sales@artisantg.com artisantg.com (217) 352-9330 | Visit our website - Click HERE...

- Page 2 Talon Instruments™ Model T940 64-Channel Digital Resource Module User Manual Publication No. 980938 Rev. K Astronics Test Systems Inc. 4 Goodyear, Irvine, CA 92618 Tel: (800) 722-2528, (949) 859-8999; Fax: (949) 859-7139 atsinfo@astronics.com atssales@astronics.com atshelpdesk@astronics.com http://www.astronicstestsystems.com Copyright 2009 by Astronics Test Systems Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

- Page 3 THANK YOU FOR PURCHASING THIS ASTRONICS TEST SYSTEMS PRODUCT For this product, or any other Astronics Test Systems product that incorporates software drivers, you may access our web site to verify and/or download the latest driver versions. The web address for driver downloads is: http://www.astronicstestsystems.com/support/downloads If you have any questions about software driver downloads or our privacy policy, please contact...

- Page 4 RETURN OF PRODUCT Authorization is required from Astronics Test Systems before you send us your product or sub-assembly for service or calibration. Call or contact Customer Support at 1-800-722-3262 or 1-949-859-8999 or via fax at 1-949-859-7139. We can also be reached at: atshelpdesk@astronics.com. If the original packing material is unavailable, ship the product or sub-assembly in an ESD shielding bag and use appropriate packing materials to surround and protect the product.

- Page 5 FOR YOUR SAFETY Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the WARNINGS and CAUTION notices. This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury. If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

-

Page 6: Table Of Contents

Publication No. 980938 Rev. K Model T940 User Manual Table of Contents Chapter 1 ........................1-1 Introduction ........................1-1 Overview and Features........................1-1 Driver/Receiver Board Options ....................1-4 Utility Resource (UR) Option ...................... 1-6 Basic Elements of the DRM System ....................1-6 Front Panel .......................... - Page 7 Model T940 User Manual Publication No. 980938 Rev. K LBUS Lockout Key Installation ....................3-5 Chapter 4 ......................... 4-1 Functional Description ....................4-1 Digital Board (DB) .......................... 4-1 VXI Bridge ..........................4-2 Terms Used in this Section ....................4-2 Description ..........................4-2 Power Converter ........................

- Page 8 Publication No. 980938 Rev. K Model T940 User Manual SFP Main Panel Menu Bar ......................5-5 File Menu ..........................5-5 Config Menu ........................... 5-6 Edit Menu ..........................5-7 Execute Menu ......................... 5-7 Instrument Menu ........................5-8 Help Menu ..........................5-8 Opening a VXI DRM Session ......................

- Page 9 Model T940 User Manual Publication No. 980938 Rev. K Synthesizer Freq (MHz) ....................5-27 Synthesizer Ref Source ....................5-27 Reference Freq (MHz) ..................... 5-27 Configure Timers ........................5-28 Watchdog Action ......................5-29 Watchdog Time ........................ 5-30 Sequence Timeout State ....................5-30 Sequence Timeout Time ....................

- Page 10 Publication No. 980938 Rev. K Model T940 User Manual Probe Button Level ......................5-47 Probe Input Connect ...................... 5-47 Probe Input Compare High and Low ................5-47 Probe Cal Connect ......................5-48 Probe Cal Signal ......................5-48 Probe Output Connect ....................5-48 Compensation ........................

- Page 11 Model T940 User Manual Publication No. 980938 Rev. K Input Bus Source ........................5-70 Connect State........................5-71 Properties (Programmable Logic) ..................5-71 ECL Mode (ECL Differential or Bipolar Logic) ..............5-71 Logic Mode (LVTTL/Bipolar ECL Logic) ................5-71 Configuring the Interrupts ......................5-72 Condition ..........................

- Page 12 Publication No. 980938 Rev. K Model T940 User Manual Mask ..........................5-98 Editing Sequence Steps ......................5-99 Internal T0CLK ........................5-100 Clocks per Pattern ......................5-100 CPP Phase and Window Triggering ................... 5-101 Timing Set ........................... 5-101 Last Step ..........................5-102 Sequence Timeout......................

- Page 13 Model T940 User Manual Publication No. 980938 Rev. K Execute Panel Modes and Settings ..................5-117 Start/Arm Selector ......................5-117 Channel Drivers........................5-118 V+/ V- ..........................5-118 Execute Idle Step ....................... 5-118 Execute Step ........................5-119 Burst ........................... 5-119 Halt Mode ........................... 5-119 Finish Mode ........................

- Page 14 Publication No. 980938 Rev. K Model T940 User Manual Error Address Display ......................5-132 Record Index Display......................5-133 Record Data Display ......................5-134 Probe Data Memory Display ....................5-135 Status Indicator Panels ......................5-139 Sequencer Events ......................5-139 Enable ..........................5-142 Condition .........................

- Page 15 Model T940 User Manual Publication No. 980938 Rev. K Serial Number ........................5-161 Start Chan.......................... 5-161 Meas. Delay ........................5-161 End Channel........................5-162 Run ............................. 5-162 Verify ..........................5-163 Export ..........................5-166 Stop ............................ 5-166 Update ..........................5-166 Monitor Temperature Panel ....................5-166 Trip Temperature .......................

- Page 16 Publication No. 980938 Rev. K Model T940 User Manual Basic Setup ............................. 6-3 Calibration Interval .......................... 6-3 Calibration Temperature ......................... 6-3 Calibration Procedures ........................6-4 ADC Reference (via EXTERNAL FORCE) ................. 6-5 Select Calibrate Function ....................... 6-5 Select Measurement Delay ....................6-6 Run Calibration ........................

- Page 17 Model T940 User Manual Publication No. 980938 Rev. K Stimulus/Capture Characteristics ....................7-3 Recording Mode Characteristics ....................7-4 Sequencer Characteristics ......................7-5 Master Clock (MCLK) ........................7-7 Counter/Timer Characteristics ....................... 7-8 Pulse Generator Characteristics ....................7-9 Calibration ............................7-9 Front Panel I/O ..........................7-10 VXI Interface ..........................

- Page 18 Publication No. 980938 Rev. K Model T940 User Manual Advanced Operation Examples: ....................8-43 Notes: ............................8-44 Appendix A ........................A-1 Glossary of Terms and Acronyms ................A-1 Appendix B ........................B-1 DR1 Driver/Receiver Board .................... B-1 DR1 Features ..........................B-1 Front Panel Connectors .........................

- Page 19 Model T940 User Manual Publication No. 980938 Rev. K DRB I/O Channels (J201) ....................... C-10 PWR Connector ........................C-12 Calibration ........................... C-13 Appendix D ........................D-1 DR3e Driver/Receiver Board ..................D-1 DR3e Features ..........................D-1 Front Panel Connectors .........................D-1 Block Diagram ..........................D-1 Auxiliary Driver &...

- Page 20 Publication No. 980938 Rev. K Model T940 User Manual Appendix F ........................F-1 DR7 Driver/Receiver Board .................... F-1 DR7 Features ..........................F-1 Front Panel Connectors ......................... F-1 Block Diagram ..........................F-1 Auxiliary Driver & Receiver I/O ....................F-2 Signal Descriptions ........................ F-3 DR7 Driver &...

- Page 21 Model T940 User Manual Publication No. 980938 Rev. K Appendix H ........................H-1 DR9 Driver/Receiver Board ................... H-1 DR9 Features ..........................H-1 Front Panel Connectors .........................H-1 Block Diagram ..........................H-3 Auxiliary Driver & Receiver I/O ....................H-4 Signal Descriptions ........................H-4 DR9 Driver & Receiver I/O ......................H-4 Signal Descriptions ........................H-5 Control Logic ..........................H-6 Signal Descriptions ........................H-7...

- Page 22 Publication No. 980938 Rev. K Model T940 User Manual External Probe Module ......................I-19 UR14 Characteristics ........................I-20 UTILITY CHANNELS ......................... I-20 PROGRAMMABLE CHANNELS ....................I-21 Programmable AUX I/O Min/Max Levels ................I-23 ADC_IN............................I-24 PROBE SUPPORT ........................I-24 PROBE MODULE CHARACTERISTICS .................. I-24 Auxiliary I/O Channels .......................

- Page 23 Model T940 User Manual Publication No. 980938 Rev. K This page was left intentionally blank. xviii Astronics Test Systems...

- Page 24 Publication No. 980938 Rev. K Model T940 User Manual List of Figures Figure 1-1: Example DRM with Two Driver/Receiver Boards (DRA and DRB) ........ 1-7 Figure 1-2: DRM Digital Resource Module Block Diagram ............... 1-8 Figure 1-3: T940 Optional Front Panel PWR Connector ..............1-8 Figure 2-1: T940 with Two DR7 Boards Installed ................

- Page 25 Model T940 User Manual Publication No. 980938 Rev. K Figure 5-21: Configure Clocks ......................5-25 Figure 5-22: Configure Timers ......................5-28 Figure 5-23: Configure Triggers Panel .................... 5-31 Figure 5-24: Configure Pulse Generator ..................5-35 Figure 5-25: Data Sequencer Configure Settings Panel ..............5-38 Figure 5-26: Over-Current Panel ....................

- Page 26 Publication No. 980938 Rev. K Model T940 User Manual Figure 5-65: Execute DSA View Menu ..................5-125 Figure 5-66: Static Data Panel ...................... 5-126 Figure 5-67: Kept Data Panel ......................5-128 Figure 5-68: View Results Data Panel................... 5-129 Figure 5-69: View CRC Panel ....................... 5-131 Figure 5-70: View Errors Address Panel ..................

- Page 27 Model T940 User Manual Publication No. 980938 Rev. K Figure 5-109: SFP Reset Message ....................5-176 Figure 6-1: Invoke the Calibrate DRM Panel from the SFP .............. 6-4 Figure 6-2: T940-DR3e-DR3e Connection Diagram ................. 6-7 Figure 6-3: T940-DR9-DR9 or T940-UR14 Connection Diagram ............. 6-7 Figure 6-4: T940-DR3e-DR3e Connection Diagram ...............

- Page 28 Publication No. 980938 Rev. K Model T940 User Manual Figure E-5: J200 and J201 Connectors .................... E-9 Figure F-1: DR7 Driver/Receiver Block Diagram ................F-2 Figure F-2: Auxiliary Driver & Receiver I/O Block Diagram .............. F-3 Figure F-3: DR7 Driver & Receiver I/O Block Diagram ..............F-4 Figure F-4: J200 and J201 Connectors ....................

- Page 29 Model T940 User Manual Publication No. 980938 Rev. K This page was left intentionally blank. xxiv Astronics Test Systems...

- Page 30 Publication No. 980938 Rev. K Model T940 User Manual List of Tables Table 2-1: Logical Address Selection ....................2-3 Table 2-2: VXI Interrupt Selection ..................... 2-4 Table 2-3: A24/A32 Map Selection ....................2-4 Table 2-4: Debug Selection ....................... 2-5 Table 2-5: Mode Selection ......................... 2-5 Table 2-6: Bus Request Selection .....................

- Page 31 Model T940 User Manual Publication No. 980938 Rev. K Table 5-30: Trigger Test Condition Settings ................... 5-33 Table 5-31: Trigger Input Mode Settings ..................5-34 Table 5-32 Trigger Event Clear Settings ..................5-34 Table 5-33: Pulse Generator Mode Settings................... 5-36 Table 5-34: Error Record Basis Settings ..................

- Page 32 Publication No. 980938 Rev. K Model T940 User Manual Table 5-74: Binary Block Format ..................... 5-89 Table 5-75: Waveform Table Size Settings ..................5-92 Table 5-76: Vector Strobe Settings ....................5-94 Table 5-77: Vector Bit Source Settings ................... 5-96 Table 5-78: Vector Bit Input Mode Settings ..................5-96 Table 5-81: Jump Type Settings ....................

- Page 33 Model T940 User Manual Publication No. 980938 Rev. K Table 8-4: Cross-Reference of Step Record Mode to Error Count Basis ........8-12 Table 8-5: Cross-Reference of Step Record Mode to Error Address Basis ........8-12 Table 8-6: Cross-Reference of Step Record Mode to Pass Fail Basis ........... 8-16 Table 8-7: Truth Table Describing Pass and Fail ................

- Page 34 Publication No. 980938 Rev. K Model T940 User Manual Table G-1: DR8 Characteristics ......................G-5 Table G-2: DR8 Power Requirements ....................G-6 Table G-3: DR8, DRA I/O Channels (J200) ..................G-7 Table G-4: DR8 Pin out by Pin Number (DRA) ................G-8 Table G-5: DR8, DRB I/O Channels (J201) ..................

- Page 35 Model T940 User Manual Publication No. 980938 Rev. K DOCUMENT CHANGE HISTORY Revision Date Description of Change 10/6/2009 Document Control release EO: Added T940 variant and DR3e & DR7 boards. 1/18/2012 Updated software screens and specifications. 4/17/2012 ECN00132: Added information regarding DR9 option. ECN00901.

-

Page 36: Chapter 1

Publication No. 980938 Rev. K Model T940 User Manual Chapter 1 Introduction This manual provides information necessary to set up and operate the T940 64-Channel Digital Resource Modules (DRM). Throughout this manual, “DRM” is used to refer to the T940. Separate chapters and appendices include: •... - Page 37 Model T940 User Manual Publication No. 980938 Rev. K Advanced Features for Modern Digital Test Development The DRM is designed for today’s challenging digital test system applications through innovative design. The flexible Field Programmable Gate Array (FPGA) design enables the DRM to meet special user and legacy requirements. The high-speed Data Sequencer provides control over test patterns, timing, and format.

- Page 38 Publication No. 980938 Rev. K Model T940 User Manual independently or linked for timing, memory, and control of the two Driver/Receiver boards. Sequencer logic supports full unit under test (UUT) handshaking and controls timing, format, pattern data, looping, and conditional testing.

-

Page 39: Driver/Receiver Board Options

Model T940 User Manual Publication No. 980938 Rev. K fault dictionary and complex patterns and timing set(s). Migration Tools and Translators The optional Migration Tools and Translators support many legacy test systems from a variety of manufacturers. Test programs from supported systems are easily translated without extensive code rewriting. - Page 40 Publication No. 980938 Rev. K Model T940 User Manual • Over-voltage detection/protection • Auxiliary channels: Four variable voltage Four LVTTL Four ECL (single-ended or differential) DR4: Driver/Receiver The DR4 features: • Channels: 48 single-ended variable voltage or 24 differential channels •...

-

Page 41: Utility Resource (Ur) Option

Model T940 User Manual Publication No. 980938 Rev. K • Voltage range: -15 V to +24 V with an output swing of up to 24 V • Relay Isolation on all I/O channels. • Provides full drive current on all channels simultaneously •... -

Page 42: Front Panel

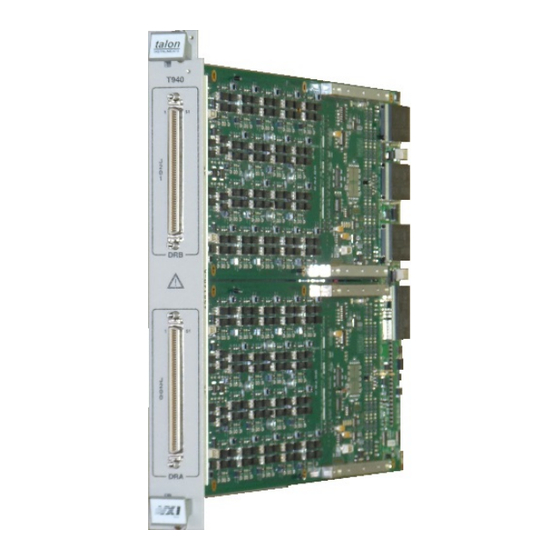

Publication No. 980938 Rev. K Model T940 User Manual Boards (named DRA and DRB for their mounted location). (A T940 module is shown in the photo as an example.) The block diagram in Figure 1-2 shows how the various components work together. -

Page 43: Figure 1-2: Drm Digital Resource Module Block Diagram

Model T940 User Manual Publication No. 980938 Rev. K FRONT POWER DIGITAL BOARD CONVERTER PANEL DRIVER/RECEIVER (OPTIONAL) DATA SEQUENCER BRIDGE INTER DATA MODULE CONTROL SEQUENCER DRIVER/RECEIVER Figure 1-2: DRM Digital Resource Module Block Diagram Front Panel The DRM front panel provides the interface to the device being tested. There is a Driver/Receiver board connector for input and output of signals. -

Page 44: Power Converter (Pc)

Publication No. 980938 Rev. K Model T940 User Manual Power Converter (PC) The PC may be optionally installed on the Digital Board when variable voltage DR boards such as the DR3e, DR9, or UR14 are used. The PC converts backplane voltages into digital bias voltages. Its protection circuitry can detect faults in any of the four on-board power supplies, status of the input fuses, or a high input current or overcurrent condition. -

Page 45: Driver/Receiver Board B (Drb)

Model T940 User Manual Publication No. 980938 Rev. K Driver/Receiver Board B (DRB) The DRB board contains all the driver/receiver logic, relays, sensors and termination circuitry for channels 33 through 64. Model and Part Number Information Model # Description Ordering Part # LVTTL, 32 channels, 100 Ω... - Page 46 Publication No. 980938 Rev. K Model T940 User Manual To create the 2nd, 3rd, and 4th sections of the part # for a configured T940, substitute the [W], “- XXzz,” “-YYzz,” and [-A] in the part # with the correct CIB/Funnel, Application and Power Converter Code from the table below.

-

Page 47: Accessories

Model T940 User Manual Publication No. 980938 Rev. K Accessories Model # Description Ordering Part # Front Panel Signal Flat Ribbon Cable T940/300-XXX 408123-XXX (1 per Driver/Receiver Board) Front Panel Signal Flat Shielded Cable T940/302-XXX 408122-XXX (1 per Driver/Receiver Board) Coaxial Cable, 22 positions, Auxiliary I/O from T940/303-001 408124-001... -

Page 48: Chapter 2

Publication No. 980938 Rev. K Model T940 User Manual Chapter 2 Installation The following sections discuss the installation procedure for the DRM module into a VXI chassis. Before installing the DRM module, ensure that the digital board (DB) DIP switches are set to correct settings for your setup – either in the factory default mode or with specific address and mode settings to your test situation. -

Page 49: Initial Digital Board (Db) Switch Setting

Model T940 User Manual Publication No. 980938 Rev. K Figure 2-2: T940 with Two DR3e Boards Installed Initial Digital Board (DB) Switch Setting WARNING Use standard ESD procedures including ground straps and static-safe work surfaces whenever handling the DRM or any of its Driver/Receiver boards. -

Page 50: Logical Address Selection

Publication No. 980938 Rev. K Model T940 User Manual Do not adjust SW3 VXI Connector VXI Connector Figure 2-3: Digital Board (DB) Switch Locations CAUTION Switch settings shown in Figure 2-2 are for example only and are not particularly what your board should be set to. Refer to the text for proper switch settings. -

Page 51: Vxi Interrupt Selection

Model T940 User Manual Publication No. 980938 Rev. K address. The “ON” setting sets the corresponding bit of the logical address to a one (1). VXI Interrupt Selection The VXI backplane supports 7 levels of interrupts. Using the Slot 0 API functions, interrupt handlers can be installed and enabled for each interrupt level. -

Page 52: Other Settings

Publication No. 980938 Rev. K Model T940 User Manual A32/A24 Register Mapping A32 (factory default) ATTENTION GPIB-VXI slot zero controllers do not support A32 register transfers. A24 register mapping must be selected for DRM operation with these controllers. Other Settings There are a few switch settings that are used for development or debug which, under normal operation, should not be changed. -

Page 53: Bus Request Selection

Model T940 User Manual Publication No. 980938 Rev. K MODE Message Based Enabled VXI Message Based VXI Register Based (Default) Bus Request Selection The VXI backplane supports 4 levels of bus request. Switch positions 2 and 1 of SW2 are used to select the VXI bus request level. Table 2-6: Bus Request Selection Position Signal... -

Page 54: Installing The Module Into A Vxi Chassis

Publication No. 980938 Rev. K Model T940 User Manual Note: Jumper above is shown in the “Terminator” position. Figure 2-4: T940 Inter-Module Mode Jumper Connector Location Terminator Position Secondary Position Primary Position Note: The gray areas in the figure indicate the open portions of the connector. Figure 2-5: T940 Inter-Module Mode Jumper Positions and Settings Installing the Module into a VXI Chassis WARNING... -

Page 55: Figure 2-6: Installing The Drm Into A Chassis

Model T940 User Manual Publication No. 980938 Rev. K ATTENTION Be sure that the VXI chassis has sufficient power and cooling capability – particularly if multiple DR3e, DR4, or DR9 modules are installed into the same chassis. The DRM may be installed in any VXI chassis slot except slot 0 (zero), which is reserved for the Resource Manager. -

Page 56: Figure 2-7: 1263 Series Vxi Chassis (1263Hpf Top, 1263Hpr Bottom)

Publication No. 980938 Rev. K Model T940 User Manual Figure 2-7: 1263 Series VXI Chassis (1263HPf top, 1263HPr bottom) The optional Racal Instruments 1263 High Power 13-slot VXI chassis series (Figure 2-7) is recommended for multiple DRMs which are populated with multiple DR3e, DR4 or DR9 modules. -

Page 57: Initial Power-On

Model T940 User Manual Publication No. 980938 Rev. K Initial Power-On The DRM is normally a register-based VXI module with an embedded processor to manage standard VXI communications. 1. Turn off the chassis power before installing the DRM. 2. Once the DRM is properly installed in a VXI chassis, turn on the chassis power. -

Page 58: Installing The Instrument Driver

Publication No. 980938 Rev. K Model T940 User Manual Included with the instrument driver is the Soft Front Panel (SFP) software. The soft front panel is a graphical user interface for the DRM. It can be used to verify communications and to debug applications during development and integration. The DRM VXIplug&play Instrument Driver uses the VISA communication library to operate the instrument. - Page 59 Model T940 User Manual Publication No. 980938 Rev. K This page was left intentionally blank. Installation 2-12 Astronics Test Systems...

-

Page 60: Chapter 3

Publication No. 980938 Rev. K Model T940 User Manual Chapter 3 DRM Front Panel The DRM front panel provides the hardware interface to the unit under test (UUT). Figures 3-1 and 3-2 illustrate the front panel and its connectors. DRB Channel (J201) T940 shown with two Driver/Receiver boards... -

Page 61: J200 And J201 Dra Channel I/O

Model T940 User Manual Publication No. 980938 Rev. K DRB Channel (J201) DRA/DRB Power and Multi- T940 shown with two Function Signals Driver/Receiver boards on this optional installed (DRA and DRB). connector DRA Channel (J200) Figure 3-2: T940 Front Panel (Showing Optional Front Power Connector) J200 and J201 DRA Channel I/O The J200 and J201 connectors’... -

Page 62: Front Panel Connectors

Publication No. 980938 Rev. K Model T940 User Manual multi-function signals (MFSIG) and grounds to all boards. Figure 3-3: PWR Connector Table 3-1: PWR Connector Pinout Connector Name Connector Name DRB V+ DRB V- DRB MFSIG DRA MFSIG DRA V+ DRA GND DRB GND DRA V-... -

Page 63: Front Panel Lbus Lockout Keys

Model T940 User Manual Publication No. 980938 Rev. K J200/J201 flat ribbon mating cable. 2. DRM cable assemblies are open at one end. Front Panel LBUS Lockout Keys The VXIbus-defined LBUS Lockout Keys are designed to prevent adjacent VXI Modules with incompatible logic families from connecting to the Local Bus. -

Page 64: Lbus Lockout Key Installation

Publication No. 980938 Rev. K Model T940 User Manual Figure 3-5: LBUS Lockout Configuration LBUS Lockout Key Installation In order to accommodate the VXIbus specification’s defined minimum thickness of the lockout key and the clearance provided around the module ejector handle, two LBUS lockout keys must be fitted on top of each other for each module. - Page 65 Model T940 User Manual Publication No. 980938 Rev. K 2. Install two screws in the holes at the top of the module front panel and tighten the screws. 3. Move the ejector handle to the ejected position, and install a third screw in the hole now made accessible.

-

Page 66: Chapter 4

Publication No. 980938 Rev. K Model T940 User Manual Chapter 4 Functional Description This section describes the DRM hardware block diagrams. For information about DRM address maps and register descriptions, contact your local sales representative or contact Sales Support at atsinfo@astronics.com. Digital Board (DB) FRONT CH[1:32]... -

Page 67: Vxi Bridge

Model T940 User Manual Publication No. 980938 Rev. K VXI Bridge TEMPERATURE MONITOR EEPROM VADDR VDATA ADDRESS CONTROL VCTRL SERIAL PROM JTAG ARBITRATION REGISTERS VXI_INT VXI TRIGGERS TTL/ECL Data Sequencer Logic Driver Receiver Logic Figure 4-2: T940 VXI Bridge Block Diagram Terms Used in this Section VADDR (VXI Address Bus) The 32 bit backplane address bus... -

Page 68: Type 1 And Type 3

Publication No. 980938 Rev. K Model T940 User Manual headroom requirements and specifications for each power converter range. Type 1 and Type 3 The type 1 power converter is designed for use in a VXI 3.0 chassis and the type 3 power converter is designed for a VXI 4.0 chassis and utilizes the additional power pins and can supply more current. -

Page 69: Terms Used In This Section

Model T940 User Manual Publication No. 980938 Rev. K LBUSC LBUSA LBUSC LBUSA LBUSC LBUSA LBUSC LBUSA Slot 1 Slot 2 Slot 3 Slot 4 Slot 12 INTER INTER INTER INTER INTER MODULE MODULE MODULE MODULE MODULE CONTROL CONTROL CONTROL CONTROL CONTROL Inter-Module Control... -

Page 70: Description

Publication No. 980938 Rev. K Model T940 User Manual Linked Used to describe two sequencers (DSA and DSB) on the same DRM that are synchronized together. Primary Used to describe the DRM that provides all the timing for the sequencers that are part of the DRS chain. DSA is always coupled to the DRS chain and is the source of the timing and control. - Page 71 Model T940 User Manual Publication No. 980938 Rev. K Primary DRM Inter-Module Modes: These modes apply to a DRM that is jumpered as a Primary. • Independent Not Linked – SIMA set to IMA and SIMB set to IMB. IMJMPR position is a don’t care.

-

Page 72: Examples

Publication No. 980938 Rev. K Model T940 User Manual position is a don’t care. Primary driver disabled. The DRM is not coupled to a DRS. DSA and DSB are not linked. • Independent Linked – SIMA and SIMB set to IMA. IMJMPR position is a don’t care. - Page 73 Model T940 User Manual Publication No. 980938 Rev. K COUPLED DRM5 DRM3 DRM1 DRM6 DRM4 DRM2 LINKED CH 321-384 CH 257-320 CH 193-256 CH 129-192 CH 65-128 CH 1-64 In this example, all 12 sequencers, DSA and DSB on DRM1 through DRM6 are coupled to a single DRS (368 channels).

- Page 74 Publication No. 980938 Rev. K Model T940 User Manual COUPLED DRM5 DRM3 DRM1 DRM6 DRM4 DRM2 LINKED CH 321-384 CH 257-320 CH 193-256 CH 129-192 CH 65-128 CH 1-64 In this example, DSA and DSB on DRM1 and DRM2 are coupled to a DRS (128 channels).

-

Page 75: Data Sequencer

Model T940 User Manual Publication No. 980938 Rev. K COUPLED DRM5 DRM3 DRM1 DRM6 DRM4 DRM2 LINKED CH 321-384 CH 257-320 CH 193-256 CH 129-192 CH 65-128 CH 1-64 In this example, DSA and DSB on DRM1 and DRM2 are coupled to a DRS (128 channels), DSA and DSB on DRM3 and DRM4 are coupled to a second DRS (128 channels), DSA and DSB on DRM5 are linked and running independent of a DRS (64 channels). -

Page 76: Terms Used In This Section

Publication No. 980938 Rev. K Model T940 User Manual Terms Used in this Section 250 MHz 250 MHz clock derived from the 500 MHz clock. 500 MHz 500 MHz oscillator clock. AUX DATA AUX output data value. AUX EN AUX output enable value. AUX I/O AUX output and enable signals as well as the AUX input and probe data. - Page 77 Model T940 User Manual Publication No. 980938 Rev. K Linked Trigger Bus signals connecting DSA to DSB. MCLK Master Clock MPSIG Multipurpose signal output. PAT DEL[1:2] Pattern delay timers. PAT TO Pattern timeout timer. PATADDR Pattern address used by the external pattern RAM. PAUSE Sequence trigger used to stop the timing generator for handshaking applications.

-

Page 78: Sequence Logic

Publication No. 980938 Rev. K Model T940 User Manual Jump 4 Selected Inter-Module signals. START Sequence trigger used to start the pattern controller. STOP Sequence trigger used to stop the pattern controller. SYNC[1:2] Programmable sync pulse signals. TEST CODE Selects the jump test event. T0 CLK Internal SEQ CLK generated by the sequence controller. -

Page 79: System Clock

Model T940 User Manual Publication No. 980938 Rev. K System Clock This block selects the sequence clock signal used by the sequence controller. Test Logic This block determines if a valid conditional jump is enabled or not. Record Control This block generates the address for the Record RAM based on the Recording Mode. -

Page 80: Pattern Ram

Publication No. 980938 Rev. K Model T940 User Manual Pattern RAM The output code as well as the input code for every channel of each pattern is stored in the Pattern RAM. Record RAM This is where the individual channel results are stored. The channel results are either the pattern input compare result or raw response data based on RH or RL. -

Page 81: Driver/Receiver

Model T940 User Manual Publication No. 980938 Rev. K Driver/Receiver The DRM can accommodate two Driver/Receiver boards (named DRA or DRB for their mounted location). Each Driver/Receiver board contains unique driver/receiver circuitry and front panel connector pinouts that are described in an appendix dedicated to each specific Driver/Receiver type. -

Page 82: Chapter 5

Publication No. 980938 Rev. K Model T940 User Manual Chapter 5 Soft Front Panel Operation The Soft Front Panel (SFP) is a stand-alone executable that can be used to program, query and run the DRM digital resource. Regardless of the user’s choice of programming path (VXIplug&play instrument driver, A24/A32 register-based access, or a combination of these) the following basic 7-step process is required to implement a DRM test program: 1. -

Page 83: Sfp Main Panel

Model T940 User Manual Publication No. 980938 Rev. K When started, the SFP searches for all the installed DRMs in the VXI system. If more than one DRM is detected, a dialog box prompts the user to select the DRM to initialize. Each instance of the SFP opens a VXI session with a single DRM in the system. -

Page 84: Figure 5-3: Main Panel

Publication No. 980938 Rev. K Model T940 User Manual Title Menu Company Chassis Logo Data Active Module Module Data Data Figure 5-3: Main Panel Figure 5-4: Main Panel UR14 Astronics Test Systems Soft Front Panel Operation 5-3... -

Page 85: Company Logo

Model T940 User Manual Publication No. 980938 Rev. K The following sections describe the main panel controls and indicators. Company Logo Pressing this control displays the information panel. Figure 5-5: Company Information Panel Active LED The Active LED indicates whether a VXI session has been established successfully. -

Page 86: Sfp Main Panel Menu Bar

Publication No. 980938 Rev. K Model T940 User Manual SFP Main Panel Menu Bar The SFP main panel menu bar provides access to select, program and save the DRM hardware. Relevant VXIplug&play API functions are included with the menu options. Figure 5-6: Menu Bar File Menu Figure 5-7: File Menu... -

Page 87: Config Menu

Model T940 User Manual Publication No. 980938 Rev. K Menu Option Description and inserted in the history list [tat964_loadConfiguration] Save Updates the configuration file with the latest editing changes [tat964_saveConfiguration] Save As Creates a new configuration file with the latest editing changes. -

Page 88: Edit Menu

Publication No. 980938 Rev. K Model T940 User Manual AUX Outputs Displays the panel for programming auxiliary output parameters Interrupts Displays the panel for programming the interrupt parameters Edit Menu The Edit Menu is used to create, program and modify timing sets, pattern sets and sequences. -

Page 89: Instrument Menu

Model T940 User Manual Publication No. 980938 Rev. K Instrument Menu The Instrument Menu is used to run self-test, calibration and monitor routines on the DRM hardware. Figure 5-11: Instrument Menu Table 5-5: Instrument Menu Descriptions Menu Option Description Self-Test Runs the self-test Full RAM Test Runs the full RAM test... -

Page 90: Opening A Vxi Drm Session

Publication No. 980938 Rev. K Model T940 User Manual Table 5-6: Help Menu Descriptions Menu Option Description Contents Displays the VXIPNP API help file table of contents About DRM Displays revision data for the DRM Soft Front Panel executable Figure 5-13: About DRM Driver Screen Opening a VXI DRM Session Starting the SFP initiates a search for all DRMs using the VISA library. -

Page 91: Configuring The Global Hardware Parameters

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-14: Opening a VXI DRM Session Relevant VXIplug&play API functions include: • tat964_init • tat964_autoConnectToAll • tat964_autoConnectToFirst • tat964_autoConnectToLA • tat964_autoConnectToSlot Configuring the Global Hardware Parameters Configuring the global hardware parameters is done from three panels: Configure Module, Configure Data Sequencer A, and Configure Data Sequencer B. -

Page 92: Inter-Module Mode

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-15: Configure Module Panel The following sections describe the Configure Module panel controls. Inter-Module Mode This pull-down control programs the control source for the DSA and DSB sequencers. The T940 chain and termination are set via jumpers. If a jumper is not installed, the DRM can only be configured as Independent Not Linked or Independent Linked. -

Page 93: Table 5-8: Inter-Module Mode Settings

Model T940 User Manual Publication No. 980938 Rev. K DRM Type Description Primary The Primary module must be located in the rightmost slot position in the VXI chassis relative to the DRM modules that will be coupled. DSA provides all the timing for the sequencers that are part of the coupled chain . -

Page 94: Power Converter

Publication No. 980938 Rev. K Model T940 User Manual Setting DSA Control DSB Control DRM Type Secondary DSB Coupled Secondary Secondary DSA and DSB Secondary Coupled Terminator Not Linked Terminator Terminator Linked Terminator Terminator DSA Coupled Terminator Terminator DSB Coupled Terminator Terminator DSA and DSB Terminator... -

Page 95: Ltbn Signal

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-16: Configure Linked Trigger Bus Panel LTBn Signal This pull-down control programs the signal source for the specified LTB trigger. The selections for this pull-down control are: Table 5-10: LTB Signal Pull-Down Settings Setting Description None... -

Page 96: Invert

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API function is: • tat964_setLtbTriggers Invert This Invert button is used to invert the associated signal. The relevant VXIplug&play API function is: • tat964_setLtbTriggers Direction The direction pull-down sets the signal direction. Table 5-11: Direction Settings Setting Description... -

Page 97: Offset

Model T940 User Manual Publication No. 980938 Rev. K Offset The group offset specifies the operating voltage window of the group channels. The selections for this pull-down control are: Table 5-12: Group Offset Attribute Settings Setting Description Zero HV -15.5V to 15.5V 0V to +31V -31V to 0V Verify that the Min and Max settings are within the window before updating. -

Page 98: Oc Src

Publication No. 980938 Rev. K Model T940 User Manual Table 5-13: Group Slew Attribute Settings Setting Description Fast Fast recommended for low voltage swings and fast data rates. Medium Slow Slow Default Low recommended for high voltage swings and low data rates. The slew attribute is updated immediately when changed. -

Page 99: Group [1

Model T940 User Manual Publication No. 980938 Rev. K Group [1..3] These toggle buttons turn the group state on or off. The relevant VXIplug&play API function is: • tat964_setGroupState Delay Signal The DRM uses the VXI local bus signal to function in a multi-module operation. During the alignment process, the local bus signals need to be delayed in order to align the timing skew between modules. -

Page 100: Ttltrg And Ecltrg Signal

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-18: Set VXI Triggers DSA Panel The TTLTRG lines are open collector on the VXI backplane. The chassis provides a split termination which provides a weak pull-up (thus there is a slow rising edge recovery time). -

Page 101: Invert

Model T940 User Manual Publication No. 980938 Rev. K Setting Description of the VXI Trigger Source Signal AUX1-AUX12 Selects the specified AUX input signal from the front panel Halted Used for DRS halt operation between coupled sequencers Probe Button Selects the state of the probe button Pulse Generator Selects the pulse generator signal Sequence Flag 1-2... -

Page 102: Dut_Gnd

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-19: Configure DSn D/R Properties Panel DUT_GND For the DR3e/DR4/DR9/UR14, this control is used to program a relay that will connect the DUT_GND reference for the Pin Electronics to either a front panel DUT_GND or to signal ground. -

Page 103: Mfsig Source

Model T940 User Manual Publication No. 980938 Rev. K The relevant VXIplug&play API function is: • tat964_setVoltageRangeMode Note: This function is inoperable for the DR1, DR2, DR4, DR7, and DR8. MFSIG Source This pull-down control programs the power connector MFSIG signal function. The DR3e Driver/Receiver boards have an optional front panel power connector that is used to provide the V+/V- rail voltages to the Pin Electronics devices. -

Page 104: Error Pulse Width

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API function is: • tat964_setMpsigSource Error Pulse Width This pull-down programs the error signal pulse width. The error pulse is a DRS signal used for counting and recording errors. The error pulse width is set during the DRS timing bus calibration with the Rev J driver or later and sequencer revision 0.20 or later. -

Page 105: Config Data Sequencer A/B

Model T940 User Manual Publication No. 980938 Rev. K Table 5-20: Record Mode Settings Setting Description Typical Usage Disabled The contents of the record memory will not Setting Record Mode to Disabled change during the next burst if Step Record insures that the record memory will not Mode is set to either None or Record be written to when Step Record Mode is... -

Page 106: Master Clock

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-21: Configure Clocks Master Clock This pull-down control programs the sequencer master clock source. The master clock defines the sequencer timing resolution. The resolution is half of the master clock period. The selections for this pull-down control are: Table 5-21: Master Clock Source Settings Setting... -

Page 107: System Clock

Model T940 User Manual Publication No. 980938 Rev. K System Clock This pull-down control programs the sequencer System Clock source. The System Clock signal defines the pattern period. The selections for this pull-down control are: Table 5-22: System Clock Source Settings Setting Description Typical Usage... -

Page 108: External Offset

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API function is: • tat964_setSystemClockParameters External Offset This control is used to specify the external System Clock offset in order to align the clock/data relationship. The valid offset range is from 0 to 65534 (even numbers only) and the resolution is 1/2 the MCLK period. -

Page 109: Configure Timers

Model T940 User Manual Publication No. 980938 Rev. K Configure Timers Access this panel from the menu bar: Config > Data Sequencer x> Timers. (Where “x” is the sequencer you wish to configure.). The DRM has five timers: • Watchdog •... -

Page 110: Watchdog Action

Publication No. 980938 Rev. K Model T940 User Manual • The timer is reset at the beginning of every step unless the sequence timeout continue flag is set in the Edit Sequence Step panel. • Cannot be nested. • Does not stop during a Pause or Halt (including single-stepping). •... -

Page 111: Watchdog Time

Model T940 User Manual Publication No. 980938 Rev. K • tat964_setWatchdogTimer Watchdog Time This numeric control is used to specify the watchdog timeout count. The timeout is programmed in 20 ns steps with a range of 40 ns to 4000 s. The watchdog timer set resolution adjusts based on the timeout value: Table 5-26: Watchdog Timer Resolution Ranges Timer Setting... -

Page 112: Pattern Delay 1-2

Publication No. 980938 Rev. K Model T940 User Manual • tat964_setPatternTimer Pattern Delay 1-2 This numeric control is used to specify the pattern delay. The pattern delay is programmed in 10 ns steps with a range of 20 ns to 42.949672970 s. -

Page 113: Trigger

Model T940 User Manual Publication No. 980938 Rev. K Execute Start Trigger The execute start trigger causes the selected sequence step to start. Selecting a sequence step consists of arming the sequence step. In a linked or DRS configuration, all of the coupled sequencers need to be armed first. -

Page 114: Test Condition

Publication No. 980938 Rev. K Model T940 User Manual The selections for this pull-down control are: Table 5-29: Trigger Source Settings Setting Description None No trigger source selected AUX1-AUX12 Trigger source set to front panel signal CHT1 Trigger source set to channel test 1 ECLTRG0,1 Trigger source set to VXI ECL trigger... -

Page 115: Input Mode

Model T940 User Manual Publication No. 980938 Rev. K • tat964_setPhaseResumeTrigger • tat964_setJumpTrigger • tat964_setHaltTrigger • tat964_setExecuteStartTrigger • tat964_setExecuteStopTrigger Input Mode This pull-down control programs the trigger input mode. The selections for this pull-down control are: Table 5-31: Trigger Input Mode Settings Setting Description Normal... -

Page 116: Configure Pulse Generator

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API functions are: • tat964_setPauseTriggerReset • tat964_setHaltTriggerReset • tat964_setJumpTriggerReset Configure Pulse Generator Access this panel from the menu bar: Config > Data Sequencer x> Pulse Generator (where “x” is the sequencer you wish to configure). Figure 5-24: Configure Pulse Generator Each data sequencer has a programmable pulse generator that can be routed to the following signals:... -

Page 117: Step

Model T940 User Manual Publication No. 980938 Rev. K The selections for this pull-down control are: Table 5-33: Pulse Generator Mode Settings Setting Description Continuous The pulse generator begins continuous output when armed Continuous Start The pulse generator begins continuous output from the start of the sequence when armed Single Start The pulse generator outputs a single pulse... -

Page 118: Width

Publication No. 980938 Rev. K Model T940 User Manual If the resolution is 10 ns, the delay is programmed in 10 ns steps with a range of 20 ns to 42.949672970 s (with an uncertainty of ±5 ns). If the resolution is 20 ns, the delay is programmed in 20 ns steps with a range of 20 ns to 85.899345920 s (with an uncertainty of ±5 ns). -

Page 119: Error Record Basis

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-25: Data Sequencer Configure Settings Panel Error Record Basis This pull-down control programs the sequencer error record basis. This control allows the user to select how the response data will be evaluated for errors when the record mode is set to Record Errors. -

Page 120: Record Type

Publication No. 980938 Rev. K Model T940 User Manual delay. See the Record Offset section in Chapter 8 for more details about using this feature. The valid offset range is from 0 to 63 MCLKs. The relevant VXIplug&play API function is: •... -

Page 121: Error Address Basis

Model T940 User Manual Publication No. 980938 Rev. K Counting and Logging Errors section in Chapter 8 including data rate limitations. The relevant VXIplug&play API function is: • tat964_setErrorParameters Error Address Basis This pull-down control programs the sequencer error address basis. This control allows the user to select which error signal causes an error to be recorded in the Error Address Memory. -

Page 122: Output-To-Input Disable

Publication No. 980938 Rev. K Model T940 User Manual Indexed 4096 sequence steps with 256 timing sets indexed. Four phase/window signals per timing set. The relevant VXIplug&play API function is: • tat964_setTimingMode Output-to-Input Disable This pull-down control programs the output-to-input disable setting. When a channel transitions from an output pattern code to an input pattern code, this enable can be set to disable the output at the beginning of the pattern (System Clock) or on a phase assert. -

Page 123: Pass Valid Mode

Model T940 User Manual Publication No. 980938 Rev. K Chapter 8. The relevant VXIplug&play API function is: • tat964_setPassFailParameters Pass Valid Mode This pull-down control programs the sequencer pass valid mode. This control allows the user to define the Pass as a Valid Pass. A Valid Pass is one where no channel errors were detected but there must be at least one valid pattern expect code for each pattern in the sequence step. -

Page 124: Over-Current

Publication No. 980938 Rev. K Model T940 User Manual Over-Current This command button displays the Over-Current panel so the over-current parameters can be programmed for the selected sequencer. The over-current mode should be used for channels configured in the static mode only. -

Page 125: Drive Fault

Model T940 User Manual Publication No. 980938 Rev. K Table 5-43: Over-Current Window Settings Setting Description 4’ – 8’ Set window to cables between 4 and 8 feet 8.3’ – 16.3’ Set window to cables between 8.3 and 16.3 feet 16.6’... -

Page 126: Probe

Publication No. 980938 Rev. K Model T940 User Manual pattern codes and can be used to detect dynamic over-current conditions. If enabled a drive fault will disable all channels of the specified sequencer and a drive fault event will be generated. Use tat964_querySequencerEvent() to query the drive fault event and tat964_querySequencerDriveFault() to query which channel caused the drive fault. -

Page 127: Offset

Model T940 User Manual Publication No. 980938 Rev. K Counting and Logging Errors section of Chapter 8 for a discussion on the impact of the Probe State on data rates. The relevant VXIplug&play API function is: • tat964_setProbeInterfaceState Offset The Probe offset allows the user to shift the probe record signals to accommodate system and UUT delay. -

Page 128: Probe Button

Publication No. 980938 Rev. K Model T940 User Manual Setting Description Window 4 Window 4 open edge samples the Open CRC. Window 4 Window 4 close edge samples the Close CRC. The relevant VXIplug&play API function is: • tat964_setProbeConfiguration Probe Button This control sets the probe button action. -

Page 129: Probe Cal Connect

Model T940 User Manual Publication No. 980938 Rev. K probe input is routed through AUX1 A on the UR14 Driver/Receiver board. The relevant VXIplug&play API function is: • tat964_setProbeLevels Probe Cal Connect This control opens and closes the probe calibration channel connect relay. The probe calibration is routed through AUX2 A on the UR14 Driver/Receiver board. -

Page 130: Dc Cal

Publication No. 980938 Rev. K Model T940 User Manual The user is then prompted to adjust the probe compensation screw until the probe module LED labeled D1 illuminates. The relevant VXIplug&play API function is: • tat964_probeCalibration DC Cal This control initiates a DC level calibration. The user is prompted to connect the probe to the calibration BNC. -

Page 131: Attributes

Model T940 User Manual Publication No. 980938 Rev. K • tat964_probeCalibration Attributes This command button on the Configure DSA Settings panel displays the Attribute panel so that the sequencer attributes can be programmed. Figure 5-28: Attribute Panel Jump Pass Fail This control sets the sequencer step pass/fail accumulator mode. -

Page 132: Window 3 Mode

Publication No. 980938 Rev. K Model T940 User Manual Table 5-50: Phase 3 Mode Settings Setting Description Typical Usage Normal Phase 3 is sourced from the internal Internally programmed timing for drive phase generator. (Default) phases. Jump 1 Phase 3 is sourced form the Jump 1 Externally programmed timing controlled by an external stimulus clock trigger signal. -

Page 133: Crc Algorithm And Capture Mask

Model T940 User Manual Publication No. 980938 Rev. K The selections for this pull-down control are: Table 5-52: CRC Preload Settings Setting Description Zeros Preload 0’s Ones Preload 1’s Masked Mask Preload The relevant VXIplug&play API function is: • tat964_setSequencerAttribute CRC Algorithm and Capture Mask These numeric controls set the number for the CRC algorithm and for the CRC capture mask settings and are available in sequencer revision 0.23 and later. -

Page 134: Configuring The I/O Channels

Publication No. 980938 Rev. K Model T940 User Manual Table 5-54: Static State Settings Setting Description Disable static operation Enable static operation. The relevant VXIplug&play API function is: • tat964_setStaticState Configuring the I/O Channels Configuring the channels is a three step process: 1. -

Page 135: Channel Parameters

Model T940 User Manual Publication No. 980938 Rev. K 1. Left click on the desired channel in the channel list control. A check mark indicates the channel has been selected. Multiple channels can be selected. 2. Use the pull down list box to select the desired channels and press the Select command button. -

Page 136: Stimulus Format

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API function is: • tat964_setChannelParameters Stimulus Format This pull-down control programs the stimulus data formatting for the selected channel(s). The selections for this pull-down control are: Table 5-56: Stimulus Format Settings Setting Stimulus Format Description •... -

Page 137: Capture Signal

Model T940 User Manual Publication No. 980938 Rev. K Setting Stimulus Format Description • Comp Surround Start of Pattern – Output driver goes to complemented level determined by the Pattern Code instruction in Pattern Memory • Phase Assert – Output driver goes to level determined by the Pattern Code instruction in Pattern Memory. -

Page 138: Capture Mode

Publication No. 980938 Rev. K Model T940 User Manual Table 5-57: Capture Signal Settings Setting Description Window 1 Use Window 1 timing signal to control input comparator timing. Window 2 Use Window 2 timing signal to control input comparator timing. Window 3 Use Window 3 timing signal to control input comparator timing. -

Page 139: Properties

Model T940 User Manual Publication No. 980938 Rev. K Table 5-59: Static Mode Settings Setting Description Static Mode enabled for selected channel(s). Static mode disabled for selected channel(s. Note: The static state must be enabled before setting the static mode. The relevant VXIplug&play API function is: •... -

Page 140: Driver Levels

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-30: Configure Channel Properties Panel Driver Levels The driver levels allow the user to set the Drive High (DVH) and Drive Low (DVL) voltage. The min/max levels are dependent on the installed Driver/Receiver board as well as the voltage mode. -

Page 141: Comparator Levels

Model T940 User Manual Publication No. 980938 Rev. K • tat964_setChannelSourceLevels Comparator Levels The comparator levels allow the user to set the Compare High (CVH) and Compare Low (CVL) voltage. The min/max levels are dependent on the installed Driver/Receiver board as well as the voltage mode. -

Page 142: Over-Current Alarm Levels

Publication No. 980938 Rev. K Model T940 User Manual Over-Current Alarm Levels This allows the user to set the over-current high (OC High (mA)) and over- current low (OC Low (mA)) alarm levels for static current limits on the DR3e, DR9, and UR14 (see Drive Fault for dynamic current limiting). -

Page 143: Figure 5-31: Current Load

Model T940 User Manual Publication No. 980938 Rev. K Source VCOM Low Load State VCOM High Sink Figure 5-31: Current Load When the channel voltage is greater than the VCOM High level, the Sink current becomes active. When the channel voltage is less than the VCOM Low level, the Source current becomes active. -

Page 144: Channel Connect

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API functions are: • tat964_setChannelSenseParameters • tat964_setChannelLoadState Channel Connect This control allows the user to control the isolation and analog bypass relays. The selections for this pull-down control are: Table 5-63: Channel Connect Settings Setting Description... -

Page 145: Channel Mode

Model T940 User Manual Publication No. 980938 Rev. K The relevant VXIplug&play API function is: • tat964_setComparatorDelay Channel Mode This control programs the front panel channel mode setting. The channel mode can be set to: • Single-ended • Differential with 100 Ω differential termination •... -

Page 146: Compare Input (V)

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-33: Configure UR14 Channel Properties Panel Compare Input (V) This control sets the comparator level of the selected channel group. Min: 0.0 Max: 20.0 The relevant VXIplug&play API function is: •... -

Page 147: Figure 5-34: Configure Aux Channels Panel

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-34: Configure AUX Channels Panel Figure 5-35: Configure AUX Channels Panel UR14 The AUX channels are a set of 12 multi-purpose signals that can be used for any of the following I/O resources: 1. -

Page 148: Table 5-64: Drn Aux Configuration

Publication No. 980938 Rev. K Model T940 User Manual 4. Vector Jump Address Input 5. Waveform Output 6. Pulse Generator Output 7. Sync Output 8. Frequency Synthesizer Output 9. Timing Set Output Signals a. Phase b. Window c. T0_CLK d. Pattern Clock 10. -

Page 149: Configuring The Aux/Uaux Signals

Model T940 User Manual Publication No. 980938 Rev. K Signal Logic Special Use AUX6 A LVTTL Shares front panel pin with AUX10 A AUX7 A LVTTL Shares front panel pin with AUX11 A AUX8 A LVTTL Shares front panel pin with AUX12 A AUX9 A ECL differential or bipolar... -

Page 150: State

Publication No. 980938 Rev. K Model T940 User Manual State This control allows the user to set the output state for the selected AUX signal. Table 5-66: AUX Output State Settings Setting Description Disable the AUX output. Enable the AUX output. Enable and invert the AUX output. -

Page 151: Input Bus Source

Model T940 User Manual Publication No. 980938 Rev. K Setting Description FS Reference Frequency synthesizer reference signal Frequency Synthesizer Frequency synthesizer signal Jump Strobe Test signal Int Error Test signal Ext Error Test signal HIGH Drive high PASS PASS flag FAIL FAIL flag CONDEN... -

Page 152: Connect State

Publication No. 980938 Rev. K Model T940 User Manual Setting Description ECLTRG0,1 Source set to VXI ECL trigger TTLTRG0-7 Source set to VXI TTL trigger LTB0-7 Source set to Linked Trigger bus signal Connect State This control allows the user to open or close the isolation relay. DR2 and DR7 Driver/Receiver boards do not have isolation relays. -

Page 153: Configuring The Interrupts

Model T940 User Manual Publication No. 980938 Rev. K Table 5-70: Logic Mode Settings Setting Description LVTTL AUX configured as LVTTL. ECL Bipolar ECL AUX configured as differential ECL The relevant VXIplug&play API function is: • tat964_setAuxLogicMode Configuring the Interrupts There are five hardware groups on the T940 that are capable of generating VXI interrupt. -

Page 154: Condition

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-37: Configure Interrupt Condition This control indicates that the interrupt condition is currently true. The relevant VXIplug&play API function is: • tat964_queryInterruptCondition Event True This control enables a VXI interrupt to be generated when any of the associated hardware groups enabled event bits goes from false to true. -

Page 155: Editing The Data Sequencers

Model T940 User Manual Publication No. 980938 Rev. K Editing the Data Sequencers Editing the data sequencers consists of programming the following: 1. Timing Sets 2. Patterns 3. Waveforms 4. Sequence Parameters 5. Sequence Steps Figure 5-38: Editing the Data Sequencers Editing the Timing Sets The timing sets are used to control the channel drivers and receivers. -

Page 156: Figure 5-40: Data Sequencer Timing Sets Panel

Publication No. 980938 Rev. K Model T940 User Manual The figure above represents two channels with the following configuration: • Output Signal = Phase 1 Stimulus Format = Return to One Pattern Code = Drive Low • Output Signal = Phase 2 Stimulus Format = Non Return Pattern Code = Drive High The Assert signal (rising edge) causes the pattern code to be loaded. -

Page 157: Timing Set Value Rules

Model T940 User Manual Publication No. 980938 Rev. K • Indexed – 256 timing sets with four phase/window groups per timing set and 4096 sequence steps where each sequence step points to one of the 256 timing sets. Double-click on one of the available Assert/Return/Open/Close cells. Enter the desired value using the numeric keys or the up/down arrows followed by the Enter key. -

Page 158: Phase/Window Spanning

Publication No. 980938 Rev. K Model T940 User Manual 2. Idle/Standby Timing Phase/Window Spanning Phase/Window spanning allows the user to Assert/Open the timing signal in one pattern and Return/Close the signal in a different pattern. The following steps describe how to span timing signals across multiple patterns: 1. -

Page 159: Append

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-41: Edit Patterns Panel This panel lists all the defined pattern sets. The associated step number, size and offset are displayed. The size of a pattern set can be from 1 to 262144. The offset can be from 0 to 262140 and must be a multiple of four. -

Page 160: Assign

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-42: Append Data Sequencer Pattern Sets Panel Enter the Number of Patterns to append and press the Apply command button. Append pattern memory will be initialized to Pattern Code “R”, which repeats the previous code. -

Page 161: Edit Data

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-43: Assign Data Sequencer Pattern Sets Panel Enter the new Size and/or Offset and press the Apply command button. Assigned pattern memory will not be initialized. Press the Close command button to exit the panel without any changes. The relevant VXIplug&play API function is: •... -

Page 162: Figure 5-44: Pattern Set Sequencer Data Panel

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-44: Pattern Set Sequencer Data Panel Each column contains the TEST code, PROBE code and the pattern codes for all the channels. The pattern codes are described in Figure 5-47 and Table 5-TTT. The pattern set is displayed in pages of 32 patterns. -

Page 163: Figure 5-46: Goto Pattern Panel

Model T940 User Manual Publication No. 980938 Rev. K To jump to a specific pattern number, right click in any of the cells to display the Goto Pattern panel Figure 5-46: Goto Pattern Panel The menu bar: View > Pattern Codes displays a legend of all the available TEST and CH entries. -

Page 164: Figure 5-48: Probe Codes

Publication No. 980938 Rev. K Model T940 User Manual The row labeled “PROBE” displays the probe expect code for each pattern. There are thirty four probe expect codes: Figure 5-48: Probe Codes Astronics Test Systems Soft Front Panel Operation 5-83... -

Page 165: Table 5-71: Probe Expect Codes

Model T940 User Manual Publication No. 980938 Rev. K Table 5-71: Probe Expect Codes Expect Probe Code Shortcut Description Code Signal starts above RH and crosses the RH and RL once and ends below RL. Signal starts above RH, crosses RH once, crosses RL three or more times and ends below RL. - Page 166 Publication No. 980938 Rev. K Model T940 User Manual Expect Probe Code Shortcut Description Code three or more times, crosses RH once and ends above RH. Signal remains between RL and RH Signal starts between RL and RH, crosses the RH once and ends above RH. Signal starts between RL and RH, crosses the RL once and ends below RL.

-

Page 167: Figure 5-49: Pattern Set Data - File Menu

Model T940 User Manual Publication No. 980938 Rev. K pattern code affects the driver/comparator. Table 5-72: Pattern Codes Pattern Code Driver Comparator Invert Code Expect Mode Level Disable Channel ‘Z’ None Disable Channel ‘Z’ Collect CRC ‘C’ Enable CRC Collect CRC ‘C’ Drive High ‘1’... -

Page 168: Import/Export File Format

Publication No. 980938 Rev. K Model T940 User Manual • Pattern data as ASCII Hex • Pattern data as ASCII String • Pattern data as Binary • Pattern data and flags as ASCII Hex • Pattern data and flags as ASCII String •... -

Page 169: Table 5-73: Ascii/Binary Data Format

Model T940 User Manual Publication No. 980938 Rev. K Table 5-73: ASCII/Binary Data Format Pattern Code ASCII/Binary Value ‘Z’ ‘C’ ‘0’ ‘1’ ‘R’ ‘I’ ‘L’ ‘H’ ‘V’ ‘B’ ‘l’ ‘h’ ‘/’ ‘\’ Flag Code Bit15, Bit 14 Code ‘a’ ‘b’ ‘c’... -

Page 170: Binary

Publication No. 980938 Rev. K Model T940 User Manual Probe Expect Bit 13 through Bit ‘7’ ‘8’ The ASCII characters are in four groups of eight characters and one line per pattern. A fifth column of four characters is present if flags and probe expect is included. -

Page 171: Ascii String

Model T940 User Manual Publication No. 980938 Rev. K ASCII String The ASCII string format represents pattern data as viewable ASCII strings, one character per channel, 32 characters per line (34 if flag and probe data are included). Each character is one of the pattern codes listed in Table 5-44. - Page 172 Publication No. 980938 Rev. K Model T940 User Manual (Where “x” is the sequencer you wish to configure.) Figure 5-50: Edit Waveforms Panel Waveform 1 Figure 5-51: Edit Waveforms Panel Waveform 5 Table Size This pull-down control programs the waveform table size for waveforms 1-4. Astronics Test Systems Soft Front Panel Operation 5-91...

-

Page 173: Waveform

Model T940 User Manual Publication No. 980938 Rev. K Waveforms 5 and 6 are fixed at 65536. The selections for this pull-down control are: Table 5-75: Waveform Table Size Settings Setting Description 16 x 1K 16 tables each with 1024 bits 8 x 2K 8 tables each with 2048 bits 4 x 4K... -

Page 174: Editing Sequence Parameters

Publication No. 980938 Rev. K Model T940 User Manual No transitions; Would generate the following waveform; "111..." Bits 1 through the size of the table high. Waveform five and six have a maximum of two transitions. The relevant VXIplug&play API function is: •... -

Page 175: Pipeline

Model T940 User Manual Publication No. 980938 Rev. K Given the following sample loop sequence: Step 1 jump step 1 using LC0 count 2 Step 2 jump step 1 using LC1 count 3 Example 1: If both loop counters reload on terminal count, then the step order will be: 1, 1, 2, 1, 1, 2, 1, 1, 2, 1, 1, 2 Example 2: If loop counter 0 is set to disable, then the step order will be:... -

Page 176: Set Vector Bits

Publication No. 980938 Rev. K Model T940 User Manual Window 4 Sets the closing edge of window 4 as the vector strobe. The relevant VXIplug&play API function is: • tat964_setVectorJumpStrobe Set Vector Bits This command button displays the Edit Vector Bits panel so the vector bit signal selection can be programmed for the selected sequencer. -

Page 177: Input Mode

Model T940 User Manual Publication No. 980938 Rev. K Table 5-77: Vector Bit Source Settings Setting Description None No trigger source selected AUX1-AUX12 Trigger source set to front panel signal CHT1 Trigger source set to channel test 1 ECLTRG0,1 Trigger source set to VXI ECL trigger TTLTRG0-7 Trigger source set to VXI TTL trigger... -

Page 178: Vector Bit Index

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-54: Edit Vector Table Panel Vector Bit Index This allows the user to enter the index to program. There are 16 indexes that can be set (0 to 15). The index is the binary value of the vector bits (VA0 through VA3). -

Page 179: Expect

Model T940 User Manual Publication No. 980938 Rev. K bus. In addition channel test 1 result can also be routed to any of the sequence triggers. Figure 5-55: Sequencer Channel Test Panel Expect This allows the user to enter the expect value for the channel test signal. Bit 0 of the expect value maps to the lowest channel of this sequencer and Bit 31 maps to the highest channel and this is the case for both A and B sequencers. -

Page 180: Editing Sequence Steps

Publication No. 980938 Rev. K Model T940 User Manual Editing Sequence Steps The sequence steps are used to control the flow of the patterns and assign timing. Access this panel from the menu bar: Edit > Data Sequencer x> Sequence Steps. -

Page 181: Internal T0Clk

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-57: Sequence Step Data Panel Internal T0CLK This control allows the user to specify the Internal T0CLK period. When the system clock source is set to internal T0CLK, this control specifies the system clock period. -

Page 182: Cpp Phase And Window Triggering

Publication No. 980938 Rev. K Model T940 User Manual Example 1: CPP = 1 System Clock Pattern Clock Period = Sytem Clock Example 2: CPP = 2 System Clock Pattern Clock Period = 2 x Sytem Clock Example 3: CPP = 3 System Clock Pattern Clock Period = 3 x Sytem Clock... -

Page 183: Last Step

Model T940 User Manual Publication No. 980938 Rev. K Last Step This control allows the user to specify the Last Step flag. This flag indicates whether the current step is the last step of the sequence burst (True) or a sub- step of a multi-step burst (False). -

Page 184: Jump Step

Publication No. 980938 Rev. K Model T940 User Manual Gosub to step 10 and step 13 has the Gosub Return flag set, then the step number sequence starting from 1 would be, 1, 2, 3, 4, 5, 10, 11, 12, 13, 6, 7, 10, 11, 12, 13, 8, 9 … The selections for this pull-down control are: Table 5-81: Jump Type Settings Setting... -

Page 185: Loop Count

Model T940 User Manual Publication No. 980938 Rev. K Setting Description Step FAIL Jump if the PASS/FAIL flag is equal to FAIL Step PASS Jump if the PASS/FAIL flag is equal to PASS Sequence FAIL Jump if Burst Error Count is not equal to zero. Sequence PASS Jump if Burst Error Count is equal to zero. -

Page 186: Loop Counter

Publication No. 980938 Rev. K Model T940 User Manual Loop Counter This numeric control programs the Loop Counter number. Jumps can be qualified by a loop counter. Sixteen loop counters are available. Nested loops are supported including up to all 16 counters. The relevant VXIplug&play API function is: •... -

Page 187: Timing

Model T940 User Manual Publication No. 980938 Rev. K burst: 1. Error Address Memory 2. Record Index Memory 3. Record Memory There is also the Error Counter which counts the number of pattern errors that occurred during the previous sequence burst. The Error Count can be queried using the "tat964_queryErrorFlags"... -

Page 188: Patterns

Publication No. 980938 Rev. K Model T940 User Manual Editing the Timing Sets in Chapter 5). Figure 5-58: Edit Timing Set Panel The relevant VXIplug&play API function is: • tat964_setSequenceTimingData Patterns If the Patterns control reads 0, then this command button displays the Initialize Step Pattern Set panel. -

Page 189: Figure 5-59: Initialize Step Pattern Set Panel

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-59: Initialize Step Pattern Set Panel The relevant VXIplug&play API function is: • tat964_initPatternSet If the Patterns control reads a number greater than zero, then this command button displays the Edit Pattern Data panel (see Editing the Patterns Chapter 5). -

Page 190: Properties

Publication No. 980938 Rev. K Model T940 User Manual Properties This command button displays the Sequence Step Properties panel. The sequence step properties consist of the following hardware settings: 1. Handshake Control (Pause/Resume) 2. Waveform 3. Phase Trigger Figure 5-61: Sequence Step Properties Panel Handshake Control The handshake control allows the user to assign a signal (Pause) that can be either internal or external, which will pause the sequencer. -

Page 191: Resume Modifier

Model T940 User Manual Publication No. 980938 Rev. K Setting Pause Signal Resume Signal Pause Trigger 1 True Pause Trigger 1 signal Pause Trigger 1 Resume true Pause Trigger 1 Not Pause Trigger 1 signal Pause Trigger 1 Resume True not true Pause Trigger 2 True Pause Trigger 2 signal... -

Page 192: Waveform Properties

Publication No. 980938 Rev. K Model T940 User Manual received). The selections for this pull-down control are: Table 5-83: Handshake Modifier Settings Setting Resume Modifier None No modifier, resume on ‘Resume Signal” only Pattern Delay 1 Pattern Delay 1 timer Pattern Delay 2 Pattern Delay 2 timer Pattern Timeout... -

Page 193: Execute The Sequence

Model T940 User Manual Publication No. 980938 Rev. K Execute the Sequence Sequence execution and control is performed from the Execute panel. Access this panel from the menu bar: Execute > DSx. (Where “x” is the sequencer you wish to execute.) Figure 5-62: Executing a Sequence Panel The following sections describe the execution overview as well as the indicators and controls of the execute panel. -

Page 194: Execution Overview

Publication No. 980938 Rev. K Model T940 User Manual Execution Overview The sequencer execution state diagram is illustrated in the following figure. reset IDLE HALT execute execute idle halt last step/stop (idle finish mode) reset manual resume single step execute ACTIVE RESET execute idle... -

Page 195: Table 5-85: Execute State Transition Description

Model T940 User Manual Publication No. 980938 Rev. K Setting Description Entry Condition 5. Active step: User 6. Pattern Memory: Free IDLE 1. Idle Active: true “execute idle”, “last step/stop idle finish mode” 2. Sequence Active: false 3. Halt flag: false 4. -

Page 196: Execute Panel Indicators

Publication No. 980938 Rev. K Model T940 User Manual Transition Description Soft Front Panel Control • last step/stop Sequence completes step Set Finish Mode to “Idle” (idle finish with last step flag true or • Enter step number and stop command. Finish mode) depress Execute command Mode set to Idle... -

Page 197: Halt Led

Model T940 User Manual Publication No. 980938 Rev. K The relevant VXIplug&play API function is: • tat964_querySequencerStatus Halt LED When green, indicates that the halt mode has been armed. When red, indicates that the sequencer is in the HALT state. The relevant VXIplug&play API function is: •... -

Page 198: Sequence Active

Publication No. 980938 Rev. K Model T940 User Manual • tat964_queryFrontEndCondition Sequence Active This numeric indicator displays the execution time of the previous sequence burst (10 ns resolution ± 10 ns with an accuracy of 500 ppm up to~43 sec). The relevant VXIplug&play API function is: •... -

Page 199: Channel Drivers

Model T940 User Manual Publication No. 980938 Rev. K Channel Drivers This pull-down control programs the channel drivers. The selections for this pull-down control are: Table 5-86: Channel Drivers Settings Setting Description Disabled All the channel drivers are forced off (disabled). -

Page 200: Execute Step

Publication No. 980938 Rev. K Model T940 User Manual The relevant VXIplug&play API function is: • tat964_setIdleSequence Execute Step This control sets the step number for the Execute command button operation. The relevant VXIplug&play API functions are: • tat964_executeSequence • tat964_armSequence Burst This control sets the burst count for the Execute command button operation. -

Page 201: Finish Mode

Model T940 User Manual Publication No. 980938 Rev. K Setting Description Step Fail Halt the current sequence at the end of the next sequence step if the pass/fail flag is set to fail. Sequence Fail Halt the current sequence at the end of the next sequence if the pass/fail flag is set to fail. -

Page 202: Stop Mode

Publication No. 980938 Rev. K Model T940 User Manual Stop Mode This pull-down control programs the stop mode. The stop mode controls what action a CPU generated stop or a triggered stop will perform if received. The selections for this pull-down control are: Table 5-89: Stop Mode Settings Setting Description... -

Page 203: Sync Number

Model T940 User Manual Publication No. 980938 Rev. K outputs. The sync parameters consist of an offset and a length. Once the programmed sync event occurs, the sync pulse will begin after the "offset" and last for "length". Both "offset" and "length" are specified in pattern clocks. The sync pulse will not extend past the end of the sequence. -

Page 204: Length

Publication No. 980938 Rev. K Model T940 User Manual Length This control sets the length for the sync pulse from 0 (no pulse) to 4095 patterns. The relevant VXIplug&play API function is: • tat964_setSyncParameters Execute Panel Command Buttons There are ten command buttons that control DRM sequence, deskew and pulse generator execution. -

Page 205: Resume

Model T940 User Manual Publication No. 980938 Rev. K Resume The Resume command button terminates a pause or halt state and sequence execution continues. See the Pause and Halt section in Chapter 8 for additional details about resuming a pause or halt. The relevant VXIplug&play API function is: •... -

Page 206: Stop Pg

Publication No. 980938 Rev. K Model T940 User Manual Stop PG The Stop PG command button stops the pulse generator. The relevant VXIplug&play API function is: • tat964_stopPulseGenerator Analyze the Execution Results After sequence execution has been performed, the final step is to analyze the results to determine if the recorded input data is valid and if it matches the expected results. -

Page 207: Stimulus Delay

Model T940 User Manual Publication No. 980938 Rev. K Figure 5-66: Static Data Panel The static data panel contains controls that program the static timing and stimulus data and displays the current static response data. Prior to sequencer revision 0.21, the static timing uses the pulse generator to specify the stimulus delay and the response delay for all the static channels to within 15ns. -

Page 208: Stimulus

Publication No. 980938 Rev. K Model T940 User Manual For sequencer revision 0.21 and later, this control sets the delay when the static input pins will be sampled from 0 to 6.5ms with 100ns resolution. The delay is from the execution of the “tat964_executeStaticPattern” API. The relevant VXIplug&play API function is: •... -

Page 209: Results

Model T940 User Manual Publication No. 980938 Rev. K menu bar selection. (Where “x” is the sequencer you wish to query.) Figure 5-67: Kept Data Panel The kept data represents the current pattern code that is not “Invert Previous Code” or “Repeat Previous Code”. Note: The Kept Data is updated at the end of a pattern so the contents of the kept data when halted or paused will contain the codes from the previous pattern. -

Page 210: View

Publication No. 980938 Rev. K Model T940 User Manual Figure 5-68: View Results Data Panel View This pull-down control selects the results to view. The selections for this pull-down control are: Table 5-94: Results View Settings Setting Description CRCs Display the CRC data from the previous sequence execution. -

Page 211: Error Address Save File Format

Model T940 User Manual Publication No. 980938 Rev. K <id>,<crc><lf> Where: <id> CH01 through CH32, PG0 and PG1. <crc> The CRC value. Error Address Save File Format The Error Address results are saved in the following format: <header><line feed> <step>,<offset>,<pma>,< data><line feed> Where: <header>... -

Page 212: Probe Data Save File Format

Publication No. 980938 Rev. K Model T940 User Manual Probe Data Save File Format The Record Data results are saved in the following format: <header><line feed> <step>,<offset>,<data><line feed> Where: <header> “STEP,OFFSET,RECORD DATA” <step> Step number of the error. <offset> Pattern number. <data>... -

Page 213: Error Address Display