Table of Contents

Advertisement

Quick Links

Advertisement

Table of Contents

Summary of Contents for Gigabyte MZ71-CE0

- Page 1 MZ71-CE0 MZ71-CE1 AMD EPYC™ Dual processor motherboard User Manual Rev. 1.0...

- Page 2 GIGABYTE's prior written permission. Documentation Classifications In order to assist in the use of this product, GIGABYTE provides the following types of documentation: User Manual: detailed information & steps about the installation, configuration and use this product (e.g. motherboard, server barebones), covering hardware and BIOS.

-

Page 3: Table Of Contents

Table of Contents MZ71-CE0/MZ71-CE1 Motherboard Layout ..............6 Block Diagram .........................8 Chapter 1 Hardware Installation ..................9 Installation Precautions ..................9 1-2 Product Specifications ..................10 Installing and Removing the CPU and Heat Sink ........... 12 Installing and Removing Memory ..............13 1-4-1 8-Channel Memory Configuration ................13 1-4-2 Installing and Removing a Memory Module ............14... - Page 4 2-2-20 Broadcom Network Connection ................64 AMD CBS Menu ..................... 71 2-3-1 CPU Common Options ...................72 2-3-2 DF Common Options ....................77 2-3-3 UMC Common Options ..................82 2-3-4 NBIO Common Options ..................95 2-3-5 FCH Common Options ..................101 2-3-6 NTB Common Options ..................105 2-3-7 SOC Miscellaneous Control .................106 AMD PBS Menu ...................

- Page 5 2-11-7 [0xACXX] assigned for AGESA CCX Module ............142 2-11-8 [0xADXX] assigned for AGESA DF Module ............143 2-11-9 [0xAFXX] assigned for AGESA FCH Module ............143 2-12 BIOS POST Beep code (AMI standard) ............145 2-12-1 PEI Beep Codes ....................145 2-12-2 DXE Beep Codes ....................145 - 5 -...

-

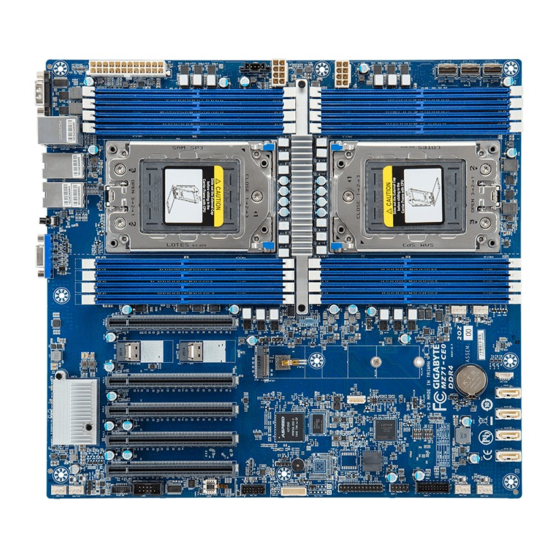

Page 6: Mz71-Ce0/Mz71-Ce1 Motherboard Layout

MZ71-CE0/MZ71-CE1 Motherboard Layout 34 35 36 37 CPU0 CPU1 - 6 -... - Page 7 VGA Port SW_ID ID button with LED LAN1 10GbE Ethernet LAN Port #1 (MZ71-CE0)/GbE Ethernet LAN Port #1 (MZ71-CE1) LAN2 10GbE Ethernet LAN Port #2 (MZ71-CE0)/GbE Ethernet LAN Port #2 (MZ71-CE1) USB3_MLAN Server Management LAN Port (Top)/ USB3.0 Ports (Bottom)

-

Page 8: Block Diagram

Block Diagram - 8 -... -

Page 9: Chapter 1 Hardware Installation

Chapter 1 Hardware Installation Installation Precautions The motherboard contains numerous delicate electronic circuits and components which can become damaged as a result of electrostatic discharge (ESD). Prior to installation, carefully read the user's manual and follow these procedures: • Prior to installation, do not remove or break motherboard S/N (Serial Number) sticker or warranty sticker provided by your dealer. -

Page 10: Product Specifications

Š Graphics 2D Video Graphic Adapter with PCIe bus interface Š 1920x1200@60Hz 32bpp Š MZ71-CE0 2 x 10GbE LAN ports (1 x Broadcom® BCM57416) Š 1 x 10/100/1000 management LAN Š MZ71-CE1 2 x 1GbE LAN ports (1 x Broadcom® BCM5720) Š... - Page 11 GIGABYTE Management Console (AMI MegaRAC SP-X) web interface Š E-ATX Š Form Factor 305W x 330D (mm) Š GIGABYTE reserves the right to make any changes to the product specifications and product-related information without prior notice. - 11 - Hardware Installation...

-

Page 12: Installing And Removing The Cpu And Heat Sink

Installing and Removing the CPU and Heat Sink Read the following guidelines before you begin to install the CPU: • Make sure that the motherboard supports the CPU. • Always turn off the computer and unplug the power cord from the power outlet before installing the CPU to prevent hardware damage. -

Page 13: Installing And Removing Memory

Installing and Removing Memory Read the following guidelines before you begin to install the memory: • Make sure that the motherboard supports the memory. It is recommended that memory of the same capacity, brand, speed, and chips be used. • Always turn off the computer and unplug the power cord from the power outlet before installing the memory to prevent hardware damage. -

Page 14: Installing And Removing A Memory Module

1-4-2 Installing and Removing a Memory Module Before installing a memory module, make sure to turn off the computer and unplug the power cord from the power outlet to prevent damage to the memory module. Be sure to install DDR4 DIMMs on to this motherboard. Follow these instructions to install a DIMM module: Insert the DIMM memory module vertically into the DIMM slot and push it down. - Page 15 LRDIMM Maximum Frequency Supported Table DIMM Frequency (MT/s) DIMMs Populated 2S2R 1.2V 2S4R 3200 3200 2933 Not Supported 2933 3DS RDIMM Maximum Frequency Supported Table DIMM Frequency (MT/s) DIMMs Populated 2S2R 1.2V 2S4R 2933 2666 Note: • 1R: 1 package rank of SDP DRAMs •...

-

Page 16: Installing And Removing The M.2 Ssd Module

Installing and Removing the M.2 SSD Module Follow the steps below to install an optional M.2 SSD module on your motherboard. Step1. Insert the M.2 SSD module into the slot. Step2. Secure it with the screw, tightening as necessary to fasten the M.2 SSD module in place. Hardware Installation - 16 -... -

Page 17: Back Panel Connectors

The USB port supports the USB 3.0 specification. Use this port for USB devices such as a USB keyboard/mouse, USB printer, USB flash drive etc. 10GBASE-T RJ-45 LAN Port #2 (MZ71-CE0) The 10 Gigabit Ethernet LAN port provides Internet connection at up to 10 Gbps data rate. See the section below for a description of the states of the LAN port LEDs. - Page 18 LAN and ID Button LEDs Link/Activity LED Speed LED 10GbE LAN LED: 10/100/1000 LAN LED: State Description State Description Yellow On 1Gbps data rate Yellow On 5Gbps, 2.5Gbps, 1Gps data rate Green On 100Mbps data rate Green On 10Gbps data rate 10Mbps data rate 100Mbps data rate LAN Port...

-

Page 19: Internal Connectors

Internal Connectors CPU0 CPU1 4 5 6 7 8 9 10 14) SYS_FAN4 P12V_1 (for CPU0) 15) PMBUS P12V_2 (for CPU1) 16) F_USB3 SATA0 17) F_USB2 SATA1 18) COM2 SATA2 19) FP_1 SATA3 20) BP_1 SATA_SGP 21) SPI_TPM CPU_FAN0 22) IPMB 10) CPU_FAN1 23) LED_BMC1 11) SYS_FAN1... - Page 20 1/2/3) ATX/P12V_1/P12V_2 (2x12 Main Power Connector and 2x4 12V Power Connector) With the use of the power connector, the power supply can supply enough stable power to all the components on the motherboard. Before connecting the power connector, first make sure the power supply is turned off and all devices are properly installed. The power connector possesses a foolproof design. Connect the power supply cable to the power connector in the correct orientation.

- Page 21 4/5/6/7) SATA0/SATA1/SATA2/SATA3 (SATA 6Gb/s Connectors) The SATA connectors conform to SATA 6Gb/s standard and are compatible with SATA 3Gb/s standard. Each SATA connector supports a single SATA device. Pin No. Definition 8) SATA_SGP (SATA SGPIO) Connector Serial General Purpose Input/Output (SGPIO) is a communication method used between a host bus adapter (HBA) and a main board.

- Page 22 9/10/11/12/13/14) CPU0_FAN//CPU1_FAN/SYS_FAN1/SYS_FAN2/SYS_FAN3/SYS_FAN4 (CPU FAN/System FAN Headers) The motherboard has one 4-pin CPU fan header (CPU_FAN), and two 4-pin (SYS_FAN) system fan headers. Most fan headers possess a foolproof insertion design. When connecting a fan cable, be sure to connect it in the correct orientation (the black connector wire is the ground wire). The motherboard supports CPU fan speed control, which requires the use of a CPU fan with fan speed control design.

- Page 23 16/17) F_USB3/ F_USB2 (USB 3.0 Connector/ 2.0 Header) The connector/header conform to USB 2.0/ 3.0 specification. Each USB connector/header can provide two USB ports via an optional USB bracket. For purchasing the optional USB bracket, please contact the local dealer. USB 2.0 Header Pin No. Definition Pin No. Definition Power (5V) USB DY+ Power (5V) USB DX- USB DY-...

- Page 24 NMI Switch LAN2 Link LED- *Note: Pin 7 & Pin 9 are reserved for Gigabyte systems. The front panel design may differ by chassis. A front panel module mainly consists of power switch, reset switch, power LED, hard drive activity LED, speaker etc. When connecting your chassis front panel module to this header, make sure the wire assignments and the pin assignments are matched correctly.

- Page 25 20) BP_1 (HDD Backplane Board Header) Pin No. Definition Pin No. Definition HP_ALERT_L BPMI DIN/OUT BPMI DIN/IN BPMI_LOAD BPMI_CLK PLD_Program_EN GLED_AMB_N GLED_GRN_N FAN_IRQ_N Reserved BP_SCL BP_SDA BP_RST_N SMB_U2_TMP_SCL SMB_U2_TMP_SDA I2C_DEV_RST PH_HP_SCL0 PH_HP_SDA0 PH_HP_SCL1 PH_HP_SDA1 P3V3_AUX P3V3_AUX 21) SPI_TPM (Trusted Platform Module Connector) Trusted Platform Module (TPM) is an international standard for a secure cryptoprocessor, a dedicated microcontroller designed to secure hardware through integrated cryptographic keys.

- Page 26 22) IPMB (Intelligent Platform Management Bus) Connector The Intelligent Platform Management Bus Communications Protocol defines a byte-level transport for transferring Intelligent Platform Management Interface Specification (IPMI) messages between intelligent I2C devices. Pin No. Definition Clock Data 23) LED_BMC (BMC Firmware Readiness LED) State Description BMC firmware is initial Blink BMC firmware is ready AC loss Hardware Installation - 26 -...

- Page 27 24) BAT (Battery Socket) The battery provides power to keep the values (such as BIOS configurations, date, and time information) in the CMOS when the computer is turned off. Replace the battery when the battery voltage drops to a low level, or the CMOS values may not be accurate or may be lost. • Always turn off your computer and unplug the power cord before replacing the battery. •...

-

Page 28: Jumper Settings

Jumper Settings Clear CMOS CLR_CMOS Enable Default Jumper Name Jumper Setting 1-2: Normal operation. (Default) Clear CMOS 2-3: Clear CMOS data. HSMB_SEL BIOS Defined BIOS Defined BIOS PWD Clear Supervisor Password Normal [Default] BIOS Recovery BIOS Recovery Mode Normal [Default] Hardware Installation - 28 -... -

Page 29: Chapter 2 Bios Setup

Chapter 2 BIOS Setup BIOS (Basic Input and Output System) records hardware parameters of the system in the EFI on the motherboard. Its major functions include conducting the Power-On Self-Test (POST) during system startup, saving system parameters, loading the operating system etc. The BIOS includes a BIOS Setup program that allows the user to modify basic system configuration settings or to activate certain system features. When the power is turned off, the battery on the motherboard supplies the necessary power to the CMOS to keep the configuration values in the CMOS. - Page 30 Main This setup page includes all the items of the standard compatible BIOS. Advanced This setup page includes all the items of AMI BIOS special enhanced features. (ex: Auto detect fan and temperature status, automatically configure hard disk parameters.) AMD CBS This setup page includes the common items for configuration of AMD motherboard-related information. AMD PBS Option This setup page includes the common items for configuration of AMD CPM RAS related settings. Chipset This setup page includes all the submenu options for configuring the functions of the North Bridge.

-

Page 31: The Main Menu

The Main Menu Once you enter the BIOS Setup program, the Main Menu (as shown below) appears on the screen. Use arrow keys to move among the items and press <Enter> to accept or enter other sub-menu. Main Menu Help The on-screen description of a highlighted setup option is displayed on the bottom line of the Main Menu. - Page 32 Parameter Description BIOS Information Project Name Displays the project name information. Project Version Displays version number of the BIOS setup utility. Build Date and Time Displays the date and time when the BIOS setup utility was created. BMC Information (Note1) BMC Firmware Version Displays BMC firmware version information. (Note1) Processor Information CPU0 Brand String/ CPU1 Brand String/ CPU Speed / Processor Displays the technical specifications for the installed processor(s).

- Page 33 Parameter Description AGESA PI Version PI Version Displays AGESA PI version information. Onboard LAN Information LAN1 MAC Address (Note) Displays LAN MAC address information. LAN2 MAC Address (Note) Displays LAN MAC address information. System Date Sets the date following the weekday-month-day-year format. System Time Sets the system time following the hour-minute-second format.

-

Page 34: Advanced Menu

Advanced Menu The Advanced Menu displays submenu options for configuring the function of various hardware components. Select a submenu item, then press <Enter> to access the related submenu screen. MZ71-CE0 BIOS Setup - 34 -... - Page 35 MZ71-CE1 Parameter Description When ErP Mode is enabled, fan speed will be adjusted and any redundant ErP Mode PSU will be placed into a standby state (“Cold Redundancy”) in order to (Energy-related Products) decrease power consumption when the server is in idle mode. Options available: Disabled, Lot 9. Default setting is Disabled. - 35 - BIOS Setup...

-

Page 36: Trusted Computing

2-2-1 Trusted Computing Parameter Description Configuration Enable/Disable BIOS support for security device. OS will not show security device. TCG EFI protocol and INT1A interface will not be Security Device Support available. Options available: Enable, Disable. Default setting is Enable. Select Enable to activate TPM support feature. SPI TPM Support Options available: Enabled, Disabled. -

Page 37: Psp Firmware Versions

2-2-2 PSP Firmware Versions The PSP Firmware Versions page displays the basic PSP firmware version information. Items on this window are non-configurable. - 37 - BIOS Setup... -

Page 38: Ast2500 Super Io Configuration

2-2-3 AST2500 Super IO Configuration Description Parameter AST2500 Super IO Configuration Super IO Chip Displays the super IO chip information Serial Port 1/2 Press [Enter] for configuration of advanced items. Configuration BIOS Setup - 38 -... - Page 39 2-2-3-1 Serial Port 1/2 Configuration - 39 - BIOS Setup...

- Page 40 Description Parameter Serial Port 1/2 Configuration Enable/Disable the Serial Port (COM). When set to Enabled allows you to configure the Serial port 1/2 settings. When set to Disabled, displays no Serial Port (Note1) configuration for the serial port. Options available: Enabled, Disabled. Default setting is Enabled. Devices Settings Displays the Serial Port 1/2 device settings. (Note2) Select an optimal settings for Super IO Device. Options available for Serial Port 1: Auto IO=3F8h;...

-

Page 41: S5 Rtc Wake Settings

2-2-4 S5 RTC Wake Settings Parameter Description Enable/Disable system wake on alarm event. Options available: Disabled, Fixed Time, Dynamic Time. When Fixed Time is Wake System from S5 (Note) selected, system will wake on the hr::min::sec specified. Default setting is Disabled. (Note) Advanced items prompt when this item is defined. - 41 - BIOS Setup... -

Page 42: Serial Port Console Redirection

2-2-5 Serial Port Console Redirection Parameter Description Select whether to enable console redirection for specified device. Console COM1/Serial Over redirection enables the users to manage the system from a remote LAN & COM2 Console location. Redirection (Note) Options available: Enabled, Disabled. Default setting is Disabled. Press [Enter] to configure advanced items. Please note that this item is configurable when COM1/Serial Over LAN &... - Page 43 Parameter Description Parity Š – A parity bit can be sent with the data bits to detect some transmission errors. – Even: parity bit is 0 if the num of 1's in the data bits is even. – Odd: parity bit is 0 if num of 1's in the data bits is odd. –...

- Page 44 Parameter Description Legacy Console Redirection Press [Enter] to configure advanced items. Redirection COM Port Š – Selects a COM port for Legacy serial redirection. – Options available: COM1/SOL, COM2. Default setting is COM1/ SOL. Resolution Š – Selects the number of rows and columns used in Console Legacy Console Redirection Redirection for legacy OS support.

- Page 45 Parameter Description Flow Control Š – Flow control can prevent data loss from buffer overflow. When sending data, if the receiving buffers are full, a 'stop' signal can Serial Port for Out-of-Band be sent to stop the data flow. Once the buffers are empty, a 'start' EMS Console Redirection signal can be sent to re-start the flow. Hardware flow control uses Settings(continued) two wires to send start/stop signals. – Options available: None, Hardware RTS/CTS, Software Xon/Xoff. Default setting is None.

-

Page 46: Cpu Configuration

2-2-6 CPU Configuration Description Parameter Enable/Disable the CPU Virtualization. SVM Mode Options available: Enabled, Disabled. Default setting is Enabled. Controls the Secure Memory Encryption Enable (SMEE) function. SMEE Options available: Enabled, Disabled. Default setting is Enabled. Press [Enter] to view the memory information related to CPU 0/1. CPU 0/1 Information BIOS Setup - 46 -... -

Page 47: Ami Graphic Output Protocol Policy

2-2-7 AMI Graphic Output Protocol Policy Description Parameter Selects Monitor Output by Graphic Output Protocol. Output Select - 47 - BIOS Setup... -

Page 48: Pci Subsystem Settings

2-2-8 PCI Subsystem Settings BIOS Setup - 48 -... - Page 49 Description Parameter Displays the PCI Bus Driver version information. PCI Bus Driver Version Change the PCIe lanes. PCIE_# Lanes Configuration Options available: Disabled, Auto, x8, x4x4, x16, x8x8, x8x4x4, (Note1) x4x4x8, x4x4x4x4. Default setting is Auto. When enabled, this setting will initialize the device expansion ROM PCI Express Slot # I/O ROM for the related PCI-E slot.

-

Page 50: Usb Configuration

2-2-9 USB Configuration Parameter Description USB Configuration USB Module Version Displays the USB module version information. USB Controllers Displays the supported USB controllers. USB Devices: Displays the USB devices connected to the system. Enable/Disable the Legacy USB support function. AUTO option disables legacy support if no USB devices are connected. - Page 51 Parameter Description Enables the I/O port 60h/64h emulation support. This should be enabled for the complete USB Keyboard Legacy support for non- Port 60/64 Emulation USB aware OS. Options available: Enabled, Disabled. Default setting is Enabled. USB hardware delays and time-outs Selects the time-out value for USB Control/Bulk/Interrupt transfers.

-

Page 52: Network Stack Configuration

2-2-10 Network Stack Configuration Parameter Description Enable/Disable the UEFI network stack. Network Stack Options available: Enabled, Disabled. Default setting is Enabled. Enable/Disable the Ipv4 PXE feature. Ipv4 PXE Support (Note) Options available: Enabled, Disabled. Default setting is Enabled. Enable/Disable the Ipv4 HTTP feature. Ipv4 HTTP Support (Note) Options available: Enabled, Disabled. -

Page 53: Nvme Configuration

2-2-11 NVMe Configuration Parameter Description NVMe Configuration Displays the NVMe devices connected to the system. BIOS Setup - 53 -... -

Page 54: Sata Configuration

2-2-12 SATA Configuration Parameter Description Displays the installed HDD devices information. System will automatically SATA Configuration detect HDD type. - 54 - BIOS Setup... -

Page 55: Uefi Post Logo Configuration

2-2-13 UEFI POST LOGO Configuration Parameter Description Selects output device type. Output Device Type Options available: First loaded Device, Onboard Device, External Device, Specific Device. Default setting is Onboard Device. BIOS Setup - 55 -... -

Page 56: T1S Auth Configuration

2-2-14 T1s Auth Configuration Parameter Description Press [Enter] for configuration of advanced items. Enroll Cert Š – Press [Enter] to enroll a certificate • Enroll Cert Using File • Cert GUID Server CA Configuration Input digit character in 1111111-2222-3333-4444-1234567890ab format. – Commit Changes and Exit – Discard Changes and Exit Delete Cert Š Press [Enter] for configuration of advanced items. Client Cert Configuration - 56 - BIOS Setup... -

Page 57: Amd Mem Configuration Status

2-2-15 AMD Mem Configuration Status Description Parameter Press [Enter] to view the memory configuration status related to CPU 0/1. CPU0/1 BIOS Setup - 57 -... -

Page 58: Iscsi Configuration

2-2-16 iSCSI Configuration Parameter Description Press [Enter] and name iSCSI Initiator. Only IQN format is accepted. iSCSI Initiator Name Range: from 4 to 223 Add an Attempt Press [Enter] to configure advanced items. Delete Attempts Press [Enter] to configure advanced items. Change Attempt Order Press [Enter] to configure advanced items. - 58 - BIOS Setup... -

Page 59: Vlan Configuration

2-2-17 VLAN Configuration BIOS Setup - 59 -... - Page 60 Parameter Description Press [Enter] to configure advanced items. Create new VLAN Š VLAN ID Š – Sets VLAN ID for a new VLAN or an existing VLAN. – Press the <+> / <-> keys to increase or decrease the desired values. – The valid range is from 0 to 4094. Priority Š...

-

Page 61: Mac Ipv4 Network Configuration

2-2-18 MAC IPv4 Network Configuration Parameter Description Indicates whether network address is configured successfully or not. Configured Options available: Enabled, Disabled. Default setting is Disabled. Options available: Enabled, Disabled. Default setting is Enabled. Enable DHCP (Note) Local IP Address Press [Enter] to configure local IP address. (Note) Press [Enter] to configure local NetMask. Local NetMask (Note) Press [Enter] to configure local Gateway Local Gateway (Note) Press [Enter] to configure local DNS servers Local DNS Servers... -

Page 62: Mac Ipv6 Network Configuration

2-2-19 MAC IPv6 Network Configuration - 62 - BIOS Setup... - Page 63 Parameter Description Press [Enter] to configure advanced items. Displays the MAC Address information. Š Interface ID Š – The 64 bit alternative interface ID for the device. The string is colon separated. e.g. ff:dd:88:66:cc:1:2:3. DAD Transmit Count Š – The number of consecutive Neighbor solicitation messages sent Enter Configuration Menu while performing Duplicate Address Detection on a tentative address.

-

Page 64: Broadcom Network Connection

2-2-20 Broadcom Network Connection MZ01-CE0 (Broadcom BCM57416 10GBASE-T Ethernet) MZ01-CE1 (Broadcom BCM5720 Gigabit Ethernet) - 64 - BIOS Setup... - Page 65 Parameter Description Press [Enter] to view firmware image information. Firmware Image Menu Press [Enter] to configure advanced items. Multi-Function Mode Š – Configures the NIC Hardware Mode. – Options available: SF, NPAR 1.0. Default setting is SF. Number of VFs Per PF Š – Configures the number of Virtual Functions Per Physical Function in multiples of 8 (1-128). This field is only applicable when SR-IOV is enabled. – Default setting is 8. SR-IOV Š – Enable/Disable Single Root I/O Virtualization. –...

- Page 66 Description Parameter Default EVB Mode Š – Configures the default Edge Virtual Bridging mode. – Options available: VEB, VEPA, None. Default setting is VEB. Enable PME Capability Š Device Configuration Menu – Enable/Disable PME Capability support. (continued) – Options available: Enabled, Disabled. Default setting is Disabled. Open Virtual Switch Š...

- Page 67 Parameter Description Boot Retry Count Š – Selects the number of boot retries. MBA Configuration Menu – Options available: No Retry, 1 Retry, 2 Retries, 3 Retries, 4 Retries, (continued) 5 Retries, 6 Retries, Indefinite Retries. Default setting is No Retry. iSCSI Boot Configuration Press [Enter] to configure advanced items. Menu Identifies the physical network port by blinking the associated LED. Blink LEDs Press the numeric keys to adjust desired values. Specifies the link status of the port. Link Status Displays the technical specifications for the Network Interface Controller.

- Page 68 2-2-20-1 iSCSI Boot Configuration Menu Parameter Description Press [Enter] to configure advanced items. TCP/IP Parameters via DHCP Š – Acquires TCP/IP Parameters via DHCP. – Options available: Enabled, Disabled. Default setting is Enabled. IP Autoconfiguration Š – Auto-configures the IP configuration. – Options available: Enabled, Disabled. Default setting is Enabled. –...

- Page 69 Description Parameter Link up Delay Time Š – Configures the link up delay time in seconds (0-225). Use TCP Timestamp Š – Enable/Disable the TCP timestamp. – Options available: Enabled, Disabled. Default setting is Disabled. Target as First HDD Š – Enable/Disable target appears as first hard disk drive (HDD) in the system. iSCSI General Parameters – Options available: Enabled, Disabled. Default setting is Disabled. (continued) LUN Busy Retry Count Š...

- Page 70 Description Parameter Press [Enter] to configure advanced items. Connect Š – Enable/Disable the target establishment. – Options available: Enabled, Disabled. Default setting is Disabled. IP Address Š – Configures the Target IP address. TCP Port Š – Configures the Target TCP port number (1-65535). Boot LUN iSCSI First/Second Target Š – Configures the Target boot LUN number (0-255). Parameters iSCSI Name Š...

-

Page 71: Amd Cbs Menu

AMD CBS Menu AMD CBS menu displays submenu options for configuring the CPU-related information that the BIOS automatically sets. Select a submenu item, then press [Enter] to access the related submenu screen. BIOS Setup - 71 -... -

Page 72: Cpu Common Options

2-3-1 CPU Common Options Parameter Description CPU Common Options Performance Press [Enter] for configuration of advanced items. Prefetcher settings Press [Enter] for configuration of advanced items. Core Watchdog Press [Enter] for configuration of advanced items. From a workaround for GCC/C000005 issue for XV Core on CZ A0, setting MSRC001_1029 Decode Configuration (DE_CFG) bit 14 RedirectForReturnDis [DecfgNoRdrctForReturns] to 1. Options available: Auto , 1, 0. Default setting is Auto. Enable/Disable PFEH, cloak individual banks, and mask deferred error Platform First Error Handling interrupts from each bank. - Page 73 Parameter Description SEV-ES ASID Space Limit Space limit control for SEV-ES ASIDs. Control Options available: Auto, Manual. Default setting is Auto. Enable/Disable the Streaming Stores functionality. Streaming Stores Control Options available: Auto, Enabled, Disabled. Default setting is Auto. Sets the Local APIC Mode. Local APIC Mode Options available: Auto, xAPIC, x2APIC.

- Page 74 2-3-1-1 Performance Parameter Description Performance Allows you to accept or decline enabling Custom Core Pstates. When Custom Core Pstates accepted, you can disable or customize core pstates. Allows you to accept or decline enabling CCDs, processor cores and threads. When accepted, you can control the number of CCDs to be used, the number of cores to be used, and whether to enable or disable Symmetric Multithreading Technology (SMT) support.

- Page 75 2-3-1-2 Prefetcher Settings Parameter Description Prefetcher settings Enable/Disable L1 Stream HW Prefetcher. L1 Stream HW Prefetcher Options available: Auto, Enable, Disable. Default setting is Auto. Enable/Disable L2 Stream HW Prefetcher. L2 Stream HW Prefetcher Options available: Auto, Enable, Disable. Default setting is Auto. BIOS Setup - 75 -...

- Page 76 2-3-1-3 Core Watchdog Parameter Description Core Watchdog Enable/Disable CPU Watchdog Timer. Core Watchdog Timer Enable Options available: Auto, Enabled, Disabled. Default setting is Auto. - 76 - BIOS Setup...

-

Page 77: Df Common Options

2-3-2 DF Common Options Parameter Description DF Common Options Scrubber Press [Enter] for configuration of advanced items. Memory Addressing Press [Enter] for configuration of advanced items. ACPI Press [Enter] for configuration of advanced items. Link Press [Enter] for configuration of advanced items. Enable/Disable SyncFlood to UMC & downstream slaves. Disable DF to external IP Options available: Auto, Sync flood disabled, Sync flood enabled. sync flood propagation Default setting is Auto. Enable/Disable DF Sync Flood propagation. Disable DF sync flood Options available: Auto, Sync flood disabled, Sync flood enabled. - Page 78 2-3-2-1 Scrubber Parameter Description Scrubber Provide a value that is the number of hours to scrub memory. DRAM scrub time Options available: Auto, Disabled, 1 hour, 4 hours, 8 hours, 16 hours, 24 hours, 48 hours. Default setting is Auto. Enable/Disable the Poison scrubber control feature.

- Page 79 2-3-2-2 Memory Addressing Parameter Description Memory Addressing Specifies the number of desired NUMA nodes per socket. NUMA nodes per socket Options available: Auto, NPS0, NPS1, NPS2, NPS4. Default setting is Auto. Enable/Disable the Memory interleaving feature. Memory interleaving Options available: Auto, Disabled. Default setting is Auto. Controls the memory interleaving size. This determines the starting address of Memory interleaving size the interleave (bit 8, 9, 10 or 11).

- Page 80 2-3-2-3 ACPI Parameter Description ACPI ACPI SRAT L3 Cache As Enable/Disable report each L3 cache as a NUMA Domain to the OS. NUMA Domain Options available: Auto, Enabled, Disabled. Default setting is Auto. Determines how the SLIT distances are declared. ACPI SLIT Distance Control Options available: Auto, Manual.

- Page 81 2-3-2-4 Link Parameter Description Link Enable/Disable GMI link encryption. GMI encryption control Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable xGMI link encryption. xGMI encryption control Options available: Auto, Enabled, Disabled. Default setting is Auto. CAKE CRC perf bounds Options available: Auto, Manual.

-

Page 82: Umc Common Options

2-3-3 UMC Common Options Parameter Description UMC Common Options DDR4 Common Options Press [Enter] for configuration of advanced items. DRAM Memory Mapping Press [Enter] for configuration of advanced items. NVDIMM Press [Enter] for configuration of advanced items. Memory MBIST Press [Enter] for configuration of advanced items. - 82 - BIOS Setup... - Page 83 2-3-3-1 DDR4 Common Options Parameter Description DDR4 Common Options Press [Enter] to configure the Plan of Record (POR) to enable / disable Enforce POR restrictions for DDR4 frequency and voltage programming. Memory speeds will be capped at AMD guidelines. DRAM Controller Configuration Press [Enter] to configure DRAM Controller Configuration. CAD Bus Configuration Press [Enter] to configure CAD Bus Configuration.

- Page 84 2-3-3-1-1 DRAM Controller Configuration Parameter Description DRAM Controller Configuration Press [Enter] to configure DRAM Power Options. Power Down Enable Š – Enable/Disable DDR power down mode. – Options available: Auto, Enabled, Disabled. Default setting is Auto. SubUrgRefLowerBound Š – Specifies the stored refresh limit to required enter sub-urgent refresh mode. (Valid value: 6~1) UrgRefLimit Š – Specifies the stored refresh limit to required enter urgent refresh DRAM Power Options mode.

- Page 85 2-3-3-1-2 CAD Bus Configuration Parameter Description CAD Bus Configuration Setup time on CAD bus signals to Auto or Manual. CAD Bus Timing User Controls Options available: Auto, Manual. Default setting is Auto. CAD Bus Drive Strength User Drive Strength on CAD bus signals to Auto or Manual. Controls Options available: Auto, Manual.

- Page 86 2-3-3-1-3 Data Bus Configuration Parameter Description Data Bus Configuration Data Bus Configuration User Specifies the mode for drive strength to Auto or Manual. Options available: Auto, Manual. Default setting is Auto. Controls - 86 - BIOS Setup...

- Page 87 2-3-3-1-4 Common RAS Parameter Description Common RAS Enable/Disable the Data Poisoning function. Data Poisoning Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable the DRAM Post Package Repair function. DRAM Post Package Repair Options available: Enabled, Disabled. Default setting is Disabled. Enable/Disable the RCD Parity function.

- Page 88 Parameter Description Disable Memory Error Injection Options available: False, True. Default setting is True. Press [Enter] to configure advanced items. DRAM ECC Symbol Size Š – Configures the DRAM ECC Symbol Size. – Options available: Auto, x4, x8, x16. Default setting is Auto. DRAM ECC Enable Š – Enable/Disable DRAM ECC. When set to Auto, it will set ECC ECC Configuration to enable.

- Page 89 2-3-3-1-5 Security Parameter Description Security Enable/Disable transparent secure memory encryption. TSME Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable Data Scrambling. Data Scramble Options available: Auto, Enabled, Disabled. Default setting is Auto. BIOS Setup - 89 -...

- Page 90 2-3-3-2 DRAM Memory Mapping Parameter Description DRAM Memory Mapping Interleave memory blocks across the DRAM chip selects for node 0. Chipselect Interleaving Options available: Auto, Disabled. Default setting is Auto. Configures the BankGroupSwap. BankGroupSwap (BGS) is a new memory mapping option in AGESA that alters how applications get assigned to BankGroupSwap physical locations within the memory modules.

- Page 91 2-3-3-3 NVDIMM Parameter Description NVDIMM Displays the information of the devices/controllers if installed Disable NVDIMM-N Enable/Disable NVDIMM-N feature for memory margin tool. Feature Options available: No, Yes. Default setting is NO. BIOS Setup - 91 -...

- Page 92 2-3-3-4 Memory MBIST Parameter Description Memory MBIST Enable/Disable the Memory MBIST function. MBIST Enable Options available: Enabled, Disabled. Default setting is Disabled. Selects MBIST Test Mode. Interface Mode: Tests Single and Multiple CS transactions and Basic Connectivity. MBIST Test Mode (Note) Data Eye Mode: Measures Voltage vs.

- Page 93 2-3-3-4-1 Data Eye Parameter Description Data Eye Pattern Select Options available: PRBS, SSO, Both. Default setting is PRBS. Pattern Length Determines the pattern length. The possible options are N=3..12. This item helps read the aggressors channels. Aggressor Channel Options available: Disabled, 1 Aggressor Channel, 3 Aggressor Channels, 7 Aggressor Channels.

- Page 94 Parameter Description Target Static Lane Select This item is configurable when Target Static Lane Control is set to Upper 32 bits Enabled. Target Static Lane Select This item is configurable when Target Static Lane Control is set to Lower 32 bits Enabled. Target Static Lane Select This item is configurable when Target Static Lane Control is set to Enabled.

-

Page 95: Nbio Common Options

2-3-4 NBIO Common Options Parameter Description NBIO Common Options Enable/Disable the IOMMU function. IOMMU Options available: Enabled, Disabled. Default setting is Disabled. Enable/Disable Alternative Routing-ID Interpretation. PCIe ARI Support Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable PCIe ten bit tags for supported devices. (Auto=Disabled) PCIe Ten Bit Tag Support Options available: Auto, Enabled, Disabled. - Page 96 Parameter Description Controls the Hot Plug Handling mode. Options available: Auto, A0 Mode, OS First (No Error Handling), Hot Plug Handling mode OS First (Error Handling-Not Implemented), Firmware First (Not Implemented). Default setting is Auto. Presence Detect Select Controls the Presence Detect Select mode. Options available: Auto, OR, AND.

- Page 97 2-3-4-1 SMU Common Options Parameter Description SMU Common Options Power Policy Quick Options available: Standard, Best Performance, Energy Efficient. Setting Default setting is Standard. Selects use the fused Determinism or set customized Determinism. Determinism Control Options available: Auto, Manual. Default setting is Auto. Selects use the fused TDP or set customized TDP. **TDP is used to define the cTDP Control RC thermal model only** Options available: Auto, Manual.

- Page 98 Parameter Description Enable/Disable the CPPC feature. CPPC Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable the HSMP support. HSMP Support Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable the Diagnostic Mode. Diagnostic Mode Options available: Auto, Enabled, Disabled. Default setting is Auto. Enable/Disable the DLWM support.

- Page 99 2-3-4-2 NBIO RAS Common Options Parameter Description NBIO RAS Common Options NBIO RAS Global Control Options available: Auto, Manual. Default setting is Auto. Options available: Disabled, MCA, Legacy. Default setting is MCA. NBIO RAS Control Configures the Egress Poison High Severity. Each bit set to 1 enables Egress Poison Severity High High severity on the associated IOHC egress port.

- Page 100 Parameter Description Uncorrected Converted to Enables mask for masking of uncorrectable parity errors on internal Poison Enable Mask High arrays. Uncorrected Converted to Enables mask for masking of uncorrectable parity errors on internal Poison Enable Mask Low arrays. Specifies the timer interval of the SYSHUB Watchdog timer in System Hub Watchdog Timer milliseconds.

-

Page 101: Fch Common Options

2-3-5 FCH Common Options Parameter Description FCH Common Options AC Power Loss Options Press [Enter] for configuration of advanced items. FCH RAS Options Press [Enter] for configuration of advanced items. Miscellaneous Options BIOS Setup - 101 -... - Page 102 2-3-5-1 AC Power Loss Options Parameter Description AC Power Loss Options Selects the AC Loss Control Method. AC Loss Control Options available: Power Off, Power On, Last State. Default setting is Last State. - 102 - BIOS Setup...

- Page 103 2-3-5-2 FCH RAS Options Parameter Description FCH RAS Options Enable/Disable the ALink RAS Support. ALink RAS Support Options available: Auto, Enabled, Disabled. Default setting is Auto. Enables AB to forward downstream sync-flood message to system Reset after sync flood controller. Options available: Auto, Enabled, Disabled. Default setting is Auto. BIOS Setup - 103 -...

- Page 104 2-3-5-3 Miscellaneous Options Parameter Description Miscellaneous Options Enable/Disable the Boot Timer. Boot Timer Enable Options available: Auto, Enabled, Disabled. Default setting is Auto. - 104 - BIOS Setup...

-

Page 105: Ntb Common Options

2-3-6 NTB Common Options Parameter Description NTB Common Options NTB Enable Options available: Auto, Enabled. Default setting is Auto. BIOS Setup - 105 -... -

Page 106: Soc Miscellaneous Control

2-3-7 SOC Miscellaneous Control Parameter Description SOC Miscellaneous Control Enable/Disable the Console Out function for ABL. ABL Console Out Control Options available: Auto, Enable, Disable. Default setting is Auto. ABL Basic Console Out Enable/Disable the Basic Console Out function for ABL. Options available: Auto, Enable, Disable. -

Page 107: Amd Pbs Menu

AMD PBS Menu AMD PBS Option menu displays submenu options for configuring the function of AMD PBS. Select a submenu item, then press [Enter] to access the related submenu screen. Parameter Description Press [Enter] for configuration of advanced items. Enable/Disable SPI Locking for protect ROM part. SPI Locking Options available: Enabled, Disabled. -

Page 108: Ras

2-4-1 RAS Parameter Description Enable/Disable the Periodic SMI for polling [MCA Threshold] error. RAS Periodic SMI Control Options available: Enabled, Disabled. Default setting is Enabled. SMI Threshold Configures the SMI Threshold value. SMI Scale Configures the SMI Scale value. Defines the unit of time scale. SMI Scale Unit Options available: millisecond, second, minute. Default setting is millisecond. - Page 109 Parameter Description PCIe Root Port UnCorr Err Initialize the PCIe AER Uncorrected Error Mask register of Root Port. Mask Reg PCIe Root Port UnCorr Err Initialize the PCIe AER Uncorrected Error Severity register of Root Port. Sev Reg PCIe Device Corr Err Mask Initialize the PCIe AER Corrected Error Mask register of PCIe device.

-

Page 110: Chipset Setup Menu

Chipset Setup Menu Chipset Setup menu displays submenu options for configuring the function of the North Bridge. Select a submenu item, then press <Enter> to access the related submenu screen. Parameter Description Configures the PCIe Link training in 1 or 2 steps. PCIe Link Training Type Options available: 1 Step, 2 Step. Default setting is 1 Step. Options available: On, Off. Default setting is Off. PCIe Compliance Mode Enable/Disable program all VR on MB. -

Page 111: North Bridge

2-5-1 North Bridge Parameter Description North Bridge Configuration Memory Information Total Memory Displays the total memory information. CPU0/1 Information Press [Enter] to view information related to CPU 0/1. BIOS Setup - 111 -... -

Page 112: Server Management Menu

Server Management Menu Parameter Description Enable/Disable FRB-2 timer (POST timer). FRB-2 Timer Options available: Enabled, Disabled. Default setting is Enabled. Configures the FRB2 Timer timeout. FRB-2 Timer Options available: 3 minutes, 4 minutes, 5 minutes, 6 minutes. Default setting is 6 timeout minutes. Please note that this item is configurable when FRB-2 Timer is set to Enabled. Configures the FRB2 Timer policy. - Page 113 Parameter Description System Event Log Press [Enter] to configure advanced items. View FRU Press [Enter] to view the FRU information. Information BMC network Press [Enter] to configure advanced items. configuration IPv6 BMC Network Press [Enter] to configure advanced items. Configuration BIOS Setup - 113 -...

-

Page 114: System Event Log

2-6-1 System Event Log Parameter Description Enabling / Disabling Options Change this item to enable or disable all features of System Event SEL Components Logging during boot. Options available: Enabled, Disabled. Default setting is Enabled. Erasing Settings Choose options for erasing SEL. Erase SEL Options available: No/Yes, On next reset/Yes, On every reset. -

Page 115: View Fru Information

2-6-2 View FRU Information The FRU page is a simple display page for basic system ID information, as well as System product information. Items on this window are non-configurable. (Note) The model name will vary depends on the product you purchased BIOS Setup - 115 -... -

Page 116: Bmc Network Configuration

2-6-3 BMC Network Configuration Parameter Description BMC network configuration Lan Channel 1 Selects to configure LAN channel parameters statically or dynamically (DHCP). Do nothing option will not modify any BMC network parameters Configuration Address source during BIOS phase. Options available: Unspecified, Static, DynamicBmcDhcp. Default setting is DynamicBmcDhcp. Station IP address Displays IP Address information. Displays Subnet Mask information. Subnet mask Please note that the IP address must be in three digitals, for example, 192.168.000.001. -

Page 117: Ipv6 Bmc Network Configuration

2-6-4 IPv6 BMC Network Configuration Parameter Description IPv6 BMC network configuration IPv6 BMC Lan Channel 1 Enable/Disable IPv6 BMC LAN channel function. When this item is disabled, the system will not modify any BMC network during BIOS IPv6 BMC Lan Option phase. Options available: Unspecified, Disable, Enable. Default setting is Enable. -

Page 118: Security Menu

Security Menu The Security menu allows you to safeguard and protect the system from unauthorized use by setting up access passwords. There are two types of passwords that you can set: • Administrator Password Entering this password will allow the user to access and change all settings in the Setup Utility. •... -

Page 119: Secure Boot

2-7-1 Secure Boot The Secure Boot submenu is applicable when your device is installed the Windows 8 (or above) operating ® system. Parameter Description System Mode Displays if the system is in User mode or Setup mode. Enable/ Disable the Secure Boot function. Secure Boot Options available: Enabled, Disabled. - Page 120 Parameter Description Press [Enter] to configure advanced items. Please note that this item is configurable when Secure Boot Mode is set to Custom. Factory Key Provision Š – Allows to provision factory default Secure Boot keys when system is in Setup Mode. – Options available: Enabled, Disabled. Default setting is Disabled. Restore Factory Keys Š...

-

Page 121: Boot Menu

Boot Menu The Boot menu allows you to set the drive priority during system boot-up. BIOS setup will display an error message if the legacy drive(s) specified is not bootable. Parameter Description Boot Configuration Number of seconds to wait for setup activation key. 65535 (0xFFFF) Setup Prompt Timeout means indefinite waiting. Press the numeric keys to input the desired values. - Page 122 Parameter Description FIXED BOOT ORDER Priorities Press [Enter] to configure the boot priority. By default, the server searches for boot devices in the following sequence: Hard drive. Boot Option #1 / #2 / #3 / #4 / #5 CD-COM/DVD drive. USB device. Network. UEFI. UEFI Network Drive BBS Press [Enter] to configure the boot priority.

-

Page 123: Save & Exit Menu

Save & Exit Menu The Save & Exit menu displays the various options to quit from the BIOS setup. Highlight any of the exit options then press <Enter>. Parameter Description Save Options Saves changes made and closes the BIOS setup. Save Changes and Exit Options available: Yes, No. -

Page 124: Abl Post Codes

2-10 ABL POST Codes 2-10-1 StartProcessorTestPoints Entry used for range testing for @b Processor related TPs 0xE000 2-10-2 Memory test points Memory structure initialization (Public interface) 0xE001 SPD Data processing (Public interface) 0xE002 Memory configuration (Public interface) Phase 1 0xE003 DRAM initialization 0xE004 ProcMemSPDChecking 0xE005 ProcMemModeChecking 0xE006 Speed and TCL configuration... -

Page 125: Original Post Code

ABL Mem - PMU Stage Training Wr 2D 0xE023 ABL Mem - PMU Queue Empty 0xE024 ABL Mem - PMU US message Start 0xE025 ABL Mem - PMU US message End 0xE026 ABL Mem - PMU Complete 0xE027 ABL Mem - PMU - After PMU Training 0xE028 ABL Mem - PMU - Before Disable PMU 0xE029... -

Page 126: Cpu Test Points

ABL Mem - Before OtherTiming 0xE04A ABL Mem - Before UMAMemTyping 0xE04B ABL Mem - Before SetDqsEccTmgs 0xE04C ABL Mem - Before MemClr 0xE04D ABL Mem - Before On DIMM Thermal 0xE04E ABL Mem - Before DMI 0xE04F ABL MEM - End of phase 3 memory code 0xE050 2-10-5 CPU test points Entry point CPU init after training... -

Page 127: Gnb Earlier Init

2-10-8 Gnb Earlier init TP0x90 0xE090 GNB earlier interface 0xE091 GNB internal debug code 0xE092 GNB internal debug code 0xE093 GNB internal debug code 0xE094 GNB internal debug code 0xE095 GNB internal debug code 0xE096 GNB internal debug code 0xE097 GNB internal debug code 0xE098 GNB internal debug code... - Page 128 ABL 2 Begin 0xE0B8 ABL 2 Initialization 0xE0B9 ABL 2 After Training 0xE0BA ABL 2 Debug Synchronization 0xE0BB ABL 2 Error detected 0xE0BC ABL 2 Global memory error detected 0xE0BD ABL 2 End 0xE0BE ABL 3 Begin 0xE0BF ABL 3 Initialziation 0xE0C0 ABL 3 GMI/xGMI Initialization Stage 1 0xB1C0...

- Page 129 ABL 4 APOB Initialzation - cold boot 0xE0CA ABL 4 Finalize memory settings - cold boot 0xE0CB ABL 4 CPU Initialize Optimized Boot - cold boot 0xE0CC ABL 4 Gmi Pcie Training - cold boot 0xE0CD ABL 4 Cold boot End 0xE0CE ABL 4 Initialization - Resume boot 0xE0CF...

-

Page 130: Pmu Test Points

Before the memory code calls out to locate a buffer 0xE0F3 After the memory code calls out to locate a buffer 0xE0F4 Before the memory code calls out to locate a buffer 0xE0F5 After the memory code calls out to locate a buffer 0xE0F6 Before the memory code calls out to locate a buffer 0xE0F7... - Page 131 ABL Error for Soc Scan No Die error 0xE2AC ABL Error for Nb Tech Heap Aloc error 0xE2AD ABL Error for No Nb Constructor error 0xE2AE ABL Error for No Tech Constructor error 0xE2AE ABL Error for ABL1b Auto Alocation error 0xE2B0 ABL Error for ABL1b No NB Constructor error 0xE2B1...

- Page 132 ABL Error over clock Mem Init Error 0xE2D5 ABL Error over clock Mem Other Error 0xE2D6 ABL Error for ABL6 General Error 0xE2D7 ABL Error Event Log Error 0xE2D8 ABL Error FATAL ABL1 Log Error 0xE2D9 ABL Error FATAL ABL2 Log Error 0xE2DA ABL Error FATAL ABL3 Log Error 0xE2DB...

- Page 133 ABL Error ABL 2 Mem Init Error 0xE302 ABL Error ABL 4 Mem Init Error 0xE303 ABL Error ABL 6 Mem Init Error 0xE304 ABL Error ABL 1 error repor Error 0xE305 ABL Error ABL 2 error repor Error 0xE306 ABL Error ABL 3 error repor Error 0xE307 ABL Error ABL 4 error repor Error...

-

Page 134: Agesa Post Codes

2-11 Agesa POST Codes 2-11-1 Universal Post Code Universal ACPI entry 0xA001 Universal ACPI exit 0xA002 Universal ACPI abort 0xA003 Universal SMBIOS entry 0xA004 Universal SMBIOS exit 0xA005 Universal SMBIOS abort 0xA006 2-11-2 [0xA1XX] For CZ only memory Postcodes Memory structure initialization (Public interface) 0xA101 SPD Data processing (Public interface) 0xA102... - Page 135 Calculate MaxRdLatency per channel 0xA120 TpProcMemReceiveDqsTraining 0xA121 Set Write Data delay 0xA122 Write test pattern 0xA123 Start read sweep 0xA124 Set Receive DQS delay 0xA125 Read Test pattern 0xA126 Compare Test pattern 0xA127 Update results 0xA128 Start Find passing window 0xA129 TpProcMemTransmitDqsTraining 0xA12A...

- Page 136 Before InitMCT 0xA149 Before OtherTiming 0xA14A Before UMAMemTyping 0xA14B Before SetDqsEccTmgs 0xA14C Before MemClr 0xA14D Before On DIMM Thermal 0xA14E Before DMI 0xA14F End of memory code 0xA150 Entry point S3Init 0xA151 Sending MRS2 0xA180 Sedding MRS3 0xA181 Sending MRS1 0xA182 Sending MRS0 0xA183...

-

Page 137: S3 Interface Post Code

BR Init Mid end 0xA19E BR Init Late entry 0xA19F BR Init Late install protocol 0xA1A0 BR Init Late end 0xA1A1 BR DXE install complete protocol 0xA1A2 UNB install complete PPI 0xA1A3 UNB AfterApLaunch callback entry 0xA1A4 UNB AfterApLaunch callback end 0xA1A5 2-11-3 S3 Interface Post Code Before the S3 save code calls out to allocate a buffer... - Page 138 PspSmmV1 SwSmiCallBack exit, build the S3 save area for resume 0xA511 PspSmmV1 BspSmmResumeVector entry 0xA512 PspSmmV1 BspSmmResumeVector exit 0xA513 PspSmmV1 ApSmmResumeVector entry 0xA514 PspSmmV1 ApSmmResumeVector exit 0xA515 PspP2CmboxV1 entry 0xA516 PspP2CmboxV1 exit 0xA517 // PSP V2 Modules PspPeiV2 entry 0xA521 PspPeiV2 exit 0xA522 PspDxeV2 entry...

- Page 139 PspP2Cmbox Command SpiSetAttrib Handling entry 0xA592 PspP2Cmbox Command SpiGetBlockSize Handling entry 0xA593 PspP2Cmbox Command SpiReadFV Handling entry 0xA594 PspP2Cmbox Command SpiWriteFV Handling entry 0xA595 PspP2Cmbox Command SpiEraseFV Handling entry 0xA596 PspP2Cmbox Command Handling exit 0xA59E PspP2Cmbox Command Handling Fail exit 0xA59F // C2P mailbox Handling PSP C2P mailbox entry base [0xA5BX | Cmd]...

-

Page 140: 0Xa9Xx, 0Xaaxx] Assigned For Agesa Nbio Module

2-11-6 [0xA9XX, 0xAAXX] assigned for AGESA NBIO Module // NbioBase AmdNbioBase PEIM driver entry 0xA900 AmdNbioBase PEIM driver exit 0xA901 AmdNbioBase DXE driver entry 0xA902 AmdNbioBase DXE driver exit 0xA903 // PCIe AmdNbioPcie PEIM driver entry 0xA904 AmdNbioPcie PEIM driver exit 0xA905 AmdNbioPcie DXE driver entry 0xA906... - Page 141 // APCB SMM APCB SMM Entry 0xA924 APCB SMM Exit 0xA925 // [0xA950, 0xA99F] NBIO PPI/PROTOCOL Callback NbioTopologyConfigureCallback entry 0xA950 NbioTopologyConfigureCallback exit 0xA951 MemoryConfigDoneCallbackPpi entry 0xA952 MemoryConfigDoneCallbackPpi exit 0xA953 DxioInitializationCallbackPpi entry 0xA954 DxioInitializationCallbackPpi exit 0xA955 DispatchSmuV9Callback entry 0xA956 DispatchSmuV9Callback exit 0xA957 DispatchSmuV10Callback entry 0xA958 DispatchSmuV10Callback exit 0xA959 AmdPcieMiscInit Event entry...

-

Page 142: 0Xacxx] Assigned For Agesa Ccx Module

GfxConfigEnvInterface entry 0xA984 GfxConfigEnvInterface exit 0xA985 GfxEnvInterfaceCZ entry 0xA986 GfxEnvInterfaceCZ exit 0xA987 GfxMidInterfaceCZ entry 0xA988 GfxMidInterfaceCZ exit 0xA989 GfxIntInfoTableInterfaceCZ entry 0xA98A GfxIntInfoTableInterfaceCZ exit 0xA98B PcieMidInterfaceCZ entry 0xA98C PcieMidInterfaceCZ exit 0xA98D GnbMidInterfaceCZ entry 0xA98E GnbMidInterfaceCZ exit 0xA98F GnbSmuMidInterfaceCZ entry 0xA990 GnbSmuMidInterfaceCZ exit 0xA991 InvokeAmdInitLate entry 0xA992 InvokeAmdInitLate exit... -

Page 143: 0Xadxx] Assigned For Agesa Df Module

2-11-8 [0xADXX] assigned for AGESA DF Module DF PEI entry 0xAD50 DF DXE entry 0xAD55 DF Ready to Boot entry 0xAD56 DF PEI exit 0xADE0 DF DXE exit 0xADE5 DF Ready to Boot exit 0xADE6 2-11-9 [0xAFXX] assigned for AGESA FCH Module FCH InitReset dispatch point 0xAF01 FCH InitEnv dispatch point... - Page 144 FCH InitEnv AB Link 0xAF51 FCH InitEnv LPC 0xAF52 FCH InitEnv SPI 0xAF53 FCH InitEnv eSPI 0xAF54 FCH InitEnv SD 0xAF55 FCH InitEnv eMMC 0xAF56 FCH InitEnv SATA 0xAF57 FCH InitEnv USB 0xAF58 FCH InitEnv xGbE 0xAF59 FCH InitEnv HwAcpiP 0xAF5F FCH InitMid HwAcpi 0xAF60...

-

Page 145: Bios Post Beep Code (Ami Standard)

2-12 BIOS POST Beep code (AMI standard) 2-12-1 PEI Beep Codes # of Beeps Description Memory not Installed. Memory was installed twice (InstallPeiMemory routine in PEI Core called twice) Recovery started DXEIPL was not found DXE Core Firmware Volume was not found Recovery failed S3 Resume failed Reset PPI is not available...

Need help?

Do you have a question about the MZ71-CE0 and is the answer not in the manual?

Questions and answers