Compaq Armada e500 Series Reference Manual

Hp armada e500: reference guide

Hide thumbs

Also See for Armada e500 Series:

- Quick reference manual (220 pages) ,

- Reference manual (205 pages) ,

- Maintenance and service manual (162 pages)

Table of Contents

Advertisement

Quick Links

The information in this guide is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR

TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS CONTAINED HEREIN;

NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM

THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL.

This guide contains information protected by copyright. No part of this guide may be

photocopied or reproduced in any form without prior written consent from Compaq

Computer Corporation.

© 2000 Compaq Computer Corporation.

All rights reserved. Printed in, U.S.A., U.K., Singapore, and Taiwan.

Compaq, Armada, and ROMPaq are registered in the U.S. Patent and

Trademark Office.

Microsoft, MS-DOS, Windows, Windows NT, and other names of Microsoft products

mentioned herein are trademarks or registered trademarks of Microsoft Corporation.

Intel, Pentium, and Celeron are trademarks of Intel Corporation. Imation and SuperDisk

are trademarks of Imation Corporation. CardWare is a registered trademark of Unicore

Software, Inc.

All other product names mentioned herein may be trademarks or registered trademarks

of their respective companies.

Software described herein is furnished under a license agreement or nondisclosure

agreement. The software may be used or copied only in accordance with the terms of

the agreement.

First Edition March 2000

Part Number 11QY-0200A-WWEN

Advertisement

Table of Contents

Summary of Contents for Compaq Armada e500 Series

- Page 1 The information in this guide is subject to change without notice. COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS CONTAINED HEREIN; NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL. This guide contains information protected by copyright.

- Page 2 #387046, SMSC MSIO, SMSC37N971, Tikki #290725, Flash ROM,512k x 8, 60ns, 5V #353924, ESS 1920 Audio Codec #258896, Li-Ion Battery Specification Compaq Armada E500 and Armada V300 Maintenance and Service Guide Microsoft Operating System Manual Synaptics Touchpad Interfacing Guide Compaq Web site at http://www.compaq.com...

-

Page 3: Table Of Contents

ONTENTS chapter 1 Standard Features ... 1-2 External Ports/Connectors ... 1-4 Power Management... 1-4 System Architecture ... 1-5 Mechanical ... 1-11 Docking Support ... 1-11 Security Features... 1-12 chapter 2 Host Bus (Northbridge)... 2-1 ISA Bus (Southbridge)... 2-10 Clocks... 2-16 chapter 3 Base System Memory ... - Page 4 chapter 5 8051 Microcontroller ... 5-3 Real-Time Clock and CMOS RAM... 5-4 Diskette Controller... 5-4 Parallel Port... 5-5 GPIO Usage ... 5-6 C Controller ... 5-6 Serial UARTs ... 5-7 Shared Flash ROM Interface ... 5-7 Keyboard Scan ... 5-8 PS/2 Serial Mouse/Keyboard Interfaces ...

- Page 5 Hotkeys ... 8-2 External Keyboard/Mouse Communications... 8-3 chapter 9 DC/DC Converter ... 9-2 Smart Battery ... 9-3 Display Inverter... 9-4 External AC Adapter... 9-4 Power Management Controller ... 9-5 chapter 10 Hard Drive Subsystem ... 10-1 Diskette Drive Subsystem... 10-3 CD-ROM Module ...

- Page 6 appendix A Docking Sequence... A-1 Docking Interface... A-1 appendix B Power Management States ...B-1 Processor Power Management...B-3 Processor Thermal Management...B-4 Secondary Cache Power Management ...B-4 PCI Bus Power Management ...B-4 Video Power Management...B-5 Hard Drive and Bay Power Management ...B-5 MSIO Super I/O Power Management...B-5 Audio Power Management ...B-5 ...I-1...

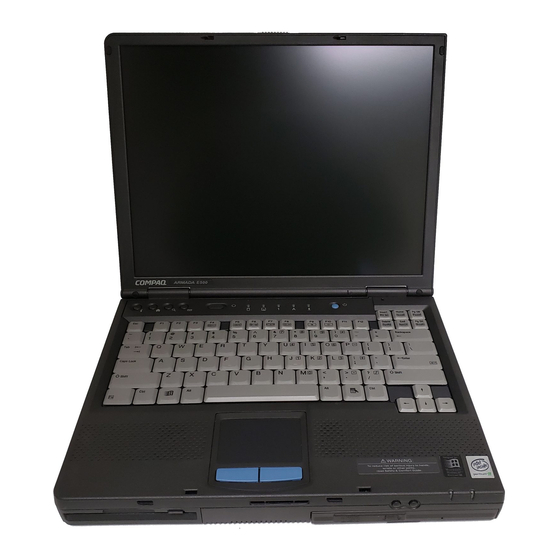

- Page 7 The Compaq Armada E500 and Armada V300 Series offer Intel Mobile Pentium II, III or Celeron Processors with 32-bit or 64-bit architecture, MMX technology, and level-2 cache memory. Both Armada E500 and Armada V300 Series provide desktop functionality and connectivity through optional expansion bases or convenience bases.

- Page 8 Microsoft Windows 95, Window 98 or Windows NT Workstation 4.0 preinstalled The following displays are available, varying by computer model: The Armada E500 features a 15-inch or 14.1-inch, XGA, TFT (1024 × 768) or 12.1-inch, SVGA, TFT (800 × 600) display, both with over 16.8 million colors.

- Page 9 SuperDisk LS-120 drive, 6-cell Li-ion MultiBay battery pack, or secondary hard drive (when used with a Hard Drive MultiBay Adapter). Armada E500 provides a DualBay that accommodates a diskette drive or a second battery pack. Connectors for parallel, serial, audio in/out, external monitor, universal serial bus, external keyboard, and AC power.

- Page 10 Standard 176-pin Armada docking connector Fast IR port One or two CardBus slots with support for Zoomed Video Audio connectors for speaker or headphones out, and microphone in PS/2 port for mouse or external keyboard with support for Y–cable for two devices RJ-11 modem jack with internal connection to modem slot, depending on model RJ-45 Ethernet jack with internal connection to the combination modem/LAN slot, depending on model...

- Page 11 The system architecture is shown in Figure 1-2. Coppermine or 440BX Dixon CPU North Bridge AGP Bus PCI Bus 4/8MB SDRAM PIIX4 Video ATI PCI-IDE Mobility-P South Bridge SVGA LCD Display USB Control PCI-ISA Tikki MSIO Flash ROM PS/2 Keyboard Serial Infrared Parallel...

- Page 12 The ISA bus is connected to: Southbridge chipset (PIIX4M) Flash ROM Super I/O controller (MSIO) Armada E500: 366- or 400-MHz Intel Mobile Pentium II Processor 450-, 500-, or 600-MHz Intel Mobile Pentium III Processor Armada V300: 400- or 466-MHz Intel Celeron Processor with 128-KB integrated L2 cache Support for all Intel Mobile Pentium II and Pentium III Processors Unbuffered and registered SDRAM support (×-1-1-1 access at 66 to 100 MHz)

- Page 13 AGP interface Integrated DRAM controller supports single AGP-66/133 compliant device (3.3 volt) AGP Specification revision 1.0 compliant AGP data/transaction flow optimized arbitration mechanism AGP side–band interface for efficient request pipelining AGP specific data buffering Supports concurrent CPU, AGP, and PCI transactions to main memory AGP high-priority transaction support Advanced power management features Supports Standby (S1), Suspend-to-DRAM (S3), and Suspend-to-Disk (S4)

-

Page 14: Microcontroller

Advanced Power Management support 3.3-volt operation with 5-volt tolerant buffers Power-On Suspend (S1), Suspend-to-DRAM (S3), Suspend-to-Disk (S4), and Soft-Off (S5) System States All registers readable and restorable for proper resume from zero-volt suspend Global and local device management Supports thermal alarm Support for external microcontroller Full support for ACPI revision 1.0 specification and OS directed power management... - Page 15 Video Controller ATI RAGE Mobility-P 32-bit wide memory-mapped registers Advanced Graphics Platform (AGP) 2X bus with sideband support; 133-MHz throughput Floating-Point Setup Engine for high-performance 3D and CAD Motion compensation for full-screen MPEG-2 video without external acceleration hardware 4 or 8-MB, 3.3-volt 125-MHz video SDRAM Support for Zoomed Video Built-in support for LVDS data bus to LCD display Built-in NTSC and PAL video output (composite)

- Page 16 SMC Super I/O Controller SMC FDC37N97X Simultaneous support for three PS/2 ports (1 internal + 2 external) Advanced infrared communications controller ACPI Embedded Controller Interface High-performance, embedded 8051 keyboard and system controller Low Suspend current in sleep mode System power plane control and power sequencing Battery management interface for charging and smart battery fuel gauge Active thermal interface for CPU thermal management 1.44-MB Super I/O FDC controller...

- Page 17 Provides 18.5 volts DC +/- 3.75% at 100 to 240 volts AC 50 watts output 6 or 9-cell Li-ion battery in dedicated bay; only Armada E500 and Armada V300- specific batteries can be inserted into the primary bay due to mechanical keying Size: 9.9-in (252 mm) ×...

- Page 18 One serial port One parallel port, with support for an Armada 4100/7800-compatible diskette drive option (Note: The Armada E500 and Armada V300 do not support this, but the Convenience Base does.) Two PS/2 ports to connect one for an external keyboard and a pointing device...

-

Page 19: Host Bus (Northbridge)

UPPORT Host Bus (Northbridge) The Armada E500 and Armada V300 computers use the Intel Pentium II, Pentium III, and Celeron Processors, respectively. The Pentium Processors feature: 450-, 500-, or 600-MHz CPU with 100-MHz SDRAM bus for PIII, 66MHz for PII... - Page 20 At the higher frequency, a higher voltage must also be run. For the Armada E500, the notebook frequency is 500 MHz at 8 watts, and the desktop frequency is 650 MHz at 14 watts. The high power mode may be operated under battery or AC power, but the battery life will be lower and the acoustic noise higher than operation in the normal notebook mode.

- Page 21 Power Planes The 82440BX supports suspend modes: Power-On-Suspend (POS), Suspend-To-RAM (STR) and Suspend-To-Disk (STD). The 82440BX maintains leakage control so that back powering of other system functions cannot occur in Suspend. Table 2-1 lists the 82440BX power planes. 82440BX Power Planes Plane VCC OPTIONS 3.3 V...

- Page 22 Signal Assert w/ PCIRST# PCIRST# CPURST# Always RSTDRV Always SUSSTAT# INIT# CPURST# is generated by the 82440BX in the following instances: CPURST# is always asserted if PCIRST# is asserted. CPURST# is asserted during resume sequence from POS (CRst_En= 1). The 82440BX de-asserts CPURST# 1 ms after detecting the rising edge of PCIRST#. The CPURST# is synchronous to the host bus clock.

- Page 23 Power-On Configuration The 440BX chipset uses power-on registers to define system configuration variables that must be set by hardware options. All signals used to select power-on options are connected to either internal pull-down or pull-up resistors of minimum 50 K/maximum 150 K ohms.

- Page 24 Clock Interface The 82440BX requires two clock inputs which are CPUCLK (66 or 100 MHz) and PCICLK_440BX (33 MHz). The CPUCLK signal is buffered and driven DCLKOUT. During certain conditions the CPUCLK signals may be stopped and restarted. The CPUCLK can be stopped in the sleep and deep-sleep modes and restarted when a primary activity is detected.

- Page 25 PCI Bus Power Management The PCI Bus Power Management Interface Specification (PCIPM) establishes the infrastructure required to let the operating system control the power of PCI functions. This is done by defining a standard PCI interface and operations to manage the power of PCI functions on the bus.

- Page 26 PIIX4M PCI Functions While the primary function of the PIIX4M is to provide a bridge between the PCI and ISA buses, it also contains PCI devices and control logic. This section defines these PCI functions. Distributed DMA and Serialized IRQ (DDMA) Support Direct Access Memory (DMA) is an open standard that supports legacy devices on the PCI bus.

- Page 27 AGP Bus The 82440BX supports a dedicated 66 MHz Accelerated Graphics Port (AGP) video bus. Like the PCI bus, the AGP bus is a 32-bit, multiplexed address/data bus, but it operates at 66 MHz–full or 2/3-CPU bus speeds, with bursting support into main memory.

-

Page 28: Isa Bus (Southbridge)

ISA Bus (Southbridge) PIIX4M (82371EB) The PIIX4M serves as the Southbridge, providing the following functions: Bridge between the PCI and ISA buses Logic to support master and slave cycles on both PCI and ISA buses Master power management controller for the 440BX chipset Mechanism to generate up to 53 general-purpose I/Os Power Planes The PIIX4M has a flexible power plane structure to support a wide variety of system... - Page 29 The SMM base address is defined as 000D0000H-000EFFFFH. The physical memory space used for SMM memory is at 000A0000H-000BFFFFH in DRAM. SMRAM accesses are always marked as write-through to the L1 cache. SMRAM cannot be accessible by PCI or AGP masters. Power Management Controller The PIIX4M has the following power management functions designed to maximize system battery life:...

- Page 30 General Purpose Input/Output (GPIO) Usage The PIIX4M provides up to 22 general purpose input (GPI) signals. These GPIs can be used to directly monitor system logic and external inputs. The read-only registers that store the state of these inputs are located in the PIIX4. See the 82371AB (PIIX4) design guide and 82371EB (PIIX4M) addendum for further information.

- Page 31 Table 2-6 Continued Signal Description DS1#_5 Driver Selection for 2 MTR1#_5 Motor selection for 2 I2C_DCKEN_3 Enable Expansion I2C interface KBCPURST#_3 Output to PIIX4 for Init generation JOUST_CKEN Expansion clock enable for Joust type docking station FAN_PWM Fan control for thermal INV_PWM_5 PWM for panel brightness Chip select for flash ROM...

- Page 32 Table 2-6 Continued Signal A20GATE_3 IDLE_ARB_3 ARCADE_EN#_3 NUM_LED#_3 SCROLL_LED#_3 RESET_OUT# PWR_LED# BAT_LED# FDD_BAT_LED System Interrupt Map The interrupt usage of a PCI/PnP system can vary considerably and is based on the commands given by the OS during hardware detection and configuration. The following default interrupts are set on the system.

- Page 33 Real-Time Clock The real-time clock (RTC) functions are provided in a special area of the PIIX4M containing low-power CMOS circuitry that keeps the current time and date and a low-power CMOS storage area for system settings. A 32.768-KHz crystal is used to clock and update the time and date.

-

Page 34: Clocks

Super I/O Controller The Super I/O Controller device is the SMC FDC37N97 (MSIO). It integrates a new generation of complete Super I/O functions, plus an enhanced 8051 microcontroller for power management and keyboard control. The MSIO resides on the SUB-ISA bus and includes the following features: 3.3-volt operation with 5-volt tolerant buffers ACPI 1.0 and PC99-compliant... - Page 35 The frequency synthesizer operates in a spread spectrum mode to help reduce EMI emissions. Three buffered 14.381-MHz clock outputs are available. These clocks are used by other components in the system such as the MSIO, Maestro 2E, and PIIX4. It provides two copies of CPU clock, five copies of PCI clock, one copy of free running PCI clock, one copy of Ref.

- Page 36 100-MHz (Armada PIII) SDRAM. Memory is expandable to 512 MB. Both the Armada E500 and Armada V300 computer models support two SODIMM slots and no soldered base memory. One bank will be filled with 32 MB or 64 MB with a 64 bit data path, dependent on the type of computer.

- Page 37 Memory expansion is available through the two DIMM sockets. The DIMMs supported are 144-pin 3.3 volt SO-DIMM. The largest SO-DIMM available is 256 MB. This means that the maximum system memory is 256 MB + 256 MB = 512 MB for Pentium II and Pentium III Processors systems.

- Page 38 The PC Card interface provides system expansion that is transparent to the user through the PC Card slot connectors. The Armada E500 supports two card slots and the Armada V300 supports one slot. Peripherals in the form of PC Cards can be added to the system.

- Page 39 Mix-and-match 5-volt/3.3-volt PC cards and 3.3-volt CardBus cards Support for two PC card or CardBus slots with hot insertion and removal with the Armada E500; only one slot used with the Armada V300 Serial interface to TI TPS2206 dual power switch...

- Page 40 Figure 4-1 shows a simplified system implementation using the PCI1225. The PCI interface includes all address/data and control signals for PCI protocol. Highlighted in this diagram is the functionality supported by the PCI1225. The PCI1225 supports PC/PCI DMA, PCI Way DMA (distributed DMA), PME wake-up from D3 through D0, 4 interrupt modes, a Zoomed Video port, and 12 multifunction pins (8 IRQMUX, and 4 GPIO pins) that can be programmed for a wide variety of functions.

- Page 41 PCI LOCK* indicates an atomic operation that may require multiple transactions to complete. When LOCK* is asserted, nonexclusive transactions may proceed to an address that is not currently locked. A grant to start a transaction on the PCI bus does not guarantee control of LOCK*;...

- Page 42 A power switch with a PCMCIA-to-peripheral control (P2C) interface is required for the PC Card powering interface. The TI TPS2206 Dual-Slot PC Card power-interface switch provides the P2C interface to the CLOCK, DATA, and LATCH terminals of the PCI1225. The Zoomed Video (ZV) port on the PCI1225 provides an externally buffered 16-bit ZV PC Card data path.

- Page 43 The SPKROUT signal carries the digital audio signal from the PC Card to the system. When a 16-bit PC Card is configured for I/O mode, the BVD2 pin becomes SPKR*. This terminal, also used in CardBus applications, is referred to as CAUDIO. SPKR* passes a TTL level digital audio signal to the PCI1225.

- Page 44 The method by which any type of PCI1225 interrupt is communicated to the host interrupt controller varies from system to system. The PCI1225 offers system designers the choice of using parallel PCI interrupt signaling, parallel ISA type IRQ interrupt signaling, or the IRQSER serialized ISA and/or PCI interrupt protocol. Traditional ISA IRQ signaling is provided through eight IRQMUX terminals.

- Page 45 Host software may individually mask or disable most of the potential interrupt sources by setting the appropriate bits in the PCI1225. By individually masking the interrupt sources, software can control which events will cause a PCI1225 interrupt. Host software has some control over which system interrupt the PCI1225 will assert by programming the appropriate routing registers.

- Page 46 Figure 4-3 illustrates the IRQMUX functionality. This illustration describes only the PCREQ/IRQMUX7/SCL signal. System Control Register (Bit 3): When bit 3 = 0 EEPROM SCL is routed on IRQMUX7 When bit 3 = 1 PCREQ is routed on IRQMUX7 EEPROM SCL 0000 0001 PCREQ...

- Page 47 IRQ15, C to IRQ12, B to IRQ11, A to IRQ10, 9 to IRQ9, 5 to IRQ5, 4 to IRQ4, and 3 to IRQ3. The IRQMUX routing register is shared between the two PCI1225 functions, and only one write to function 0 or function 1 is necessary to configure the IRQMUX signals. Parallel PCI interrupts are available when in pure parallel PCI interrupt mode, IRQMUX signaling mode, and when only IRQs are serialized with the IRQSER protocol.

- Page 48 The specific issues addressed by the PCI Bus Interface Specification for PCI-to-CardBus bridges for D3 wake-up are: Preservation of device context: The PCI Power Management Specification version 1.0 states that PRST* must be asserted when transitioning from D3 method to preserve wake-up context must be implemented so that PRST* does not clear the PME* context registers.

- Page 49 There are two methods to clock the power switch interface in the PCI1225: Use an external clock to the PCI1225 CLOCK pin Use the internal oscillator Asynchronous signals, such as card status change interrupts and RI_OUT, can be passed to the host system without a PCI clock. However, if card status change interrupts are routed over the serial interrupt stream, the PCI clock will have to be restarted to pass the interrupt because neither the internal oscillator nor an external clock is routed to the serial interrupt state machine.

- Page 50 RI_OUT Function Card PC Card Socket 0 RICSC(A) RICSC(B) PC Card Card Socket 1 RI_OUT* is multiplexed on the same pin with PME*. The default is for RI_OUT* to be signaled on this pin. In PCI power managed systems, the PME* signal should be enabled by setting bit 0 (RI_OUT*/PME*) in the system control register (80h) and clearing bit 7 (RIENB) in the card control register (91h).

-

Page 51: Diskette Controller

UPER ONTROLLER The FDC37N97X MSIO Super I/O Controller used in the Armada E500 and Armada V300 computers is made by SMC. It integrates a new generation of complete Super I/O functions, plus provides an enhanced 8051 microcontroller for power management and keyboard control. -

Page 52: Controller

VCC1(3) VCC2(4) DIGITAL DATA SEPARATOR VSS(9) WITH WRITE PRECOMPENSATION SYSTEM nRESET_OUT RESET nIOR nIOW nMEMRD nMEMWD nROMCS SMSC PROPRIETARY SA[0:15] #2077 COMPATIBLE SD[0:7] VERTICAL FLOPPY DISK DRQ[0:1] CONTROLLER CORE DRQ[2:3]* nDAC[0:1] HOST INTERFACE nDAC[2:3]* nNOWS IOCHRDY INTERRUPTS CONFIGURATION nlRBQ* REGISTERS nSMI* SER_IRQ nCLKRUN... - Page 53 The MSIO device integrated a high performance 8051 embedded controller compatible with the industry standard 80C51 microcontroller. The high performance 8051 features include: Keyboard controller providing 2 kB of internal ROM, 256 bytes of RAM; a 512 KB of Flash ROM interface; support four PS/2-type pointing device/keyboard interfaces; a real-time clock;...

- Page 54 The host can no longer access the shared ROM once this happens, since the 8051 owns the interface and executes from the ROM. The real-time clock (RTC) and CMOS RAM in the MSIO are not utilized in the Armada E500 and Armada V300 computers.

- Page 55 The 82077AA-compatible diskette controller (FDC) provides the interface between the computer and the diskette drive. The FDC integrates the functions of the formatter/controller, digital data separator, write precompensation, and data rate selection logic for an IBM XT/AT-compatible FDC. Moreover, the MSIO Super I/O controller implements Write protect function, shown in Figure 5-3.

- Page 56 The MSIO Super I/O Controller provides eight general-purpose input pins, 12 general purpose-outputs, and 22 general-purpose I/O pins. Improvements on these pins are made for system management flexibility. The GPIO pins, shown in Figure 5-5, are controlled by the 8051, so that host access to them are through the mailbox registers. GPIO DIR BIT ALT FUNC Control bit...

- Page 57 Two 16550A-compatible UARTS are provided in the MSIO. They can be mapped to any of the standard legacy I/O addresses and interrupts. UART-A is dedicated to the RS-232 transceiver and serial connector on the back of the unit. UART-B interfaces internally to an IrDA-compliant infrared encode/decoder and an IrDA module for serial infrared communications.

- Page 58 All four interfaces can operate simultaneously if supported by 8051 firmware. They are used in the Armada E500 and Armada V300 to support the internal pointing stick or touchpad, an external keyboard, and an external mouse. One of the ports is currently not used.

-

Page 59: Functional Description

UDIO UBSYSTEM The Armada E500 and Armada V300 computers have an internal, industry-standard audio controller, the Maestro 2E from ESS Technology. It supports 16-bit stereo audio, wavetable synthesis, and four-operator FM music synthesis. The Maestro 2E provides all digital sound creation and reproduction tasks and uses an AC97-compatible CODEC, the ES1921, as its interface to the analog world. - Page 60 Signal Processsor Maestro2E Figure 6-1. ESS Maestro 2E Block Diagram used in the Armada E500 and Armada V300 Computers The M2E has a variety of audio interfaces. It has two internal 20-bit AC’97 CODEC interfaces. The secondary AC’97 CODEC interface is used to handle the Docking station CODEC interface.

-

Page 61: Features

The device supports full DOS game compatibility for both PC motherboard and add-in card solutions through three hardware implementations: PC/PCI, Distributed DMA (DDMA), and Transparent DMA (TDMA). While PC/ PCI and DDMA are industry-standard protocols for legacy support, ESS’s TDMA technology implements DOS game compatibility over the standard PCI 2.1 bus. - Page 62 PCI Power Management Interface (PPMI) The PCI Power Management Interface (PPMI) specification establishes the infrastructure required to let the operating system control the power of PCI functions. This is done by defining a standard PCI interface and operations to manage the power of PCI functions on the bus.

-

Page 63: Wavecache

WaveCache The WaveCache dynamically prefetches from the system memory and manages samples for the wave processor (WP). The WaveCache is capable of handling up to 64 separate data streams for the WP. The types of different data streams supported include 16-bit mono, 16-bit stereo, 8-bit mono, 8-bit stereo, and 8-bit differential. -

Page 64: Audio Docking Solution

Audio Docking Solution When docked, the audio output only generates from the docking base. The notebook internal speakers cannot be functional and the audio amplifier is disabled by way of the AUDIO_DOCKED and HP_ON signals. Selecting between input channels from the notebook and the docking station is done by the user through ESS Windows application software. - Page 65 Applications Multimedia PCs 3-D PC Games Music Synthesis Business Audio DVD-ROM/Consumer Video Audio Playback Audio Conferencing Voice Recognition Features Single, high-performance, mixed-signal, 18-bit stereo VLSI chip Meets or exceeds Audio CODEC ’97 revision. 2.1 and Audio CODEC ’97 revision 1.3 analog performance specifications Supports 2-CODEC architecture for notebook and docking station configuration with one ES1921 in each Supports direct Digital Audio mode data out and PCM data in implementing full...

-

Page 66: Functional Description

Functional Description This section shows the overall structure of the ES1921 and discusses its major functional subunits. The major subunits of the ES1921 are shown in Figure 6-2 and described briefly in the following paragraphs. LINE_IN VIDEO MIC1 PREAMP MIC2 PHONE PC_BEEP RESET#... - Page 67 Analog Subsystems PCM out Digital Audio PC BEEP PHONE Bypass MIC1 MIC2 Preamp Select LINE VIDEO Figure 6-3. ESS1921 Mixer Block Diagram Playback Mixer–eight input stereo mixer, shown in Figure 6-3. Each of these inputs except PC_BEEP has 5-bit volume control: PCM out (digital audio from the Maestro Digital Controller) Line in CD audio In...

- Page 68 18-bit stereo ADC -- - AC-Link and the Maestro Digital Controller. 18-bit mono MIC ADC cancellation. Audio is returned to the host through the AC-Link and the Maestro Digital Controller. Record source and input volume control recording. The Mic source can be mixed post-input volume with its own independent input volume control.

-

Page 69: Digital Interface

Digital Audio Mode Digital audio mode, shown in Figure 6-4, is a means of providing digital-ready audio support. The final rendered audio can be routed to multiple locations. In the case of the ES1921, the output of the playback mixer is routed to the ADC and back to the digital controller, where the digital audio can be distributed. - Page 70 The following data streams or slots are used by the ES1921: PCM playback Two-channel composite PCM transmit stream which can be programmed to use two of eight slots PCM double-rate playback Two-channel composite PCM transmit stream which is used for double-rate audio PCM record Two-channel composite PCM receive stream Control...

- Page 71 AC-Link Audio Output Frame (SDATA_OUT) The audio output frame data streams correspond to the multiplexed bundles of all digital output data targeting the ES1921’s DAC inputs and control registers. As was previously discussed, each audio output frame supports up to 12 outgoing 20-bit data time slots. In addition, Slot 0 is a special reserved time slot containing 16 bits.

-

Page 72: Power Management

Power Management The ES1921 is capable of operating at reduced power when no activity is required. The state of power-down is controlled by the power-down control/status register (26h). There are seven separate power states: PR0 through PR6. Figure 6-5 illustrates an example procedure for powering down the ES1921. From normal operation, sequential writes to the power-down control/status register 26h are performed to power down the ES1921 subsection by subsection. -

Page 73: Audio Linear Amplifier Lm4873

Figure 6-6 illustrates a state when all the mixers should work with the static volume settings that are contained in their associated registers. This is used when the user could be playing a CD (or external LINE_IN source) through the ES1921 to the speakers but have most of the system in low-power mode. -

Page 74: General Features

64-bit 2D and 3D graphics acceleration with XGA flat panel and/or CRT displays. The graphics controller used in the Armada E500 and Armada V300 is the ATI Technologies RAGE Mobility-P, with 8 MB and 4 MB of video memory, respectively. -

Page 75: Video Interface

Scaler YUV2 RGB Built-in Self Diagnostics iDCT Engine 2D Engine VGA Graphics Controller Video I/O Interface Figure 7-1. RAGE Mobility-P Graphics Controller used in the Armada E500 and Armada V300 7-2 Video/Graphics Subsystem DISPLAY MEMORY Memory Controller and Interface Display Controller #1... -

Page 76: Bus Interface

The video interface is hardware and register compatible with the VGA standard. This device uses a 2.5-volt video controller core voltage and provides external high resolution video and a variety of LCD panel support. The RAGE Mobility-P supports full SimulScan operation, where the two displays can not only have different resolutions, pixel depths, and refresh rates, but–with proper OS support–different video data. -

Page 77: Flat Panel Support

Flat Panel Support The RAGE Mobility-P can provide support for different flat panels. The Armada E500 supports a 14.1- or 15.1-inch XGA, TFT (1024 × 768) display, using the low voltage differential signaling (LVDS) interface. The Armada V300 supports a 12.1-inch SVGA, STN (800 x 600) CMOS display or a 14.1-inch XGA, TFT (800 x 600) LVDS display. -

Page 78: Tv Out

3D Acceleration The controller has built-in 3D video acceleration, including the following: Integrated 1.2 million triangle per second setup engine 4 KB on-chip texture cache for 3D primitives Complete 3D primitive support–points, lines, triangles, lists, strips, quadrilaterals, and BLTs with Z-compare Full screen or window double buffering Hidden surface removal using 16-bit Z-buffering Edge anti-aliasing... - Page 79 The external TV interface supports the formats listed in Table 7-1. NTSC-M PAL-I Antigua Angola Aruba Botswana Bahamas Gambia Barbados Guinea- Bissau Belize Hong Kong Bermuda Ireland Bolivia Lesotho Burma Malawi Canada Namibia Chile Nigeria Colombia South Africa Costa Rica Tanzania Cuba U.K.

-

Page 80: Simultaneous Scan Mode

Simultaneous Scan Mode The RAGE Mobility-P provides simultaneous display operation with Multisync variable frequency CRT, PS/2 fixed frequency CRT, or TV monitors and SS or DS LCDs. Resolutions, refresh rates and display data can be independent. Scanning is supported in high-resolution modes. - Page 81 Single Display Modes The RAGE Mobility-P supports the video modes illustrated in Table 7-2 when using a single display (LCD or CRT): Single CRT Supported Modes (TFT or DSTN or CRT) dsp wid dsp hgt 1024 1024 1024 1024 1024 1280 1024 1280...

- Page 82 Dual Display Modes The RAGE Mobility-P supports the following video modes when using two displays simultaneously (LCD + CRT), each displaying a different image. Dual Display Modes LCD Resolution 1024 × 768 8 bpp 1024 × 768 16 bpp 1024 × 768 24 bpp 1024 ×...

- Page 83 DVD (MPEG-2) Display Modes The RAGE Mobility-P supports the following video modes when playing back MPEG-2 data in a scalable window, using the built-in motion compensation logic (LCD or CRT): DVD (MPEG-2) Display Modes with Software MPEG Decoding dsp iwid dsp hgt ref(Hz) 1024...

-

Page 84: Video Memory

1024 × 600 Video Memory The video system uses 8 MB (Armada E500) or 4 MB (Armada V300) of 125-MHz SDRAM as graphics memory. The RAGE Mobility-P uses a 64-bit data path to display memory. Display memory control signals are derived from the integrated clock synthesizer’s memory clock. -

Page 85: Motion Video Acceleration

Motion Video Acceleration Hardware DVD decode through integrated motion compensation and iDCT circuitry for full frame rate DVD playback Smooth video scaling and enhanced YUV to RGB color space conversion for full-screen/full-speed video playback Front and back end scalers support multistream video for video conferencing and other applications Enhanced line buffer allows vertical filtering of native MPEG-2 size (720 ×... -

Page 86: Internal Keyboard

The internal keyboard for the Armada E500 and Armada V300 computers consists of a keyboard matrix with a keyboard controller integrated into the MSIO Super I/O Controller, a TouchPad, or stickpoint pointing device (depending on computer model) and select buttons. The computers and optional convenience base have a connector for an external full-sized keyboard and external mouse. -

Page 87: Touchpad Interface

The TouchPad includes a special edge-sensitive feature that allows the user to extend the drag operation when a finger reaches the edge of the sensor pad. The cursor continues to coast in the indicated direction when the finger is held against the edge. The system includes driver and application software that allows the user to configure the pad to: Adjust touch sensitivity from light to heavy... - Page 88 When the PS/2 mouse is powered on, it sends 0xAAh, then 0x00h. The data transmitted by the pointing device to the system consists of the X, Y coordinates of the pointer and status of the buttons. This data is transmitted in a 3-byte serial PS/2 data packet that is compatible with the Microsoft PS/2 mouse.

- Page 89 processed. During a keyboard transmission, the computer system can request a transmission interrupt by lowering KBDCLK. The keyboard checks the state of KBDCLK every 100 microseconds during a transmission. If the line is detected low and the parity bit has been clocked out, the keyboard finishes the transmission.

- Page 90 When the system is ready to transmit a command to the keyboard or mouse, it sets the DATA line low (0). This action serves as both an RTS and a start bit. Upon detecting the KBDDATA line low, the keyboard or mouse sets the KBDCLK line low, causing the start bit to be clocked out of the system.

- Page 91 OWER UPPLY The Armada E500 and Armada V300 computers are designed to operate from multiple power sources, including an internal IBA-2 main battery pack. This requires a flexible power subsystem with advanced power management features. The main components of the power subsystem are: DC/DC converter: generates system voltages of +3.3 volts, +5 volts, and +12 volts,...

-

Page 92: Dc/Dc Converter

The computers have the following Power Management features: Standby modes Local Standby: Selected subassemblies and subsections enter a reduced power mode after prescribed periods of inactivity. Global Standby: All subassemblies enter a reduced power mode and some are powered off. This mode may be activated by system inactivity, a low battery condition, or manually by the operator. -

Page 93: Smart Battery

This cycle can be repeated until an equilibrium is reached, thus keeping within the AC Adapter’s power limit. The Armada E500 and Armada V300 only support the IBA2 battery packs. The battery bay is mechanically keyed to allow only the newer IBA2 packs to be plugged in. -

Page 94: Display Inverter

MBAT (Master Battery) MBAT is a common signal between all of the batteries. This signal is driven active by the power source (either of the two batteries or the AC Adapter) that is powering the system. If the device powering the system is removed MBAT will go inactive. When this occurs any battery in the system will supply power to the system for 4 seconds which will allow the 8051 microcontroller time to assign another battery as master. -

Page 95: Power Management Controller

The adapter simply outputs 19 volts at 50 watts continuous, 60 watts peak (2.8 amps output max). The DC input is a simple two-wire (ground and power) connection, and may be connected to a wide number of sources. Primary support is given to the airline adapter and automotive adapter, but consideration is given that virtually any supply may be connected to the input. - Page 96 PWM signal. A zero percent duty cycle will keep the fan off and a 100 percent duty cycle will run the fan at its full speed. Minimum start up time for the fan is 10 milliseconds. The Armada E500 and Armada V300 incorporate a 35 mm fan.

-

Page 97: Hard Drive Subsystem

4-, 6-, or 12-GB (dependent on model), AT-compatible, 2.5-inch UDMA capable hard drive and a 1.44-MB, 3.5-inch, AT-compatible diskette drive. They support a 24X CD- ROM module and an LS-120 module in the MultiBays. The Armada E500 also supports a 4X DVD-ROM drive module, The preinstalled hard drive contains software that supports PC Cards, IrDA, multimedia, and other system features. -

Page 98: Hard Disk Interface

Hard Disk Interface The hard drive interfaces to the main PCB using the following industry-standard 44-pin connector that interfaces directly to the main PCB, detailed in Table 10-1. Signal Pin # Name Direction HRESET# hard drive7 IN/OUT hard drive8 IN/OUT hard drive6 IN/OUT hard drive9... -

Page 99: Diskette Drive Subsystem

The diskette drive is packaged in a module form for insertion into the Dualbay on the front of the Armada E500. The Armada V300 has a fixed diskette drive in the same location. The diskette controller is software compatible with the Intel 82077 controller and is integrated into the MSIO Super I/O device. -

Page 100: Superdisk Ls-120 Drive Subsystem

SuperDisk LS-120 Drive Subsystem The LS-120 drive option is a bootable device. The drive uses an imbedded ATAPI (IDE) controller for the host interface. The drive is capable of reading and writing to standard SuperDisk LS-120 diskettes, industry-standard 1.44 MB and 720 KB 3.5-inch diskettes and 1.7 MB Distribution Media Formatted diskettes (read only), and 1.2 MB diskettes. - Page 101 chapter This chapter describes the internal Compaq high-speed modems used in the Armada E500 and Armada V300 computers. These computers support the internal combination Compaq 56K (V.90) plus Intel PRO/100+ Mini-PCI Modem or the Compaq Global Mini-PCI 56K (V.90) Modem, both with Lucent Technology chipsets. The modem is CTO configurable and a user upgrade.

- Page 102 The heart of the network interface portion of the card is the Intel 82559. It provides all LAN functions between the mini-PCI Bus and the Ethernet interface magnetics. The PCI configuration register information is stored in a serial EEPROM for host initialization.

- Page 103 IEEE 802.2 LLC SNAP Artisoft Lantastic 7.0, 8.0, Dedicated Server 1.1 Banyan 7.x, 8.5x DEC Pathworks 4.x, 5.x IBM LAN Server version 1.2, 1.3, 2.0, 4.0 Microsoft NT 3.51, NT 4.0, Windows 2000 Novell Netware 3.1x, 4.x, 5.x TCP/IP Novell IPX/SPX and Microsoft compatible Novell IPX ODI Microsoft NetBEUI Sun Microsystems PC-NFS...

- Page 104 The CSP1034 CODEC performs the analog-to-digital and digital-to-analog conversions for the modem line signals and has a digital interface for connection to the 1641 DSP. CODEC features include: High precision sigma delta A/D, D/A converters Support for “real” or “complex” impedance countries Hook relay circuit The DAA contains one relay circuit to handle on/off hook.

- Page 105 V.90 (a-law, mu-law) K56flex (a-law, mu-law) V.8bis V.80 V.42bis, MNP5 V.42 (LAPM, MNP2-4) V.34 (file date: 10/96) Optional symbol rates: 2800, 3429 Asymmetric symbol rates Synchronous primary channel data signaling rates: 33600, 31200 Automatic rate renegotiation 32, 64 state trellis encoding V.32bis V.32 V.23...

- Page 106 The combination modem/NIC card derives its power from either the main PCI +3.3-volt supply or the +3.3 volt AUX supply. A “smart” switch on the card senses the supply source and switches between the two supplies as the host system transitions between a low-power state (S4, S5) and a higher power state (S0 - S3).

- Page 107 The following table maps the ACPI-defined power states (general, system, and device) to the expected platform wake-up capabilities:...

- Page 108 Variances will occur between different computers and between different operating systems. The information below does not apply to all computers that the modem is install. Æ Æ...

- Page 109 When the system is in the working state, G0 (S0), and a communications program is running, the modem will either be in D0 or D2 and is capable of detecting an incoming call. See Table 11-5 for the other states. Note that the modem’s COM port must be open at the time the computer is put into one of the sleep states in order to detect an incoming call.

- Page 110 Boot-on-LAN support relies on PXE code resident in the flash ROM and the boot methods specified above to allow remote administration of the host system. Boot on LAN is determined during BIOS POST. This modem, shown in Figure 11-2, is a controller-less design utilizing the Lucent Technologies Mars2 chipset.

- Page 111 This modem is based on the Lucent 1646 DSP and the 1034C CODEC. The main components of the 1646 DSP are: ROM-coded digital signal processor Two full-duplex bus master streams Internal PLL 24-bit I/O channels 16550 UART (MIMIC) PCI decode logic The data access arrangement (DAA) contains one relay circuit to handle on- or off- hook.

- Page 112 V.42 (LAPM, MNP2-4) V.34 (file date: 10/96) Optional symbol rates: 2800, 3429 Asymmetric symbol rates Synchronous primary channel data signaling rates: 33600, 31200 Automatic rate re-negotiation 32, 64 state trellis encoding V.32bis V.32 V.23 V.22bis V.22 V.21 Bell 212A Bell 103J TIA-578-A (Class 1) T.30 T.4 (Group 3)

-

Page 113: Docking Sequence

OCKING The Compaq Armada E500 computer is compatible with the ArmadaStation EM docking station, Convenience Base, and Port Replicator. The Armada V300 computer docks with the Port Replicator only. Docking Sequence Docking is first detected when the EBOXL# pins (long pins) make contact with the docking station. - Page 114 The Armada Station EM is designed to utilize the Intel MPCI2 PCI to PCI bridge to perform the connecting and disconnection of primary PCI bus. The MPCI2 incorporates a docking state machine that is capable of monitoring system status, controlling electrical isolation, issuing docking event interrupts, and performing motor mechanism controls.

-

Page 115: Power Management States

OWER ONSERVATION The Armada E500 and Armada V300 power conservation features are designed to extend operating time while running in either the normal operating “On” mode or the reduced power “Suspend” (also referred to as “Global Standby” or “System Standby”) mode under either AC power or internal battery power. - Page 116 Suspend–Only those devices required for data retention and integrity receive power. These devices include system DRAM, Video DRAM, 3D RAGE LT Pro Video Controller, all 82443BX power planes, a small part of the PIIX4M, and the MSIO. This mode offers the lowest power consumption available while maintaining the present state in DRAM.

-

Page 117: Processor Power Management

Ring Indicate–The system must be in Standby for this feature to operate. The modem card passes through the modem ring to the RING# pin. The MSIO then wakes up the PIIX4M. RTC Alarm–An alarm causes the IRQ8# from the RTC to assert and wake the PIIX4M. -

Page 118: Processor Thermal Management

Off and S3 Suspend modes. PCI Bus Power Management The Armada E500 and Armada V300 computers use the method defined in the PCI 2.1 specification to reduce the power used by the PCI bus. This method uses a PCI signal called CLKRUN# to stop the PCI clock when no PCI activity is occurring. -

Page 119: Video Power Management

Video Power Management The RAGE Mobility-P graphics controller has several internal timers that monitor subsystems within the video controller. When one of these areas becomes inactive for a long period of time, the controller disables that area, saving overall system power. RAGE Mobility-P power management logic supports four device power states: On, Standby, Suspend, and Off. -

Page 120: External Ports/Connectors

Lucent 1641 DSP, 11-3 Lucent CSP1034 CODEC, 11-4 modem sleep state transitions, 11-8 power management, 11-6 combo modem/NIC card, 11-1 Compaq Armada E500 Personal Computer block diagram, 1-5 computer setup, B-1 CPU, 1-1, 1-6 CRT, 7-4 DC/DC controller, 9-2 DC/DC converter, 9-1, 9-2... -

Page 121: Mechanical

Flash Disaster Recovery mode, 5-4 flash ROM, 2-15 interface, 5-7 interface block diagram, 5-7 fuel gauge, 9-4 functional interrupts, 4-6, 4-7 Global Standby, 9-2 GPI signals, 2-12 GPO signals, 2-12 graphics controller, 7-1 HDD, B-2 HDD interface, 10-2 Hibernation, 9-2 hot keys, 8-2 IDE controller, 2-8 infrared controller, 5-6... - Page 122 Off, B-2 On, B-2, B-3 parallel PCI interrupts, 4-10 parallel port, 5-5 parallel port multiplexor, 5-5 PC Card CardBus interface, 4-1 controller, 4-1 hot insertion and removal, interface, 4-1, 4-3 interrupts, 4-7 PCI1225, 4-1, 4-3 PC Card interrupts, 4-6 master devices, 2-6 power management states, slot assignments, 2-6 PCI bus, 1-6, 2-6...

- Page 123 advanced power management, 1-8 clock interface, 2-10 features, 1-7 GPI signals, 2-12 GPO signals, 2-12 ISA bus interface, 2-11 PIIX4E, 2-2, 2-10 power management, 2-11 power planes, 2-10 reset interface, 2-10 ROM, 2-15 Super I/O (MSIO), 2-16 system interrupts, 2-14 System Management Mode (SMM), 2-10 SPKROUT signal, 4-5...